数字IC前端学习笔记:异步复位,同步释放

相关阅读

数字IC前端![]() https://blog.csdn.net/weixin_45791458/category_12173698.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12173698.html?spm=1001.2014.3001.5482

异步复位

异步复位是一种常见的复位方式,可以使电路进入一个可知的状态。但是不正确地使用异步复位会导致出现意想不到的错误,复位释放便是其中的一个重要问题,这将在后面进行讨论。

异步复位是通过寄存器的异步复位端实现的,复位端一般是低电平有效,即当复位端为低电平时,寄存器输出被强制复位。

代码风格

下面的代码显示了如何在Verilog代码中说明带有复位的寄存器。注意到复位信号的下降沿事件被加入了敏感列表。其实,异步复位是根据电平生效的,即当复位信号为低时复位。在这里写成下降沿的形式是因为,综合工具要求敏感列表中出现的信号如果有一个是边沿事件,则其他所有事件也必须是边沿敏感的,但这对于仿真工具是可以接受的,甚至仿真工具还可以在敏感列表中存在除了复位沿和时钟沿以外的其他信号事件,这对于综合工具也是不可接受的。

//综合与仿真工具都支持

module FlipFlop(input clk, rst_n, d, output reg q);

always@(posedge clk, negedge rst_n)begin

if(!rst_n)

q <= 1'b0;

else

q <= d;

end

endmodule

//综合工具不支持与仿真工具支持,其实复位效果和上面的代码一致(不要使用它)

module FlipFlop(input clk, rst_n, d, output reg q);

always@(posedge clk, rst_n)begin

if(!rst_n)

q <= 1'b0;

else

q <= d;

end

endmodule

//一个奇怪的例子,但仿真工具确实支持(不要使用它)

module FlipFlop(input clk, rst_n, d, output reg q);

always@(posedge clk, rst_n, d)begin

if(!rst_n)

q <= 1'b0;

else

q <= d;

end

endmodule异步复位的优势

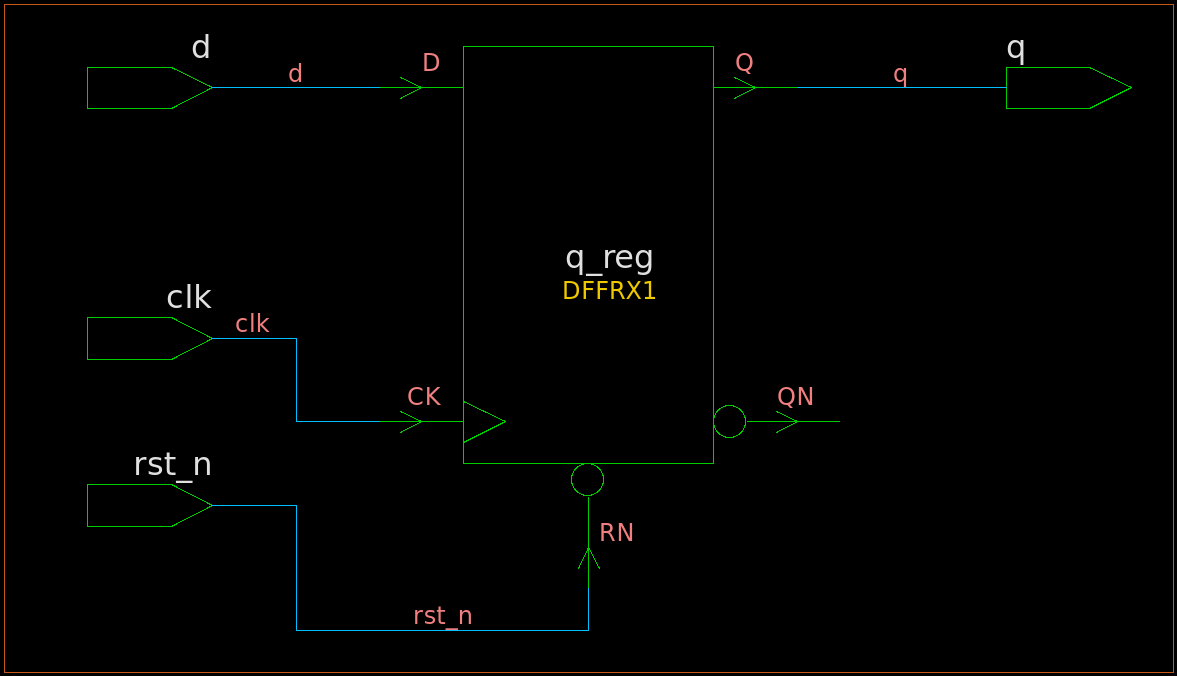

在进入这个话题前,我们先来看一下上面的第一段代码综合出的电路,如图1所示。可以看到综合工具可以直接从异步复位的Verilog描述中推断出一个带异步复位端的寄存器。

图1 异步复位综合出的寄存器

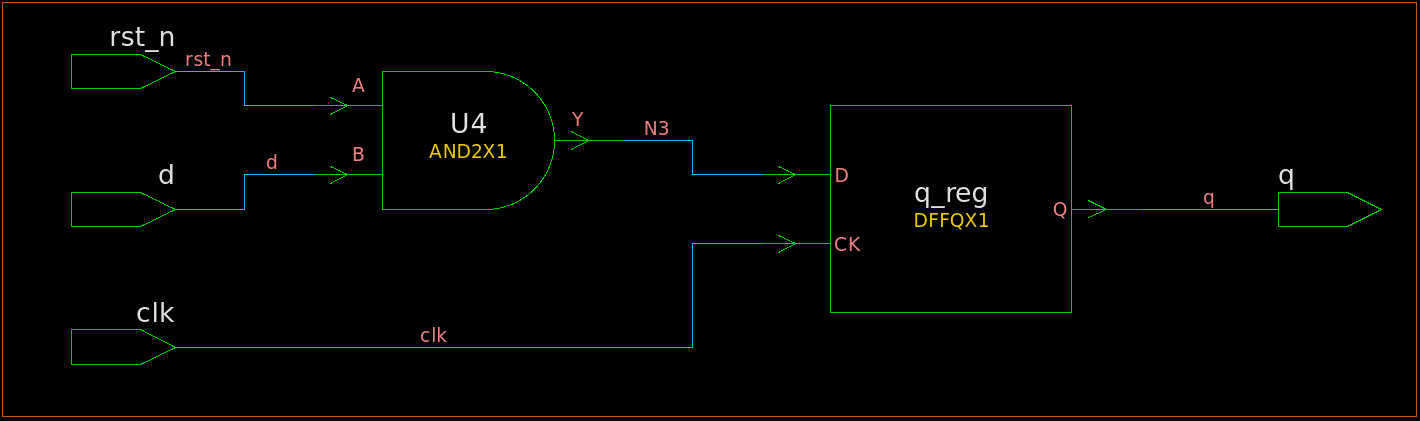

我们再来看一下同步复位综合出的电路,如图2所示。顺便一提,上面异步复位的代码可以很轻松地改变为同步复位,只要把posedge rst_n从敏感列表中去除即可,如下所示。综合结果显示,异步复位其实就是将异步复位信号当做寄存器输入的一部分,而不是综合出一个有同步复位端的寄存器。对于那些时序上比较紧张的设计,在寄存器前的组合逻辑再插入异步复位的逻辑无法承受,使用异步复位能保证不会给reg2reg的时序路径带来负面影响。异步复位的另一个优点是无需时钟存在便可复位,这使得在时钟尚未启动时复位电路成为了可能。

//同步复位

module FlipFlop(input clk, rst_n, d, output reg q);

always@(posedge clk)begin

if(!rst_n)

q <= 1'b0;

else

q <= d;

end

endmodule

图2 同步复位综合出的寄存器

异步复位的问题

异步复位中也存在一定问题,因为复位信号的使能和释放都是异步的。不正确的复位释放,即复位沿过于接近时钟沿会导致寄存器输出现亚稳态(复位的生效不会导致出现亚稳态,因为复位是强制将输出拉低)。其实同步复位也有相似的问题,因为同步复位信号需要像其他输入信号一样满足建立时间、保持时间的要求,否则会在寄存器输出产生亚稳态。

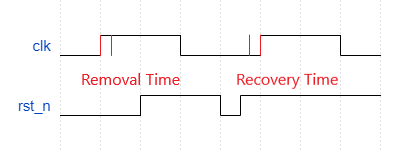

Removal时间和Recovery时间

与建立时间和保持时间类似,removal时间和recovery时间被用来描述复位信号的时序要求。如图3所示,removal时间指的是复位释放不能过于靠近时钟有效沿的后方,而Recovery指的是复位释放不能过于靠近有效沿的前方。这两种条件都可能造成输出的亚稳态,因为复位相当于内部信号的改变,这种改变过于靠近时钟沿会导致电路逻辑状态不定。

图3 复位信号释放的要求

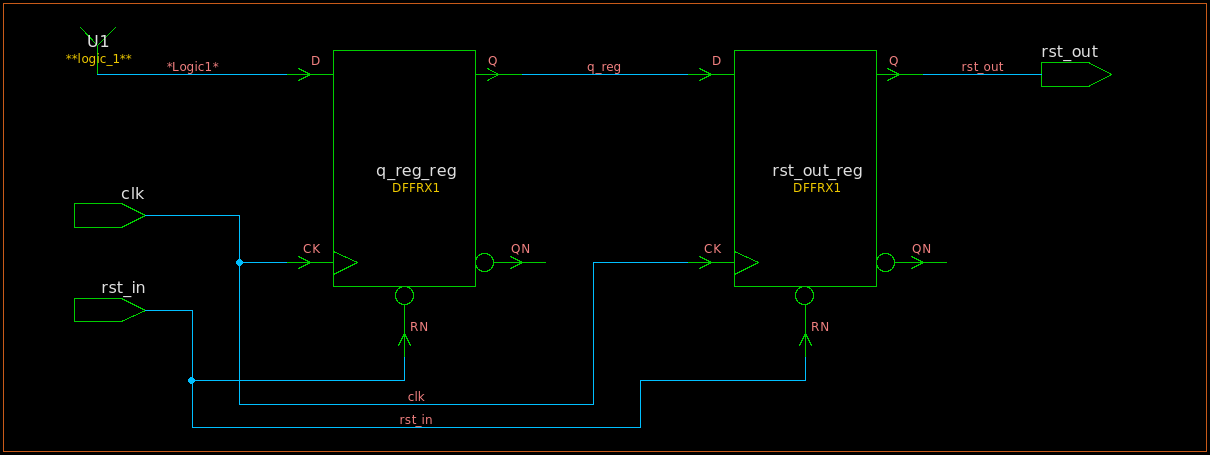

复位同步器

就像CDC(跨时钟域)问题一样,复位信号的释放同样也可以使用同步器与时钟沿进行同步,这就是“异步复位,同步释放”。

以上结构的Verilog描述如下所示。

module reset_syn(input clk, rst_in, output reg rst_out);

reg rst_r;

always@(posedge clk, negedge rst_in)begin

if(!rst_n)

{rst_out, rst_r} <= 2'b0;

else

{rst_out, rst_r} <= {rst_r, 1'b1};

end

endmodule在同步了复位释放信号后,第一个寄存器的输出依然可能出现亚稳态,但这个不确定状态在传播到第二个寄存器输入前已经稳定(可能是1,也可能是0),即下一个时钟边沿在第二个寄存器输出不会出现亚稳态,这也意味着同步后复位释放信号会延迟输入的复位释放信号1至2个周期。

甚至为了保险起见还可以使复位再延迟一段时间再释放,这样可以在最大程度上确保复位正常释放,如下所示。

`define count 16'hffff

module reset_syn(input clk, rst_in, output reg rst_out);

reg rst_r, rst_cnt, rst_pre;

always@(posedge clk, negedge rst_in)begin

if(!rst_in)

{rst_pre, rst_r} <= 2'b0;

else

{rst_pre, rst_r} <= {rst_r, 1'b1};

end

always@(posedge clk, negedge rst_pre)begin

if(!rst_pre)

rst_cnt <= 0;

else if(rst_cnt < `count)

rst_cnt = rst_cnt + 1;

end

always@(posedge clk, negedge rst_pre)begin

if(!rst_pre)

rst_out <= 0;

else if(rst_cnt == `count)

rst_out <= 1'b1;

else

rst_out <= 1'b0;

end

endmodule