【USRP】5G / 6G 原型系统 5g / 6G prototype system

面向5G/6G科研应用

USRP专门用于5G/6G产品的原型开发与验证。该系统可以在实验室搭建一个真实的5G 网络,基于开源的代码,专为科研用户设计。

软件无线电架构,构建真实5G移动通信系统

X410 采用了目前流行的异构式系统,融合了FPGA、ARM、GPU和x86多种处理器,支持单独升级和扩展,为算法评估提供强大算力支持。

高性能与灵活性的完美平衡

支持流行的开源5G项目,也可以运行商业5G协议栈,可用于搭建工业5G专网,实现云化管理。L1/L2/L3都可以二次编程,能支持FPGA级别的硬件编程和开发,充分发挥开发人员的主动性和创造力。

真正可编程移动通信系统

支持5G FR1频段,可以通过扩展组件,支持FR2(毫米波)频段,适用于6G平台开发,同时也兼容2G/3G/4G通信系统。如果需要覆盖距离元,也可以配合外部功放模块。

硬件平台

可编程射频单元 X410

NI Ettus USRP X410 是一款高性能、多通道软件定义无线电。 SDR 设计用于 1 MHz 至 7.2 GHz 的频率,可调至 8 GHz,采用两级超外差架构,具有 4 个独立的 TX 和 RX 通道,每个通道的瞬时带宽为 400 MHz。 用于数据卸载和控制的数字接口包括两个支持 100 GbE 的 QSFP28 接口、一个 PCIe Gen3 x8 [1] 接口以及标准命令、控制和调试接口:USB-C JTAG、USB-C 控制台、以太网 10/100 /1000。 USRP X410 是一款基于 Xilinx Zynq Ultrascale+ ZU28DR 射频片上系统 (RFSoC) 构建的一体化器件,具有内置数字上下转换和板载软决策前向纠错 (SD-FEC) IP。

使用您选择的软件

NI Ettus USRP X410 完全支持流行的开源 USRP 硬件驱动程序 (UHD) 版本 4.1 或更高版本[2]。 UHD 4.1 旨在支持 400 MHz 带宽和板载多个通道所带来的大数据移动要求。 USRP X410 支持开源 SDR 设计流程,例如 C/C++ 和 GNU Radio 以及 LabVIEW FPGA [1]。 与其他基于 RFSoC 的系统不同,USRP X410 已完全准备好移植您以前的 UHD 设计,以便通过简单的重新编译来利用高性能功能。

联网/单机运行

由于 USRP X410 基于 ZU28DR 射频片上系统 (RFSoC) 器件构建,因此它配备了四核 ARM Cortex-A53 处理子系统,主频高达 1.2 GHz,可满足独立应用要求。 此外,RFSoC 还包含一个双核 ARM Cortex-R5 实时处理单元,用于板载监控。

内置IP

USRP X410 上的板载 RFSoC 包含的 FPGA 可编程逻辑资源是上一代 X 系列 USRP 器件的两倍多。 此外,ZU28DR还配备8个软判决前向纠错(SD-FEC)硬IP核,非常适合无线通信系统。 鉴于 RFSoC 内置 ADC 和 DAC 的高速特性,Zynq 器件具有 8 个数字上变频和数字下变频 IP 内核,可实现快速带内重新调谐或信号减弱。

多电台同步

通过内置 GPSDO(GPS 规范振荡器)或 10 MHz 参考和 1 PPS(每秒脉冲)输入信号接口,可以实现多无线电时钟和定时同步操作。 不支持多无线电相位对齐和相位相干操作,因为 USRP X410 不支持 RF 链 LO 导入和导出功能。

5G NR 信号调理模块

SC2430 NR 信号调理模块 (SCM) 是一款前端解决方案,可为软件定义无线电 (SDR) 系统提供信号调理和放大。它专为与 NI Ettus-USRP X410 结合使用而设计。在此配置中,其输入和输出无线电特性符合 5G NR 用户设备 (UE) 和 gNodeB (gNB) 实施的精选 3GPP 5G/NR 标准。

典型应用

- 5G NR FR1 开发

- 软件定义无线电应用

- 先进无线通信研究

- 大批量生产测试和测量

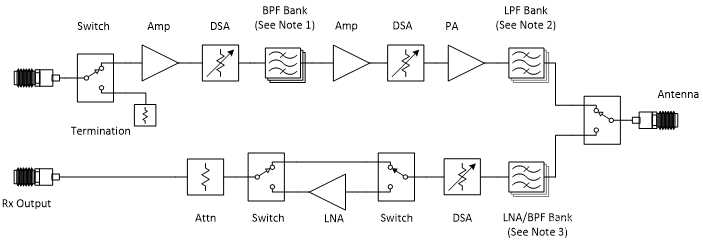

SC2430 SCM 包含两个前端 (FE) 模块。每个模块在时分双工 (TDD) 配置中包含两对独立的发送 (Tx) 和接收 (Rx) 通道。对于需要频分双工 (FDD) 操作的应用,可以将一个无线电通道配置为连续发送路径,将第二个无线电通道配置为连续接收路径。

综上所述,SC2430可以同时支持4个TDD或2个FDD通道。

这些通道在 Tx 和 Rx 路径中包含信号调理和放大模块,与多个 5G NR 频段(n34、n38、n39、n40、n41、n46、n47、n48、n77、n78、n79、n90 和 n96 )。此外,旁路路径可用于在这些频段之外运行的应用程序。

通过 8 个 SMA 连接器建立与 SDR 的射频连接。Tx 和 Rx 端口采用交流耦合,支持 350 MHz 至 7.125 GHz 范围内的信号。这些通道提供 100 MHz(350 MHz 至 600 MHz)、200 MHz(600 MHz 至 800 MHz)和 400 MHz(800 MHz 至 7.125 GHz)的瞬时带宽 (IBW)。

传输路径可在 1.9 GHz 下产生 34 dB 增益,在 3.5 GHz 下产生 30 dB 增益。峰值输出功率 (P1dB) 约为 27 dBm,三阶截取点 (OIP3) 为 41 dBm。在最大增益下,所有频率下的噪声系数通常为 8 dB 或更好。带通滤波可提供超过 50 dB 的带外抑制。

在接收路径中,1.9 GHz 时可获得 27 dB 增益,3.5 GHz 时可获得 23 dB 增益。噪声系数范围为 4 dB (1.9 GHz) 至 7 dB (3.5 GHz)。输入三阶压缩点为-5 dBm (1.9 GHz) 至-1 dBm (3.5 GHz)。该装置可承受最大+10 dBm 的无损坏输入功率。设计中融入了两组 5G NR 特定频带滤波器,可提供超过 50 dB 的带外抑制。

控制接口是用户访问以配置和编程 SCM 的数字端口。有两种控制选项可供选择。

第一个是基于 SPI 的接口,与前面板 HDMI 连接器上提供的其他 GPIO 相结合。SPI 信号存在于引脚 1、4、6、7 和 9 上。其余引脚用于 GND、自动发送/接收或 ATR(引脚 10、12)以及衰减器锁存(13、15)。提供 ATR 和锁存引脚是为了促进 5G 规范中定义的高速 TDD 操作。SPI 端口可以在 40 MHz 的写入频率和 16 MHz 的读取时钟频率下运行。

NI Ettus-USRP X410 SDR 的用户可能更喜欢这种控制选项。与其他 USRP 兼容硬件一样,SC2430 可以设置为 UHD 设备并通过 X410 进行控制。SC2430 驱动程序与 UHD 扩展框架兼容。当启用 SC2430 扩展时,X410 配置将包括 SCM 性能。例如,设置 X410 增益将导致 X410 和 SCM 增益设置最适合当前操作条件。

标准 HDMI 电缆可用于互连。另外,SCT 还提供短的机械锁定电缆。这些电缆包含扼流圈以最大限度地减少排放。为每个模块提供单独的接口。

第二个控制选项允许用户通过机箱后部 USB-C 连接器上的 UART 控制台接口访问 SC2430。现场固件更新期间需要 USB 端口。

SCT 网站的支持页面上提供了完整的 API 规范:https://www.signalcraft.com/support。

外部电源输入需要 12 V DC、16 A 电源。SC2430 附带通用交流/直流电源块。如果需要高密度或机架安装操作,则可以使用其他兼容电源。SC2430 可通过前面板按钮开机,或设置为在施加 12 伏输入时自动启动。前面板按钮还可用作 SC2430 电源状态的指示器。

在前面板上,SC2430 每个通道配备一个 LED 来指示其状态(发送或接收)。

单射频通道(总共 4 个可用通道)

协议栈开发平台 超高性能服务器

用于开发5G系统的基站功能,包括物理层和协议栈等。可以预装开源的OAI参考设计,也支持第三方或者用户自己开发的协议栈。处理单元采用Intel酷睿i9多核处理器,支持FPGA实现协议栈加速。

高性能

- 应对高性能和关键任务系统最多支持 8个Intel® Xeon®处理器7500系列

- 高带宽和低延时实现了高性能

高可扩展性

- 从1个开始可扩展至 8CPU (64 核心/128线程)

- 最多128个DIMM插槽 (最多2TB内存使用16GB DIMM)

- 最多14个 PCI-Express Gen2插槽

高可靠性

- “无缝架构”, 直接连接CPU,减少部件数量,降低故障率

- 通过冗余部件和在线维护功能(fan, PSU, and HDD)最小化宕机时间

- 内置服务处理器与NEC的BIOS以及Intel的机器校验架构(MCA)恢复功能配合作用,简化服务器资源管理

- 通过使用BID快速确定错误部分,在UNIX 服务器上最小化恢复时间

节能

- 使用轻型材质,减轻14%重量

- 高效的PSU认证 80 PLUS 金牌认证电源

- 通过使用电力消耗管理最先进技术,降低运行成本

核心网开发平台 普通性能服务器

开发平台基于高性能Intel多核处理器,支持万兆网口与协议开发平台互联,预装开源的5G核心网,提供 AMF、SMF、AUSF、UDM、UPF 等功能单元。平台支持第三方或者客户自己的核心网,也可以根据需要,用于边缘计算或者作为应用服务器实现业务组件集成。

性能

• 支持四颗全系列英特尔 至强 可扩展处理器,单CPU最高支持28个计算核心

• 支持48条DDR4内存,内存速度最高达2666MT/s,内存容量可达6TB

• 智能内存巡检,内存故障率降低95%

• 支持6个热插拔存储设备,支持多种存储配置模式,可以支持RAID6

• 支持配置4块PCIe NVMe SSD 盘+2块M.2硬盘

• 智能硬盘巡检,故障预警保护数据安全

• 支持8个PCI-E槽位

管理

• 自动监控模块,实时监控固件信息

• 自动部署模块,自动发现并纳管基础设施

• 自动生命周期管理模块,固件/驱动一键升级

• 支持OS批量安装,每台平均耗时缩短到分钟级

• 支持错峰上电功能

• 裸金属虚拟化,对服务器实现配置采集、镜像制作、镜像分发等功能,自动实现服务器裸金属虚拟化

• 智能日志分析,分析系统日志,智能优先级排序,主动上传上级运维系统

开源5G项目(Open Air Interface 5G)

随着第五代通信技术迅速发展,基于5G的应用以及学术研究需求逐渐增大,对于开源5G的研讨迫在眉睫。开源5G平台可用于探索5G领域新技术、新趋势,对下一代核心网、新型智能终端、mIoT、NB-IoT等领域进行深入学术研究与工程实践,促进5G的全球化发展。

基于开源5G无线技术和实验环境的部署,系统原型和标准化硬件实现,可以作为接入网早期测试与验证工具,支持下一代核心网新型智能终端的研发。

USRP 5G研发平台预装开源的5G协议Open Air Interface 5G(OAI),支持新的版本移植和运行。平台可以为OAI提供稳定运行经过验证的软硬件环境,也可以根据需求定制软件和硬件来满足科研项目需求。

一般参数

· 静态时分双工

· FDD正常CP

· 30 kHz 子载波间隔

· 带宽高达 80MHz(217 个物理资源块)

· 与 IF 设备接口的中间下行链路和上行链路频率

· 单天线端口(单波束)

· 时隙格式:上行或下行 14 个 OFDM 符号

· 高效的3GPP兼容LDPC编码器和解码器(支持BG1和BG2)

· 符合3GPP标准的高效极性编码器和解码器

· 短块的编码器和解码器

gNB 物理层

· FR1 为 30KHz SCS,FR2 为 120 KHz SCS

· NR-PSS/NR-SSS的生成

· NR-PBCH支持多个SSB和灵活的周期

· SIB1的NR-PDCCH的生成(包括DCI的生成、极性编码、加扰、调制、RB映射等)

· MIB配置的公共搜索空间

· RRC配置的用户特定搜索空间

· DCI格式:00、10(集成中的01和11)

· NR-PDSCH的生成(包括分段、LDPC编码、速率匹配、加扰、调制、RB映射等)。

· 单符号 DMRS、DMRS-TypeA-Position Pos2、DMRS 配置类型 1

· PDSCH映射类型A

· NR-CSI PHY 序列生成(集成中)

· NR-PUSCH(包括分段、LDPC编码、速率匹配、加扰、调制、RB映射等)。

· NR-PUCCH

· 格式0(2位,主要用于ACK/NACK)

· 格式2(最高64位,主要用于CSI反馈)

· NR-PRACH 格式 0,1,2,3, A1-A3, B1-B3

· 高效的3GPP兼容LDPC编码器和解码器(支持BG1和BG2)

· 符合3GPP标准的高效极性编码器和解码器

· 短块编码器和解码器

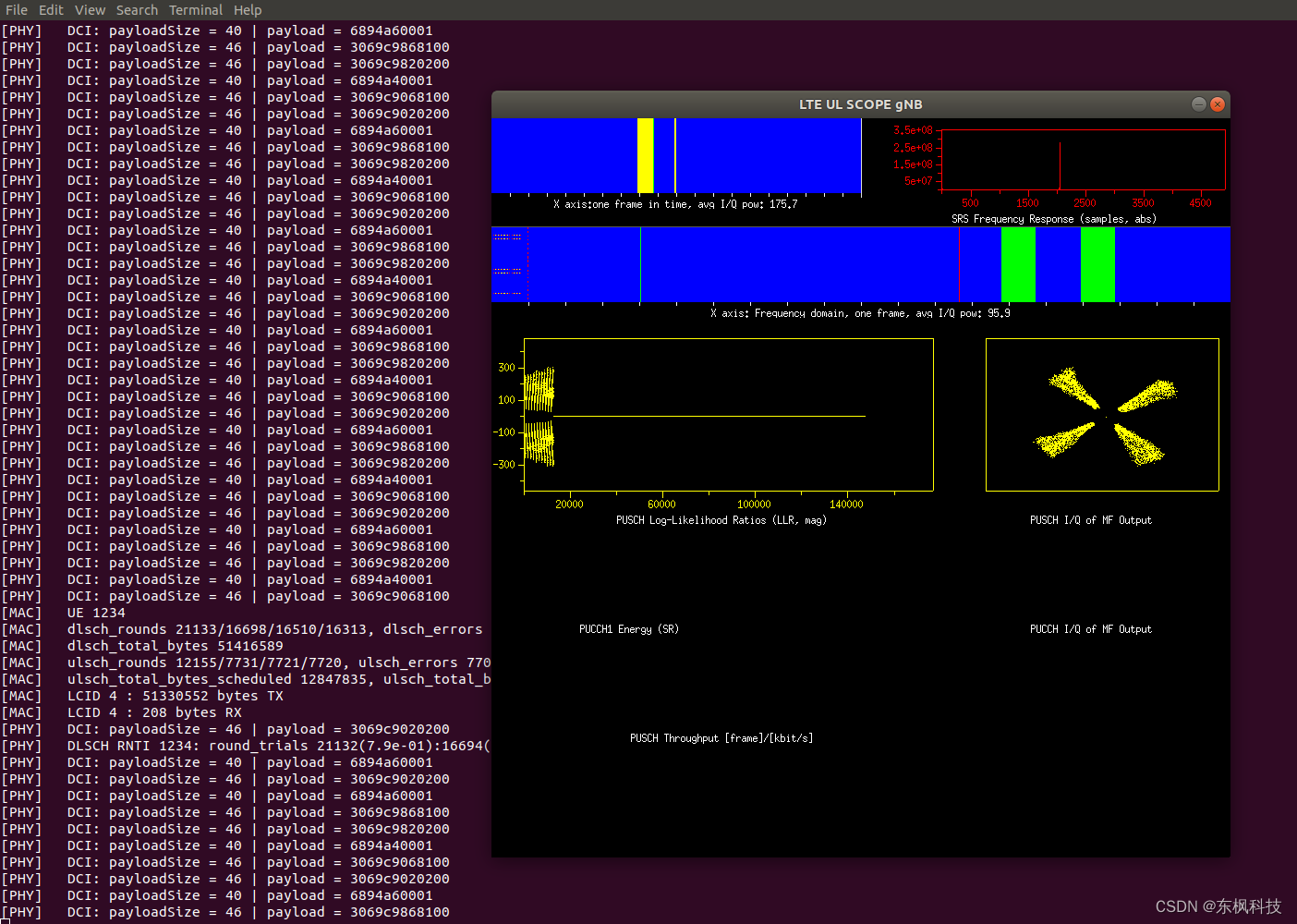

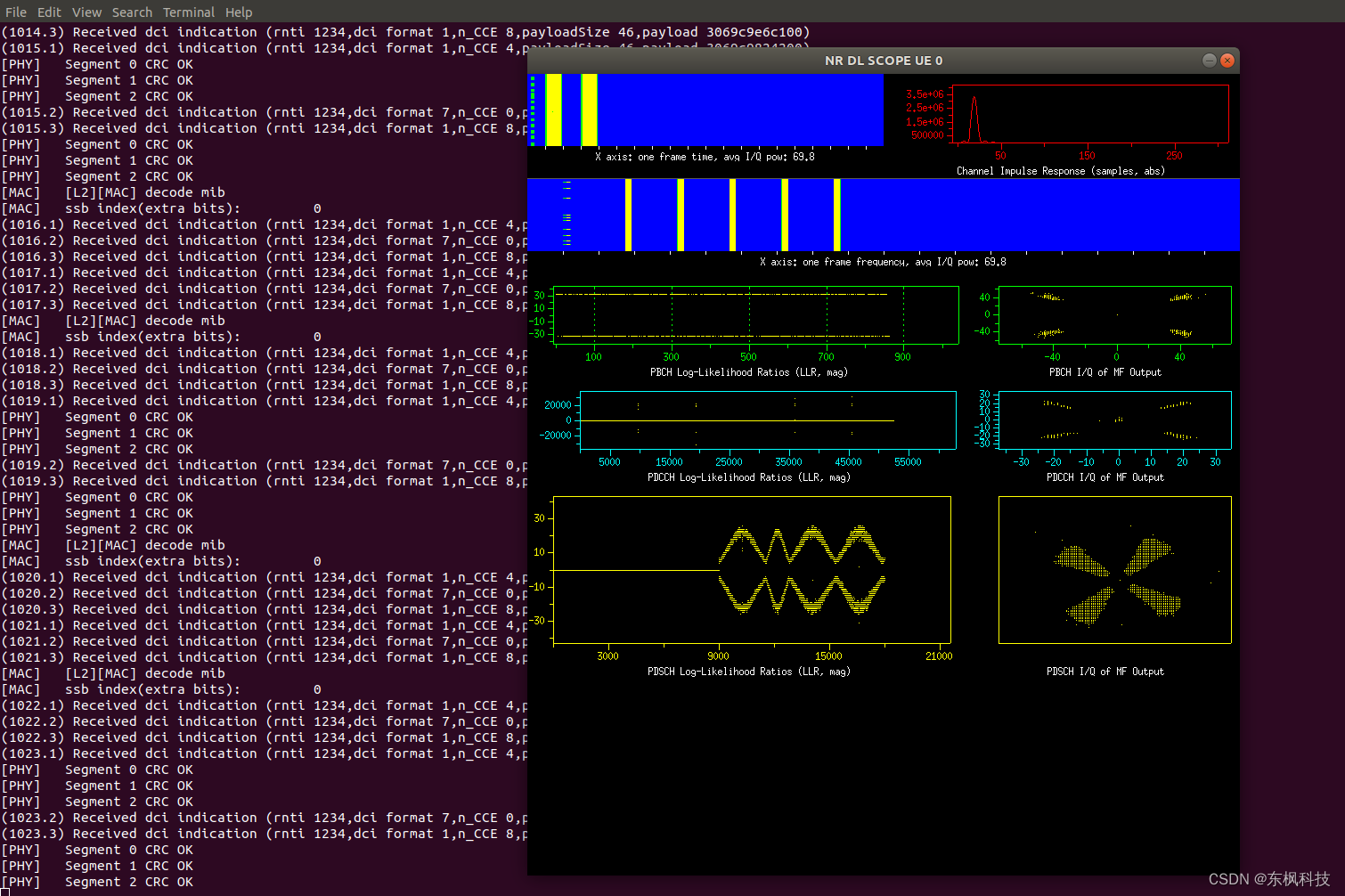

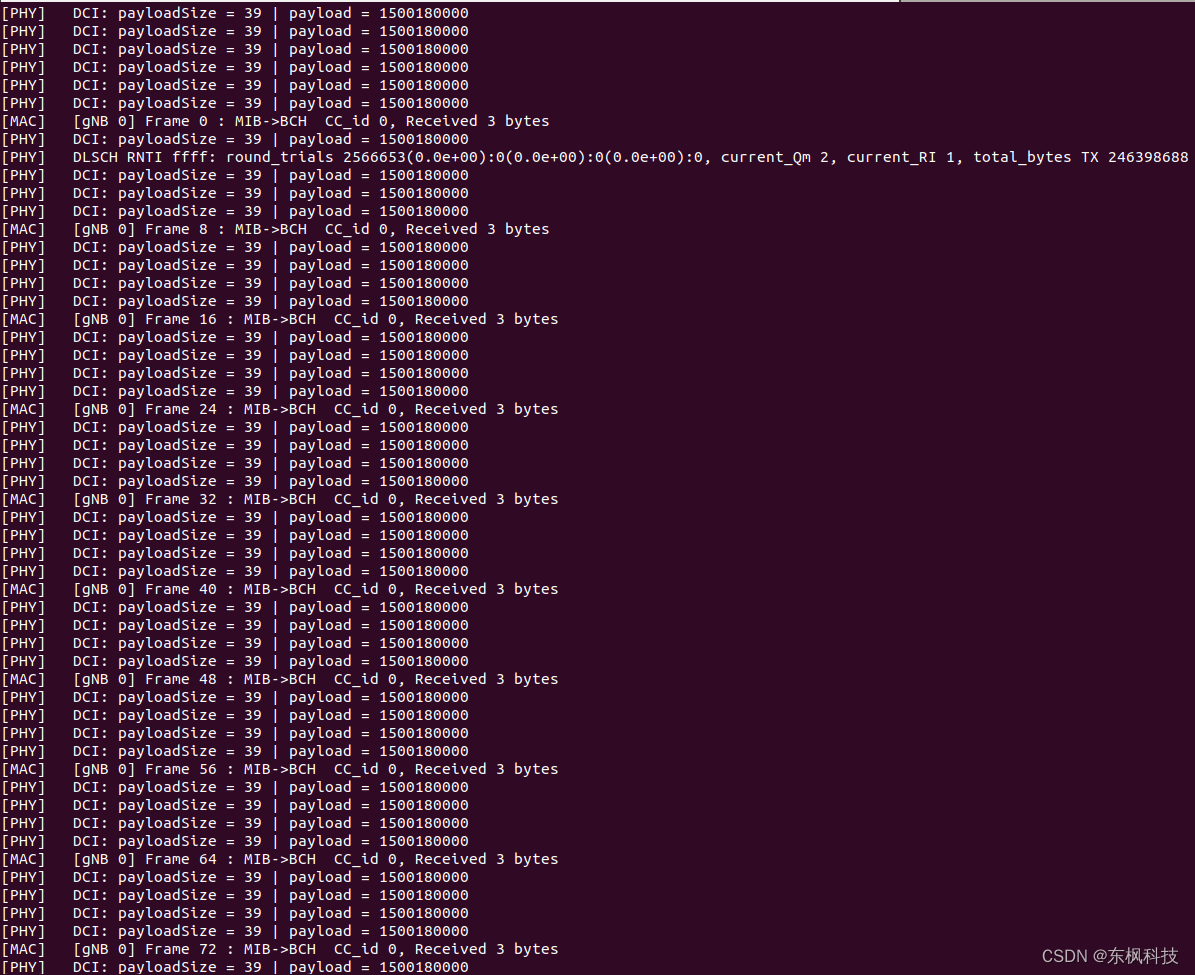

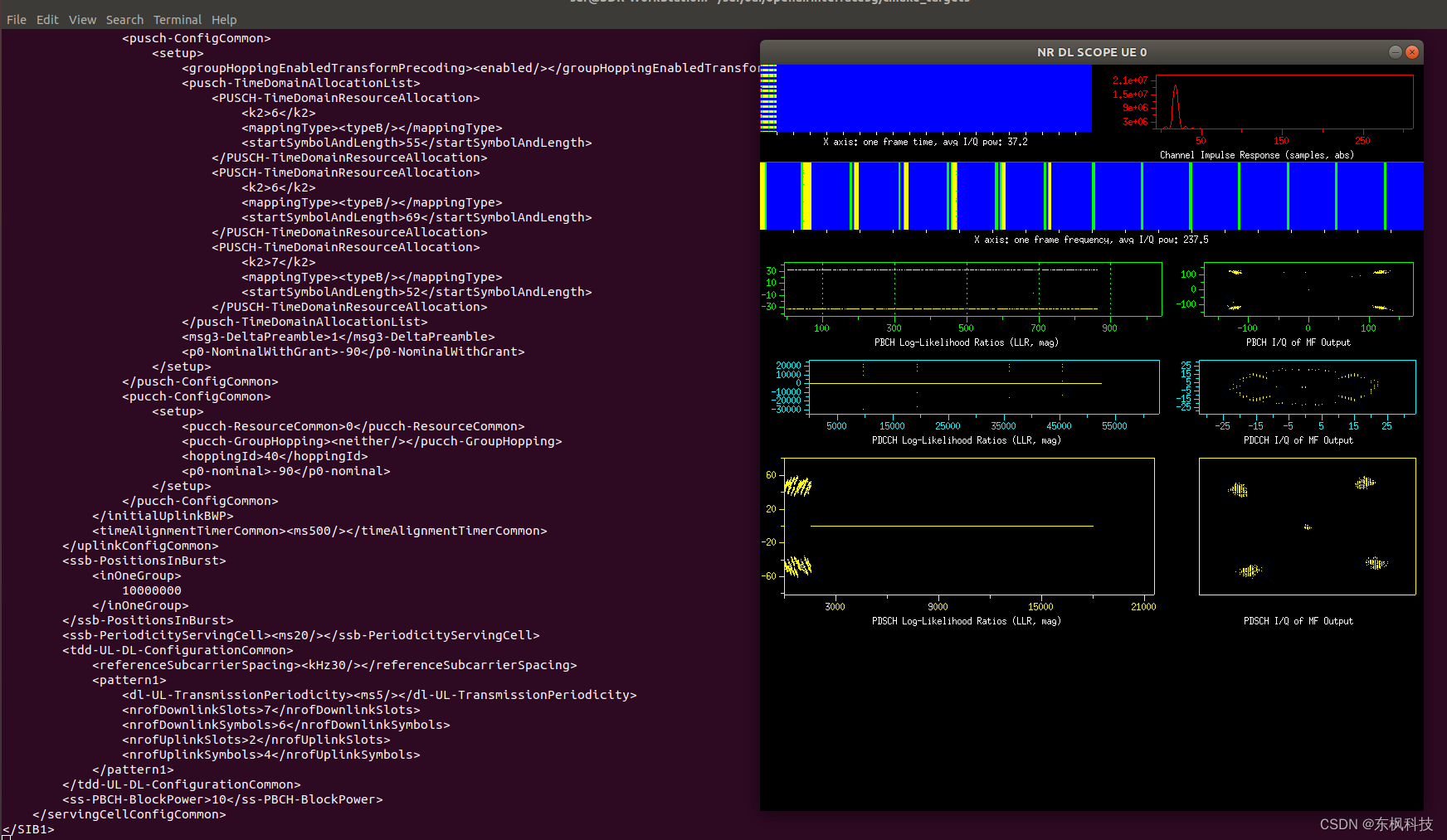

运行效果

5GNR PHY Test–5GNR gNB运行界面

5GNR PHY Test–5GNR UE运行界面

5GNR SA Mode–gNB运行界面

5GNR SA Mode–UE运行界面

频率查询表

| NR | Band Frequency |

|---|---|

| n34 | 2010 MHz – 2025 MHz |

| n38 | 2570 MHz – 2620 MHz |

| n39 | 1880 MHz – 1920 MHz |

| n40 | 2300 MHz – 2400 MHz |

| n41 | 2496 MHz – 2690 MHz |

| n46 | 5150 MHz – 5925 MHz |

| n47 | 5855 MHz – 5925 MHz |

| n48 | 3550 MHz – 3700 MHz |

| n77 | 3300 MHz – 4200 MHz |

| n78 | 3300 MHz – 3800 MHz |

| n79 | 4400 MHz – 5000 MHz |

| n90 | 2496 MHz – 2690 MHz |

| n96 | 5925 MHz – 7125 MHz |

Zynq UltraScale+ RFSoC

射频模拟集成

将直接射频采样数据转换器单片集成到自适应 SoC 上,无需外部数据转换器,从而实现灵活的解决方案,与多组件解决方案相比,功耗和占用空间减少高达 50%,包括消除高耗电的组件FPGA 至模拟接口,例如 JESD204。这种方法还实现了高度灵活的解决方案,将大部分射频信号处理转移到数字域。

标清前向纠错

Zynq™ UltraScale+™ RFSoC 集成了具有低密度奇偶校验检查 (LDPC) 和 Turbo 编解码器支持的软决策前向纠错核心 (SD-FEC) IP 模块。与软逻辑实现相比,硬化核心可在低延迟下提供超过 1Gb/s 的性能,并且功耗更低、面积更小。

硬化数字前端

Zynq RFSoC DFE 是最新的自适应 RFSoC 平台,它集成了比软逻辑更多的硬化 IP,用于关键的 DFE 处理。Zynq RFSoC DFE 为 5G 新无线电提供灵活的解决方案,输入/输出频率高达 7.125GHz,具有高功效和成本效益。

硬件适应性

Zynq UltraScale+ RFSoC 架构集成了 FPGA 结构,可利用相同的基础硬件灵活地满足各种要求。利用同一平台来满足不同需求和新兴标准的能力使供应商能够对新的市场机会做出快速反应。

用于单芯片无线电的完整 SoC

作为一种异构计算架构,包括完整的 Arm 处理子系统、FPGA 结构以及整个 RF 信号链的完整模拟/数字可编程性,Zynq UltraScale+ RFSoC 为各种应用提供了完整的单芯片软件定义无线电平台,并且能够随着市场动态的发展产生无线电变体。

Zynq UltraScale+ RFSoC 产品组合