EMC学习笔记(二十四)降低EMI的PCB设计指南(四)

降低EMI的PCB设计指南(四)

- 1.电路板分区

- 2.信号走线

- 2.1 电容和电感串扰

- 2.2 天线

- 2.3 端接和传输线

- 2.4输入端的阻抗匹配

tips:资料主要来自网络,仅供学习使用。

1.电路板分区

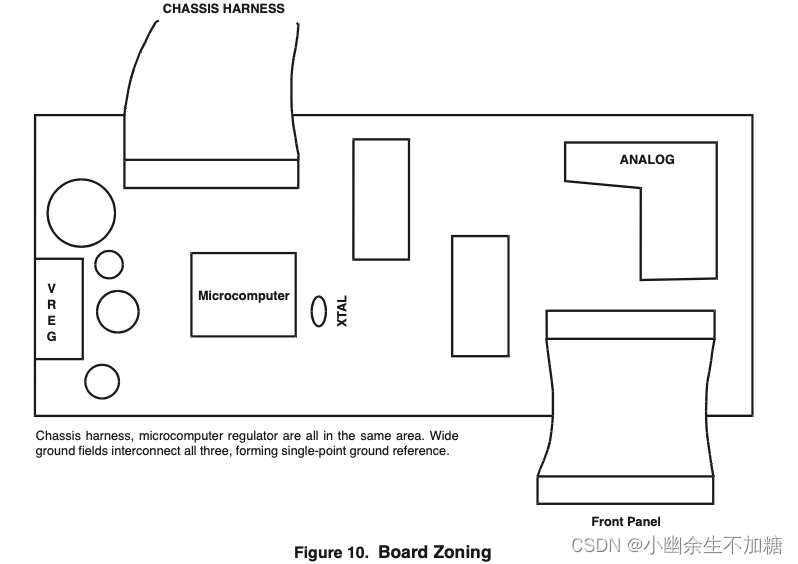

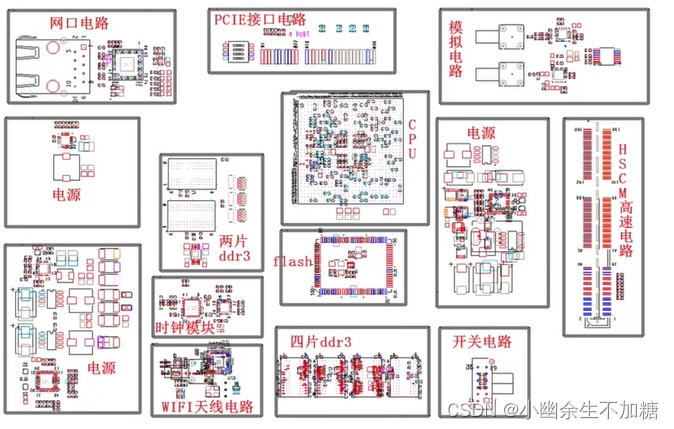

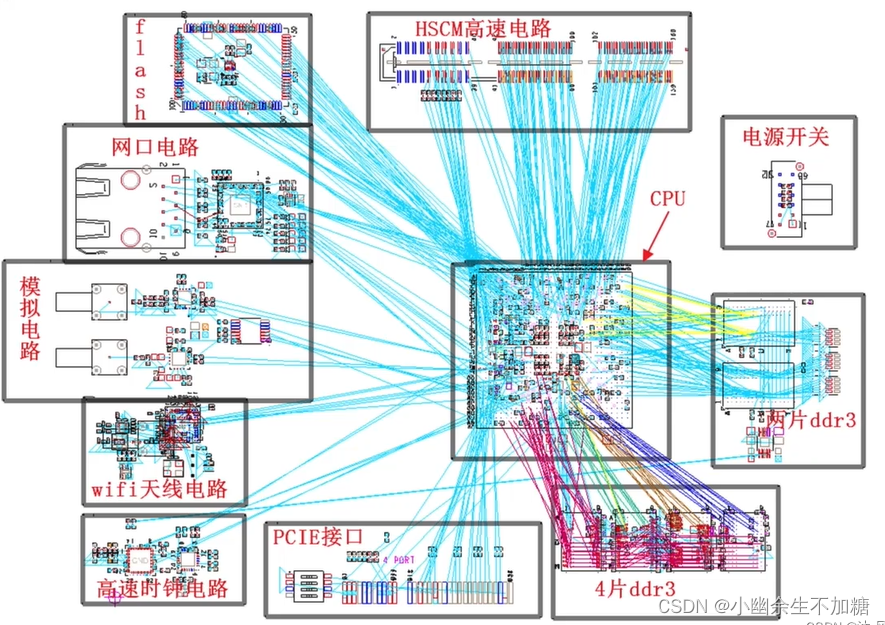

电路板分区与电路板平面规划具有相同的基本含义,后者是在绘制任何走线之前定义空白PCB上元件的大致位置的过程。更进一步,它包括将相似的功能放置在同一区域上,而不是混合在一起。(见图)。

包括微处理器在内的高速逻辑器件被放置在靠近电源的地方,而速度较慢的器件则被放置在离电源较远的地方,模拟器件则被放置在更远的地方。

采用这种布置,高速逻辑对其它信号迹线造成污染的机会较小。振荡器槽回路应远离模拟电路、低速信号和连接器,这一点尤为重要。这既适用于电路板,也适用于包含电路板的盒子内的空间。请勿设计在最终组装后折叠振荡器或微型计算机的电缆组件,因为它们可能会拾取噪声并将其带到其他地方。

在确定元件布局的优先级时,PCB设计中最重要的事情是:

将微处理器定位在电压调节器旁边,电压调节器定位在VBatt进入电路板的地方旁边;

在这三个点之间建立一个网格或坚实的地面(形成一个单点地面),并在该点连接铜皮。

2.信号走线

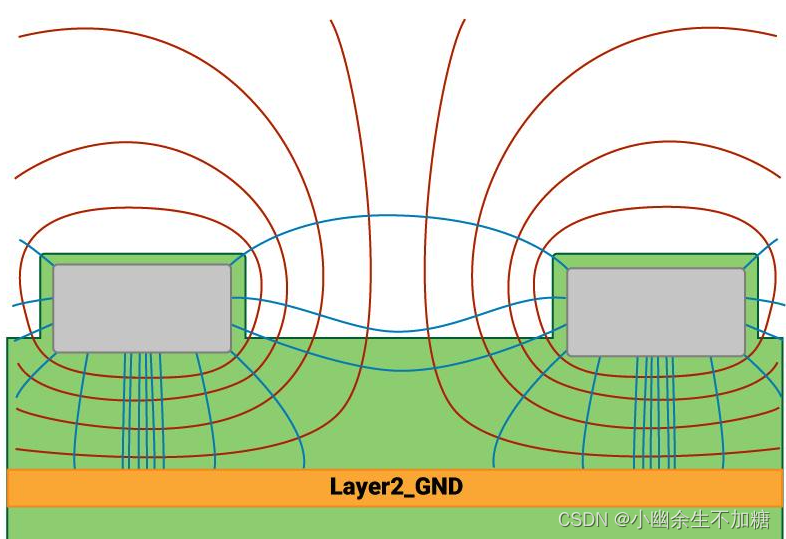

2.1 电容和电感串扰

电容和电感串扰发生在即使很短距离平行走线之间。在电容耦合中,源极上的上升沿导致受害者上的上升沿在电感耦合中,受端电压的变化方向与源端电压的变化方向相反。串扰的大多数实例是电容性的。受害者上的噪声量与平行距离、频率、源上电压摆动的幅值、受害者的阻抗成正比,与间隔距离成反比。 减少串扰的措施有:

将连接到微处理器的带有射频噪声的迹线与其他信号隔开,这样它们就不会耦合噪声。

可能成为噪声受害者的信号应该有其返回地在其下方运行,这有助于减少其阻抗,从而减少噪声电压和任何辐射面积。

不要在板子的外边缘留下嘈杂的痕迹。

如果可能的话,把一些嘈杂的痕迹用地面痕迹围在一起。

将无噪声的走线远离电路板上可能拾取噪声的区域,如连接器、振荡器电路、继电器和继电器驱动器。

大多数与EMI相关的串扰问题都与晶振有关。不相关的器件与晶体的距离不应超过1英寸。

2.2 天线

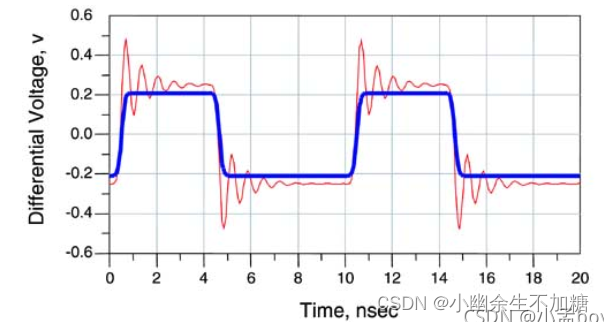

通常,对于联邦通信委员会(FCC)的限制,当迹线长度大于波长的1/10时,迹线长度就变得很重要,对于军用标准限值,该数值为波长的1/20至1/30。对于汽车和消费类两层板,1/50的波长开始变得至关重要,特别是在非屏蔽的应用中。这表示超过4英寸的痕迹可能是FM波段噪声的问题。在这些情况下,建议采取某种形式的终止,以防止振铃。

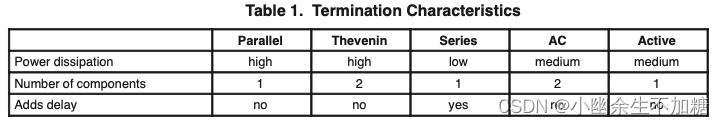

2.3 端接和传输线

端接的主要目的是提供临界阻尼,以实现尽可能高的数据传输速率和尽可能少的过冲。然而,当应用于大多数微控制器系统时,重点转变为在允许系统功能的同时尽可能多地去除总的差模噪声。下表列出了不同的终止方法以及每种方法的主要特点。

请注意,CMOS是一种欠阻尼技术,这意味着必须始终警惕振铃和过冲。如果出现以下任何一种情况,请使用某种形式的端接:

信号走线长度超过1英尺;

信号传输到离开屏蔽外壳的电缆;

存在振铃。

串联电阻是一个廉价的解决方案,终止和振铃问题,是基于微处理器的系统,其中最大限度地减少差模噪声也是一个问题的首选方法。

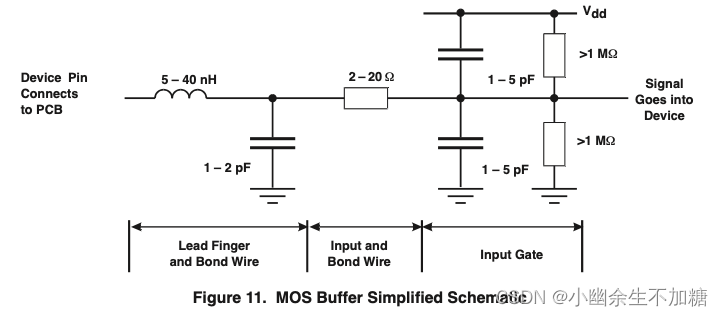

2.4输入端的阻抗匹配

CMOS器件的输入看起来像一个约5-40 nH的串联电感,这导致约5 pF并联,约5 MO到接地基板(见图)这0是一个非常高的阻抗,如果驱动输入的设备没有以某种方式与更高的阻抗匹配,可能会导致大量振铃和其他噪声。这是2.4.3节情况的补充,由于微处理器驱动的负载阻尼不足,所以要注意微处理器的输出。在这里,微处理器是欠阻尼负载,振铃和超调是真正的可能性。更有可能,一些形式的终端将需要,并再次串联电阻是最有可能的解决方案。设置在驱动器上的电阻增加输出阻抗,如跟踪和输入引脚所见,从而匹配输入的高阻抗。

如果输入连接到开路走线,如开关的开路线,建议使用上拉或下拉电阻。虽然这增加了输入激活时的电流切换量但在所有其他时间都降低了阻抗。这减少了跟踪成为耦合噪声受害者的机会。