LabVIEW FIFO详解

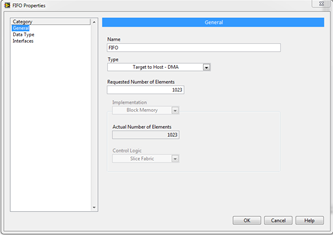

在LabVIEW的FPGA开发中,FIFO(先入先出队列)是常用的数据传输机制。通过配置FIFO的属性,工程师可以在FPGA和主机之间,或不同FPGA VIs之间进行高效的数据传输。根据具体需求,FIFO有多种类型与实现方式,包括目标范围内FIFO(Target-Scoped)、DMA FIFO以及点对点流(Peer-to-Peer)。

FIFO类型

-

**目标范围FIFO(Target-Scoped):**适用于在同一FPGA目标下的VI之间传输数据,灵活但不支持跨时钟域操作。

-

**DMA FIFO(Host to Target/Target to Host):**用于主机与FPGA目标之间的数据传输,广泛应用于高数据吞吐场景。

-

**点对点FIFO(Peer-to-Peer):**点对点传输适合高带宽需求,但需合理处理数据溢出或欠载情况。

实现方式

FIFO的实现方式决定了其性能与资源使用:

-

**触发器(Flip-Flops):**提供最快的数据传输速度,适合小容量数据存储。

-

**查找表(Look-Up Table):**中等大小数据传输的良好选择,兼具性能与资源平衡。

-

**块内存(Block Memory):**适合大容量数据,但读写延迟较高。

-

**UltraRAM:**为大规模存储设计,性能优越,适用于复杂FPGA目标。

根据项目需求,工程师需要在FIFO类型和实现方式上做出最佳选择,平衡性能、资源和系统要求。

块内存(Block Memory)在FPGA中使用时,读写延迟一般在几个时钟周期的量级。具体的延迟通常取决于FPGA的架构和使用的FIFO配置,通常会在 2到6个时钟周期 之间。这意味着在你写入数据后,读取该数据可能需要等待几次时钟周期才能从FIFO中获取。

关于读写相同数据的时间是否有变化,答案是不会有显著变化。每次读写数据的时间是固定的,主要受限于硬件层面实现的固定逻辑延迟。除非系统中出现了特定的条件,比如时钟频率变化、FIFO内存资源紧张或系统负载过大,否则读写相同数据的延迟基本保持一致。

需要注意的是,块内存的高容量与较长的读写延迟是一个权衡。如果系统对速度要求较高,可以考虑使用其他类型的存储(例如触发器或查找表),但这会限制FIFO的容量。