【Verilog学习日常】—牛客网刷题—Verilog快速入门—VL22

根据状态转移图实现时序电路

描述

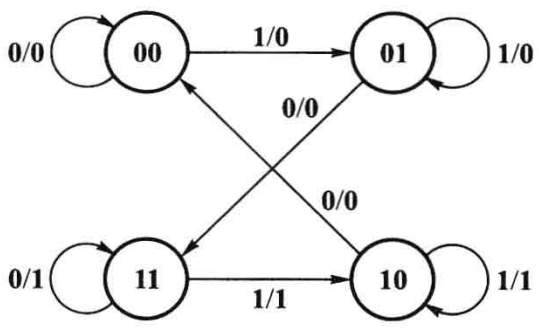

某同步时序电路的状态转换图如下,→上表示“C/Y”,圆圈内为现态,→指向次态。

请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

电路的接口如下图所示,C是单bit数据输入端。

输入描述:

input C ,

input clk ,

input rst_n

输出描述:

output wire Y

解题思路:

根据状态转换图画出功能表,如下所示:

其激励方程、状态方程和输出方程的判定方式与VL21一致;

代码如下:

`timescale 1ns/1ns

module seq_circuit(

input C ,

input clk ,

input rst_n,

output wire Y

);

wire d0, d1, q0, q1;

//激励方程

assign d0 = q0&~C | ~q1&C;

assign d1 = q0&~C | q1&C;

//状态方程

DFF D0 (.d(d0), .clk(clk), .rst_n(rst_n), .q(q0));

DFF D1 (.d(d1), .clk(clk), .rst_n(rst_n), .q(q1));

//输出方程

assign Y = q0&q1 | q1&C;

endmodule

module DFF (

input d,

input clk,

input rst_n,

output reg q

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) q <= 1'b0;

else q <= d;

end

endmodule