arm-硬件

一、ARM体系与架构

- ARM芯片组成

-- arm 体系中,一般讲到的芯片由两大部分组成:arm的内核、外设

-

arm内核: -- 其内核主要由:寄存器、指令集、总线、存储器映射规则、中断逻辑主调试组件构成。ARM公司只设计内核,授权给芯片厂商使用生产芯片,所以ARM只设计不生产。

-

外设: -- 包括计时器、A/D转换器、存储器、I2C、UART、SPI、ROM等。外设由芯片厂商自行设计并与ARM内核衔接配套。不同芯片厂商设计的外设不同,因此构成了数量和规则庞大的ARM芯片。

-

ARM处理器架构

ARM公司2004年推出ARMv7内核架构(ARM11之前的处理器称经典处理器 使用ARM+数字方式命名)之后,使用以Cortex命名方式。分为3个系列:Cortex-A、Cortex-R、Cortex-M Cortex-A系列(A:Application 应用)

面向性能要求高的系统应用:支持高计算要求、运行丰富操作系统、交互媒体和图形体验场景如:智能手机、平板电脑、汽车娱乐系统、数字电视、智能本、电子阅读器 等信息化产品 Cortex-R系列(R:Real-time实时)

面向实时应用的高性能内核,针对实时操作系统。汽车制动系统、大容量存储控制器 等嵌入式应用。

Cortex-M系统(M:MCU &FPGA)

面向各类嵌入式应用的微控制器内核

Cortex-SC系列(SC:SecurCore)

三大系列之外,另一个主打安全的Cortex-SC 应用于政府安全芯片。

-- 总结:Cortex-A 系列是用于移动领域的CPU,Cortex-R和Corext-M系列是用于实时控制领域的MCU。Cortex-M比ARM7的架构高了3代,性能也有较大的提升,分为M0、M3、M4 和超低耗的M0+。

-- tip:ARM公司只设计处理器架构,并不生产CPU。

STM32就是属于ARM公司授权Cortex-M内核给ST公司的一款处理器

ARM处理器模式

- ARM 处理器共有7种运行模式,分为用户、快速中断、外部中断、特权、中止、未定义指令中止、系统模式.

ARM寄存器

-

Arm架构有多个不同的版本和变体,每个版本和变体都有不同的寄存器数量和类型。以下是一些常见寄存器数量:

-

ARM处理器共有37个寄存器。

(1) 1个状态寄存器cpsr

(2) 5个异常模式下的cpsr状态寄存器的影子寄存器spsr

(3) 16个通用寄存器r0 ~ r15

(4) 10个异常模式下的r13和r14的影子寄存器

(5) 5个FIQ模式下的r8 ~ r12的影子寄存器

程序计数器PC为R15、程序链接寄存器LR为R14、堆栈指针寄存器SP为R13。

SP 堆栈指针。

LR ARM处理器相应异常时,或者函数调用时,会自动完成将当前的PC的值-4保存到LR寄存器,便于返回时回到原来的运行地址

PC 指向下一条要执行的指令。

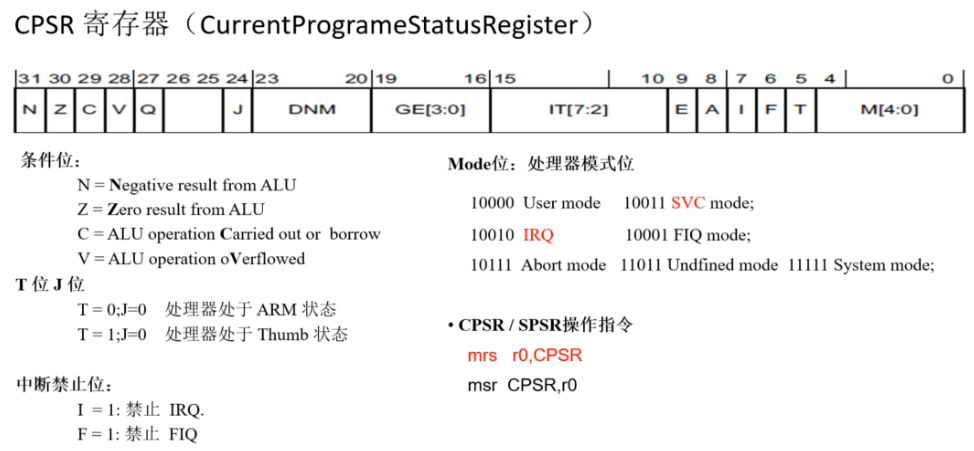

CPSR 程序状态寄存器,记录当前程序的状态。

SPSR 状态切换时保存CPSR的值,便于返回时回到原来的状态。

带三角的是独有的影子寄存器,状态转换的时候原来的不用保存一直在,不带的都是各模式共用的寄存器。

FIQ多个影子寄存器是用空间换时间,处理更快。

什么是CPSR,SPSR?什么时候用到?

- CPSR是当前程序状态寄存器,存储的是当前程序的状态,比如上下文的⼀些寄存器内容,程序运行的话就要用到CPSR。SPSR为备份的程序状态寄存器,主要是中断发生时用来存储CPSR的值的。

简述处理器中断产生和处理的过程。

-

处理器在中断处理的过程中,一般分为以下几个步骤:中断请求 -> 中断响应 -> 保护现场 -> 中断服务 -> 恢复现场 -> 中断返回。

-

arm对异常(中断)处理过程

① 初始化:

a. 设置中断源,让它可以产生中断

b. 设置中断控制器(可以屏蔽某个中断,优先级)

c. 设置CPU总开关(使能中断)

② 执行其他程序:正常程序

③ 产生中断:比如按下按键--->中断控制器--->CPU

④ CPU 每执行完一条指令都会检查有无中断/异常产生

⑤ CPU发现有中断/异常产生,开始处理。

对于不同的异常,跳去不同的地址执行程序。

地址上,只是一条跳转指令,跳去执行某个函数(地址),这个就是异常向量。

③④⑤都是硬件做的。

⑥ 这些函数做什么事情?

软件做的:

a. 保存现场(各种寄存器)

b. 处理异常(中断):

分辨中断源,再调用不同的处理函数

c. 恢复现场

各种中断源发出的中断信号,汇聚到中断控制器,CPU可以读取中断控制器的寄存器,判断当前处理的是哪个中断,中断控制器有多种实现,比如NVIC,GIC。CPU每执行完一条指令,都会判断一下是否有中断发生了,有中断就会根据中断种类在中断向量表中找到中断处理函数,保存现场后跳到中断处理函数执行。执行完恢复现场。

GIC有三种中断类型软件触发中断、私有外设中断、共享外设中断。

什么是中断向量?什么是中断嵌套?

中断向量:中断服务子程序的入口地址。

中断嵌套:中断系统正在执行一个中断服务程序时,有另一个优先级更高的中断源提出请求,这时会暂停当前正在执行的级别较低的中断源的服务程序,处理级别更高的中断源。处理完毕后再返回到被中断了的中断服务程序。

中断的优缺点是什么?

优点:

响应性:中断使得系统能够及时响应外部设备的事件,如输入/输出请求、硬件故障等。它允许系统在接收到中断信号时立即中断当前正在执行的任务,并转而处理中断请求。

高效性:中断机制允许系统在不占用过多的处理器时间的情况下处理异步事件。它使得系统能够在等待外部事件时进行其他任务的处理,提高了系统的效率。

灵活性:中断机制可以处理多个异步事件,每个事件都有自己的中断处理程序。这使得系统可以同时处理多个外部设备的事件,并根据需要进行优先级排序和分配资源。

缺点:

复杂性:中断处理引入了额外的复杂性和开销。系统必须能够正确处理中断请求,并在中断处理程序之间进行上下文切换。这需要额外的硬件支持和操作系统的管理。

不确定性:由于中断是异步发生的,因此中断处理程序的执行时间和顺序可能会受到干扰。这可能导致系统的行为变得不确定,特别是在高并发或高优先级的中断请求情况下。

可靠性:中断处理程序的编写和管理需要特别注意,以确保其正确性和可靠性。不当的中断处理可能导致系统崩溃、死锁或数据损坏等问题。