LPDDR4芯片学习(二)——Functional Description

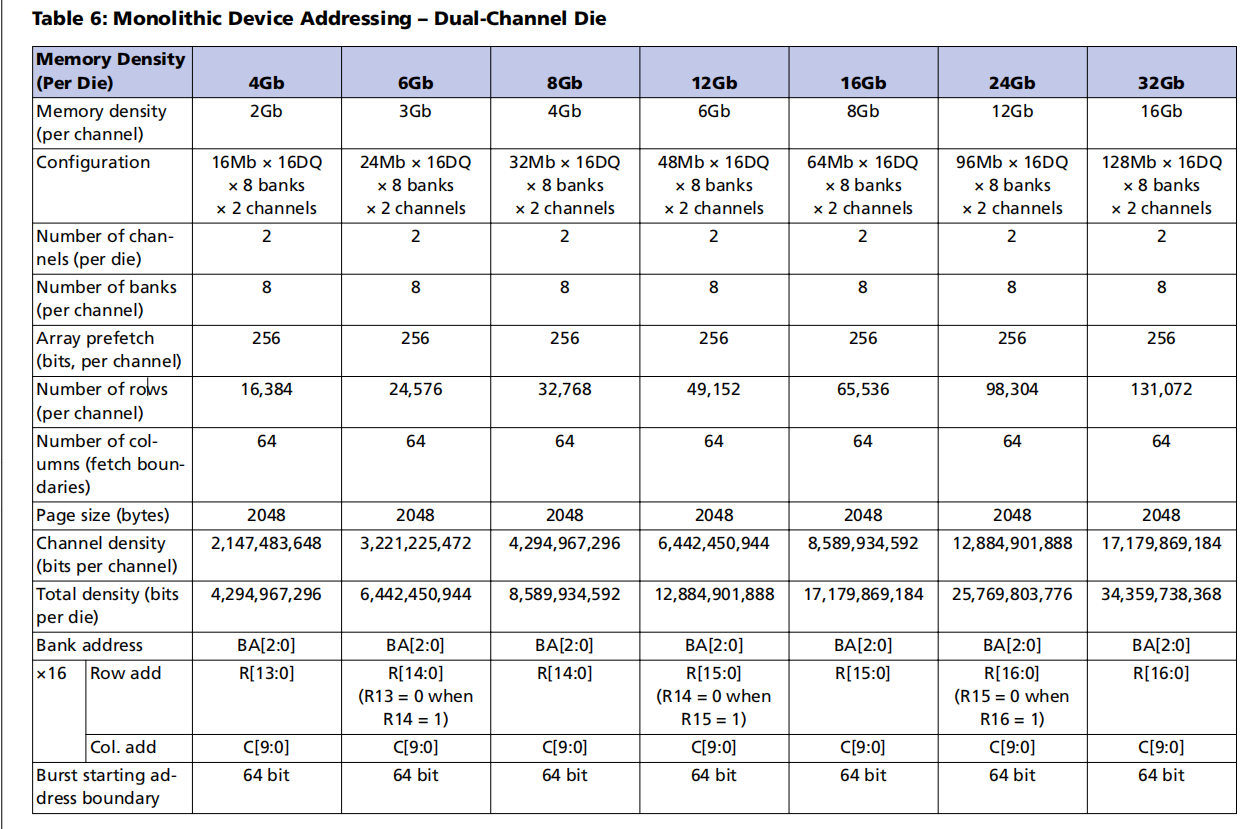

一、LPDDR4寻址表

以每个die容量为4GB为例:

- Memory density(per channel) 2Gb:每个通道大小为2Gb,一个die有两个通道

- Configuration 16Mb × 16DQ× 8 banks× 2 channels :16Mb的寻址空间16位每个channels8个bank*每个die两channels。16Mb为R[13:0] 和C[9:0]组成的寻址空间。 214 × 210 ÷ 102 ÷ 1024 = 16Mb。

- Channel density(bits per channel) 2,147,483,648 :每个通道的粒度,即每个通道可以存储多少位的数据

- Total density (bitsper die) 4,294,967,296:每个die的粒度,每个die有两个channel,这个值为Channel density的两倍

- Bank address BA[2:0]:bank选择通道

- Row add R[13:0] :行选信号

- Col. add C[9:0]:列选信号

LPDDR4协议规范之 (一)地址映射和容量计算_lpddr4 bl-CSDN博客

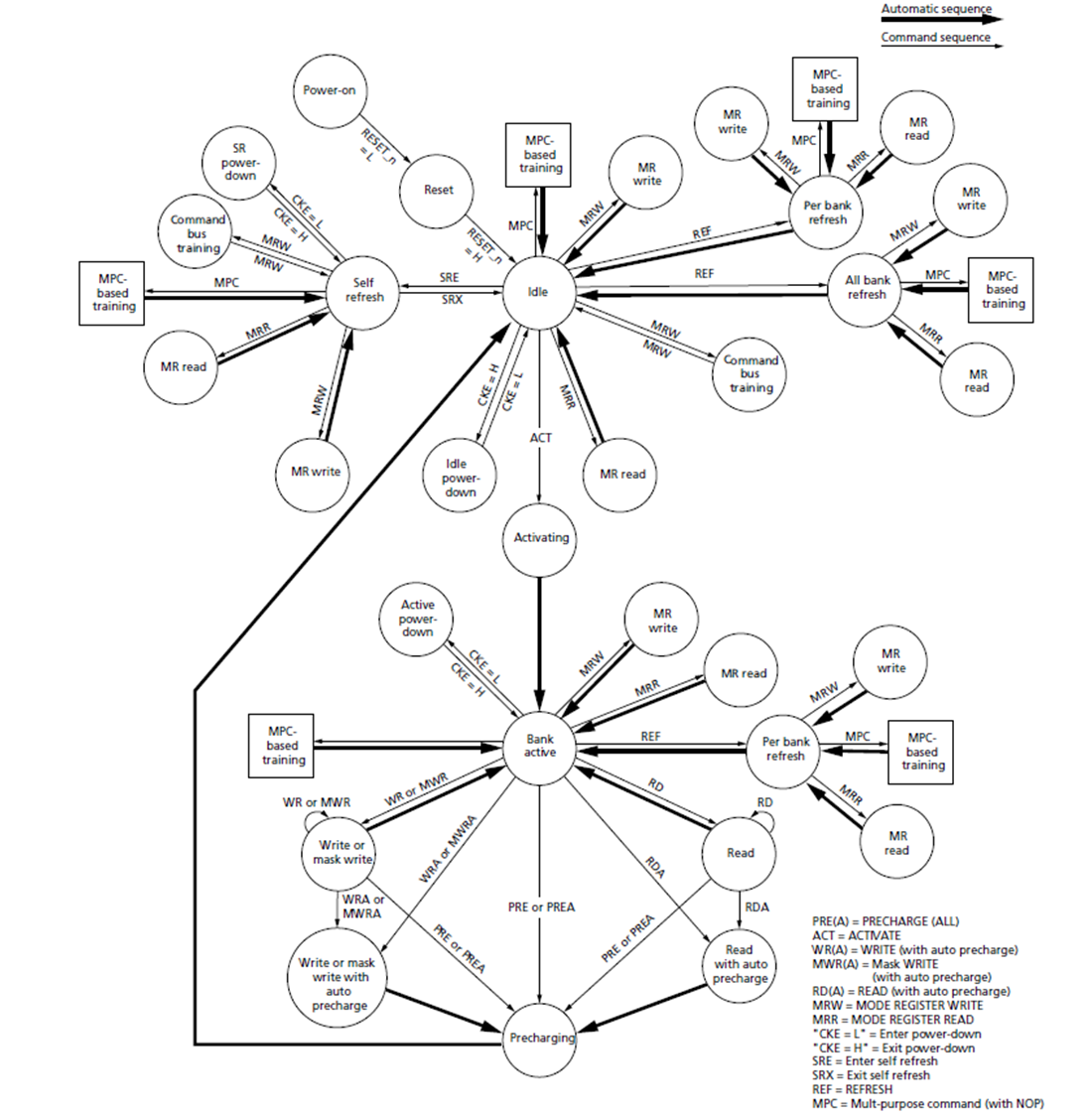

二、LPDDR4 State Diagram

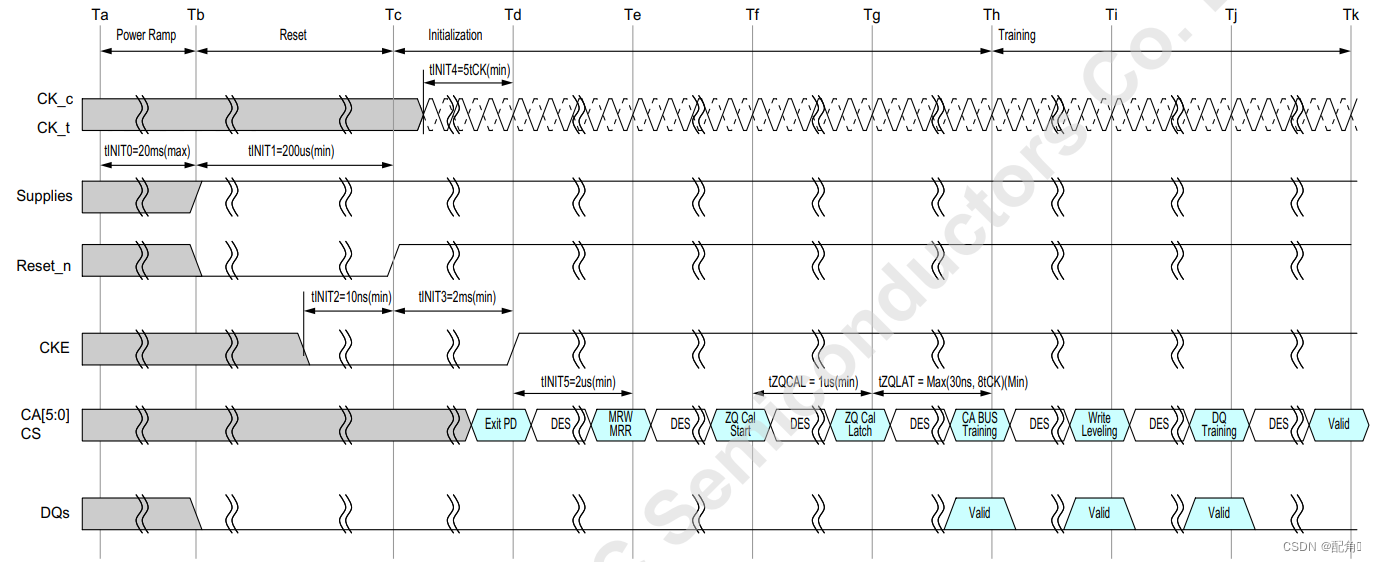

三、LPDDR4上电、复位以及初始化过程

power on -> reset -> ZQ start -> CA BUS Training -> Write Leveling -> DQ Training

- Ta阶段power on后,RESET_n推荐为LOW(≤0.2×Vdd2),所有input必须在VILmin和VIHmax之间。

- Ta时刻上电,至Tb时刻上电结束,该过程不大于20ms,在这个过程,Vdd1升压必须同时或早于Vdd2,Vdd2同时或早于Vddq;

- Tb时刻开始,RESET_n需要保持为低至少200us至Tc,所有的输出在RESET_n为低期间全部保持高阻态Z,Tc前也就是RESET_n变为非有效值之前至少10ns,CKE需要设为低。

- Tc时刻,复位释放,需要至少等待2ms才可以断言CKE,并且在CKE断言之前CS信号保持为低,CKE断言之前,clk需要稳定至少五个周期。

- CKE使能之后,后续会完成模式寄存器读写、ZQ校准、CA training、Write Leveling、DQ Training,即完成初始化。

注:上述步骤是强制的,并且all通道是同时的。除非特殊指定。

power off:即CKE拉低(≤0.2×Vdd2),CKE拉低期间,所有输出会保持高阻态Z。

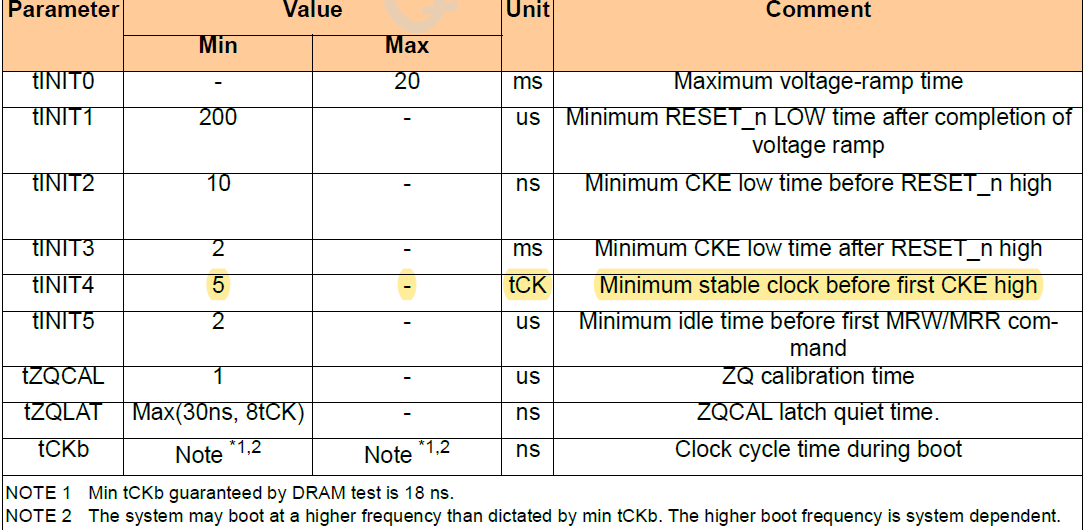

Timing Parametres: