|

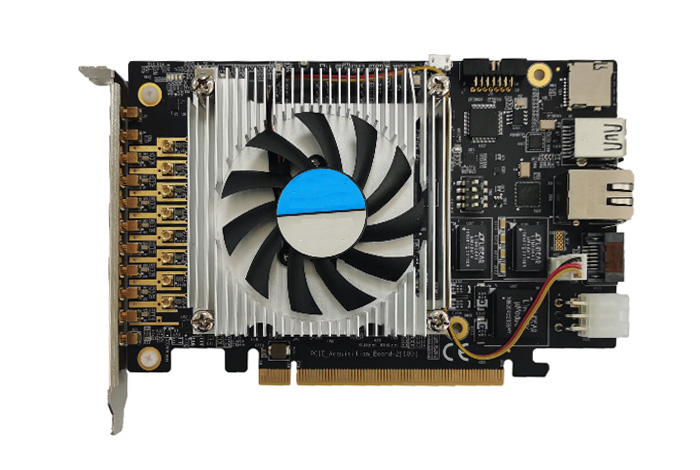

一、板卡概述 板卡使用Xilinx的第三代RFSOC系列,单颗芯片包含8路ADC和DAC,64-bit Cortex A53系列4核CPU,Cortex-R5F实时处理核,以及大容量FPGA。 对主机接口采用PCIe Gen3x16,配合PCIe DMA传输,支持高速数据采集和传输。

二、板卡特性:

- 基于Zynq RFSoC系列FPGA,支持8路最高5G ADC和8路最高10G的DAC

- PL 2组64bit 2400M DDR4,支持PL部分高速存储和处理。 单组4GB字节容量,PL部分8GB字节容量。

- 标准PCIe全高半长板型(167 x 111 mm ),适配常见主机、服务器

- PCIe Gen3 x16,高速数据通讯,附带DMA传输例程

- 可快速修改版型,支持客户定制开发

- PS部分1组64bit位宽DDR4,单组4GB字节

- 可配置的Dual QSPI 加载

- 支持MicroSD卡加载

- 1000Base-T以太网(RJ45)端口(CPU端)

- USB接口支持

- 支持外部时钟输入

三、FPGA设计框图:

PL部分,主要分为:

- PCIe DMA部分,PCIe分为寄存器通道和数据DMA通道,寄存器用于板卡控制和状态监控,数据DMA用于读取ADC采集的数据。

- DDR4控制管理,包括ADC的数据写入DDR4,以及上位机从DDR4中读取数据。

- RF硬件控制,用于控制板卡上PLL,ADC和DAC控制。

- 数据处理模块,即用户的数据处理部分。可根据客户的要求定制开发。

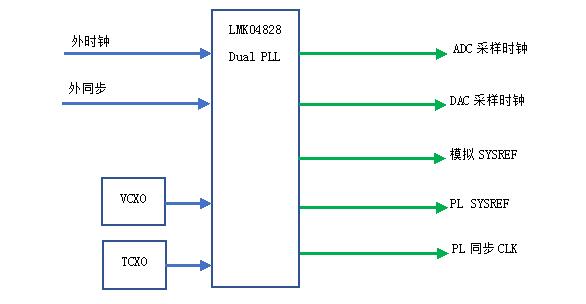

板卡时钟灵活,支持多种应用配置,模拟部分的时钟,采用LMK04828,双PLL锁相环。 如果采用板内时钟,用TCXO和VCXO双锁相环,提供稳定可靠的模拟时钟。同时也输出一路给FPGA进行数字处理。 该方案也支持使用外部独立输入时钟,通过LMK04828扇出后输出给ADC和DAC。

数字部分,使用高集成度的SI5341B,单路芯片输出PS和PL所需的各路时钟。

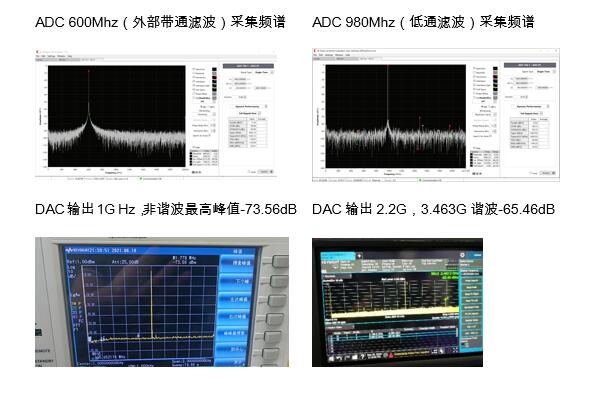

四、部分测试结果:

|