SIwave:释放 EMI 扫描仪/探测器的强大功能

SIwave 是一种电源完整性和信号完整性工具。信号网络分析仪求解器是 SIwave 中的工具之一,本视频将对此进行讨论。

EMI 扫描仪是对 PCB 布局的快速扫描。它查找可能导致 SI、PI 或 EMI 问题的主要设计缺陷。此扫描仪是设计师在上传新机械设计时需要做的第一件事。

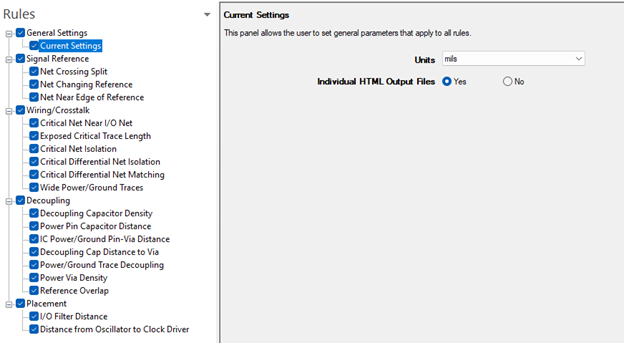

图 1:EMI 扫描仪

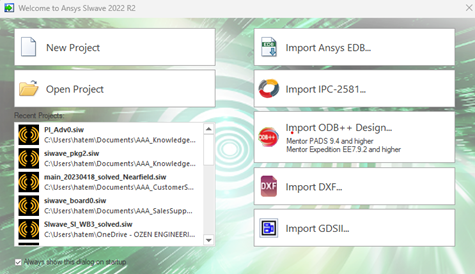

SIwave 不应用于构建 PCB。虽然这是可能的,但这不是使用 SIwave 的最佳方式。但是,请尝试从专业 CAD 文件导入文件。SIwave 可以导入以下类型的 CAD 文件:

图 2:导入文件

SIwave 中的任何过程都从选择求解器开始。选择求解器后,会弹出一个对话框,用户只需填写表单并提交即可。

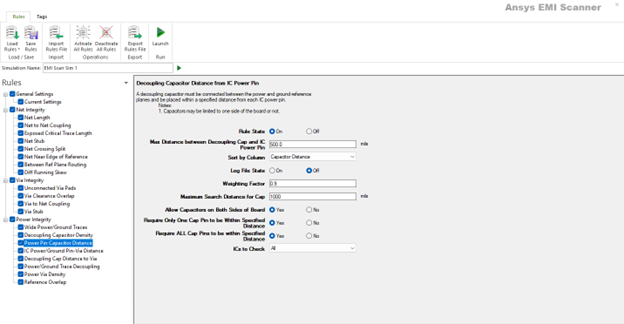

因此,我们选择 EMI 扫描仪来获取此对话框。

图 3:EM 和 SI 规则

每种维度和关系都有默认规则。用户可以修改这些规则中的任何一个。这些规则只是意味着,如果尺寸小于/大于规格,则您的设计中很可能会出现问题。

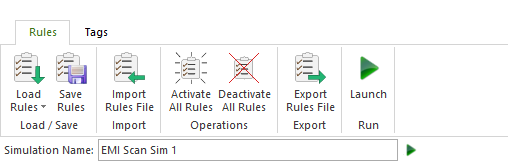

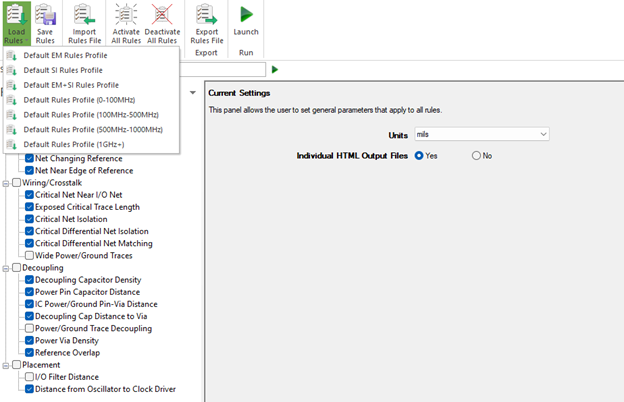

用户可以导入工具、激活规则和停用规则。用户还可以导出工具以备将来使用。

图 4:导入/导出规则

用户需要了解几种类型。

SI 规则

图 5:SI 规则

EM 规则

图 6:EM 规则

频率相关 EMI 规则

图 7:EM 规则 – 频率相关

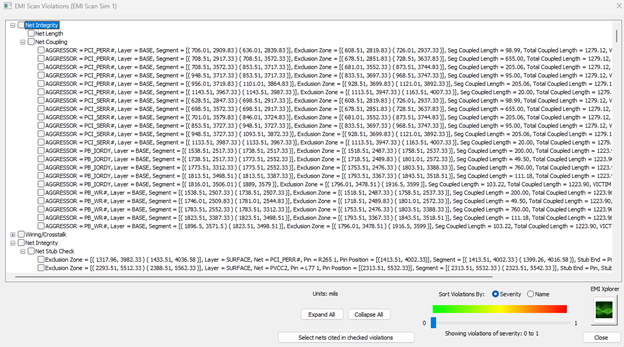

扫描后,用户可以显示报告。

图 8:警告列表

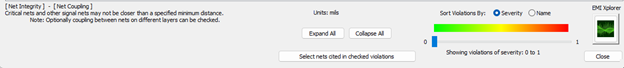

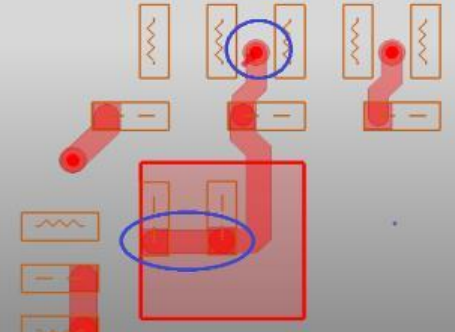

单击任意行可查看规则底部的描述。SIwave 还将放大问题的位置。

图 9:违规描述

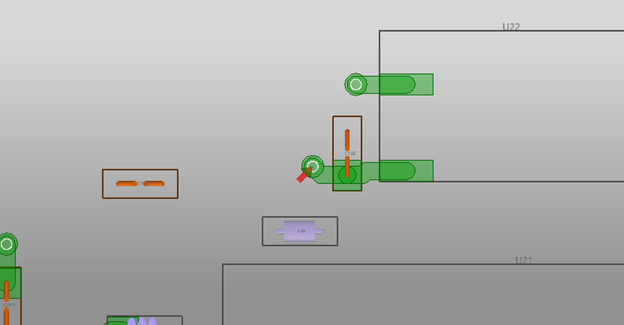

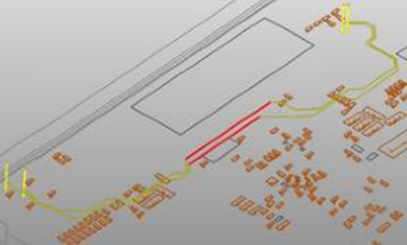

图 10:违规位置

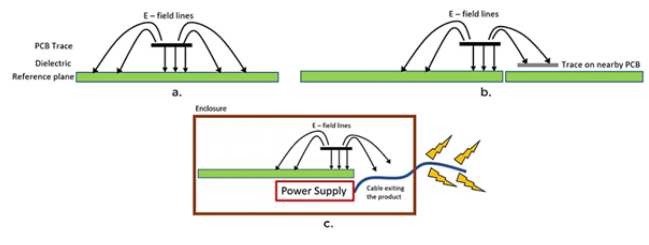

如果您想了解更多信息,请单击 EMI 扫描以查看问题的直观描述,以及信号分析和违规造成的损坏。对于某些规则,将不会显示任何内容。请注意,信号分析显示默认值和违规结果。用户可以添加更多选项并查看对信号的影响。这些情节可以有许多不同的形式,这取决于规则。它们可以是阻抗、电流或电压形式。

图 11:现象的详细描述

让我们放大这些规则,看看我们可以从中得出什么结论:

规则列表:

- 网络交叉拆分

- 净变化参考

- Net Near Edge of Reference

- 关键网络 靠近 I/O 网络

- 暴露的临界迹线长度

- Critical Net 解决方案

- 关键差分网络隔离

- 关键差分网络匹配

- 宽电源 / 接地走线

- 去耦电容器密度

- IC 电源/接地参考引脚到过孔的距离

- 去耦电容到过孔的距离

- 去耦电容与 IC 电源引脚的距离

- 电源/接地走线去耦

- 电源过孔密度

- 参考重叠

- I/O 滤波器距离

- 振荡器到时钟驱动器的距离

- 净长度

- Net to Net 耦合

- 净子

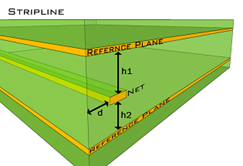

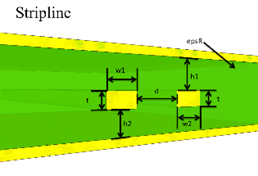

- 参考平面之间布线

- Diff Running Skew

- 未通过 Pads 连接

- 过孔间隙重叠

- 过孔到网络耦合

- Via Stub

C:\Program Files\AnsysEM\v231\Win64\config\EMIScanner\ViolationAnalyzerImages

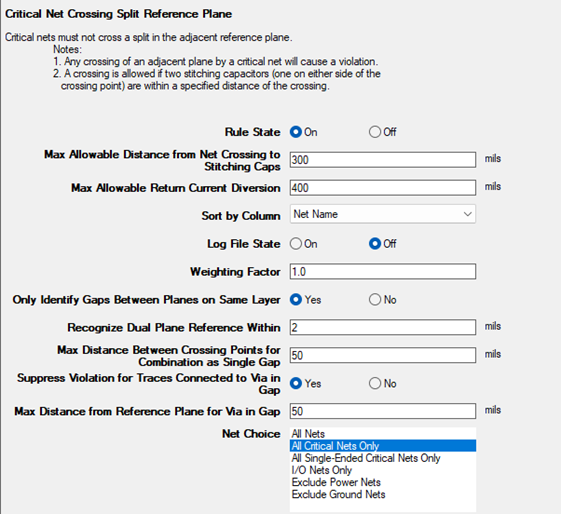

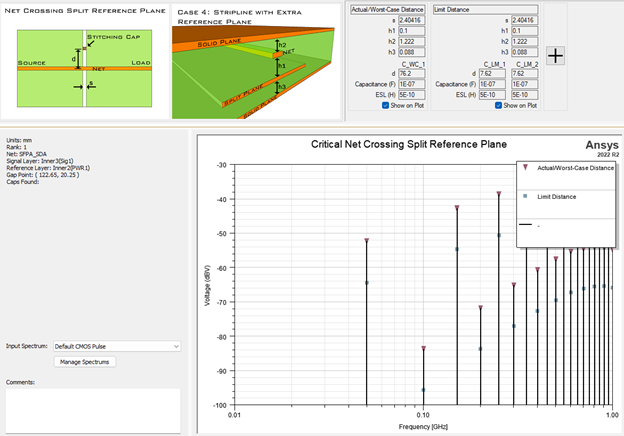

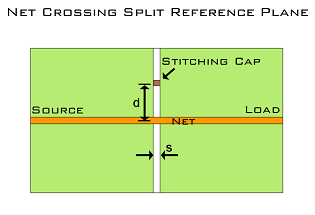

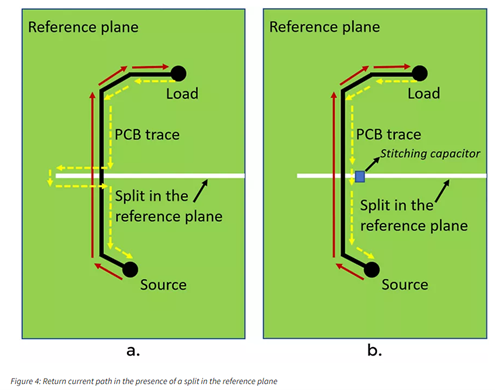

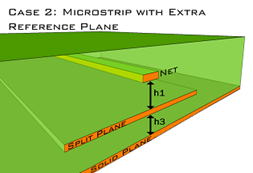

网交叉分割

图 12:表单

图 13:结果

图 14:模型

https://www.ansys.com/blog/pcb-design-rules

图 15:示例

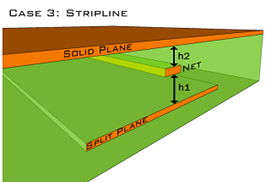

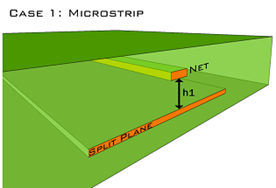

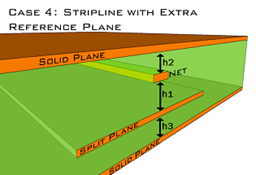

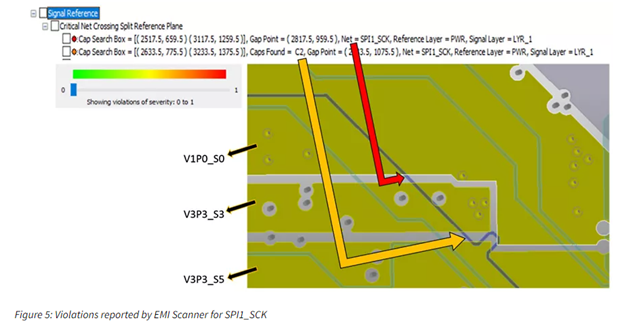

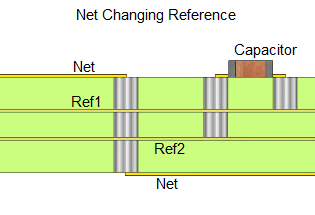

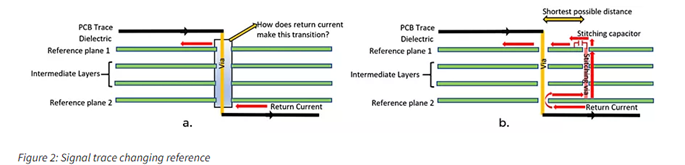

净变化参考

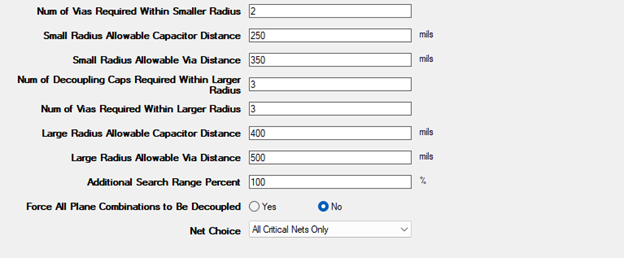

图 16:表单

图 17:模型

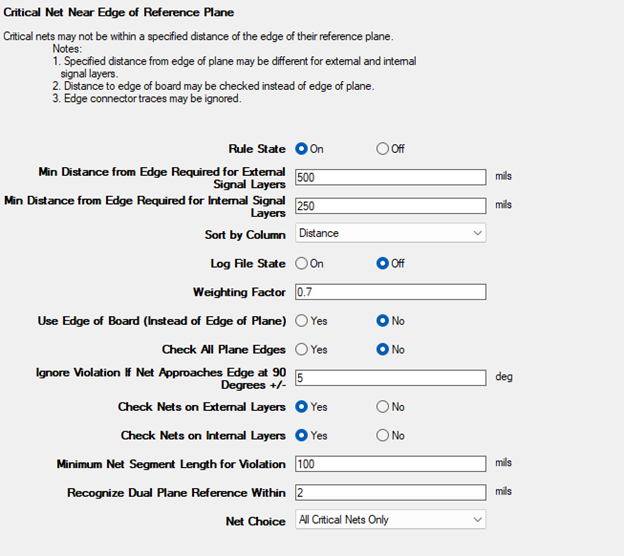

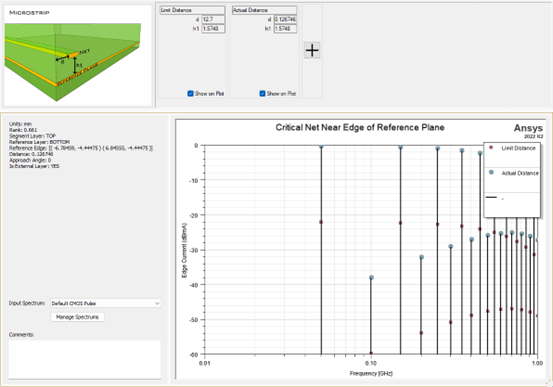

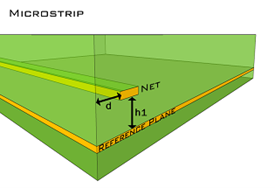

Net near edge of reference (网络近参考边缘)

Figure 18: Form

图 19:结果

图 20:模型

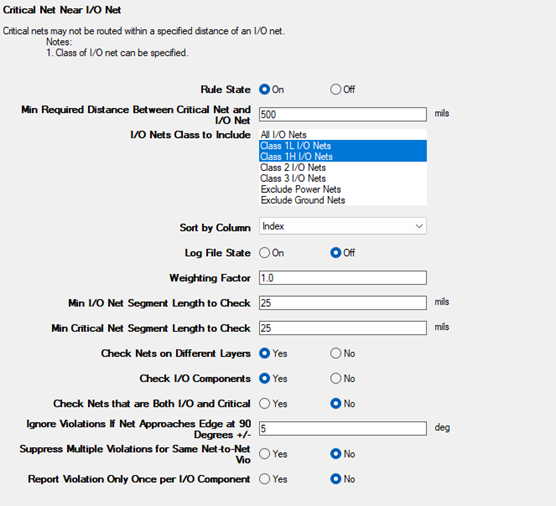

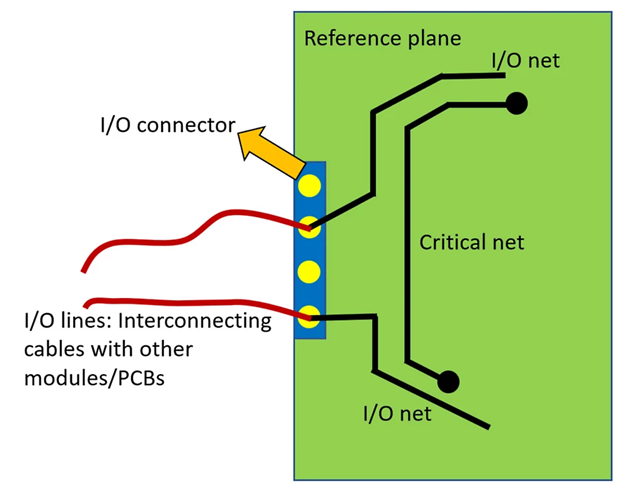

靠近 I/O 网络的关键网络

图 21:表单

https://www.ansys.com/blog/pcb-design-rules-wiring-and-crosstalk

图 22:模型

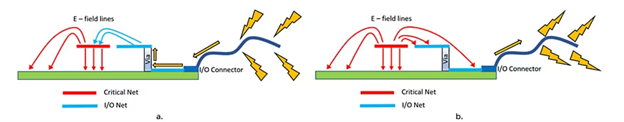

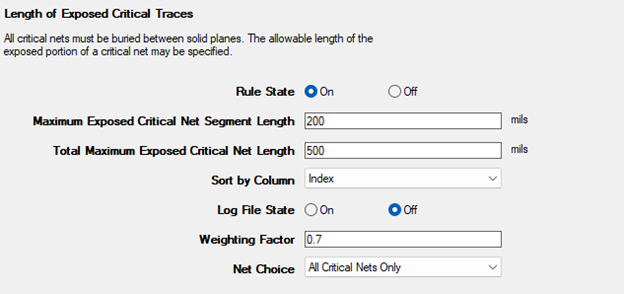

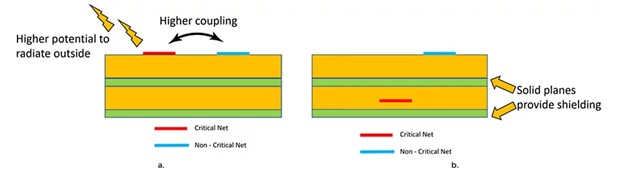

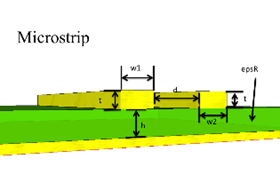

暴露的临界迹线长度

图 23:表单

https://www.ansys.com/blog/pcb-design-rules-wiring-and-crosstalk

图 24:模型

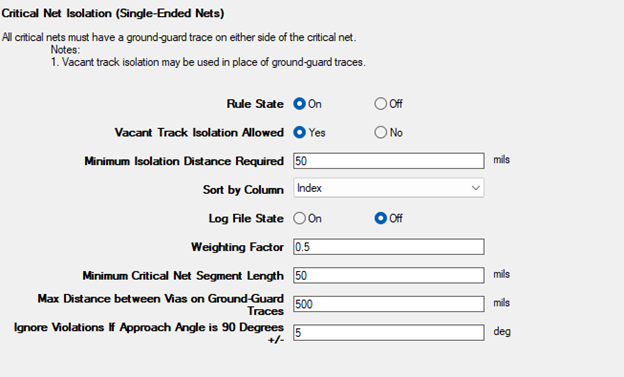

关键网络隔离

图 25:表单

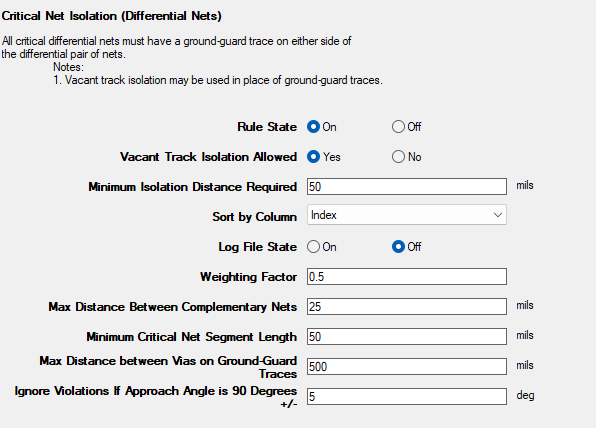

临界差分网络隔离

图 26:表单

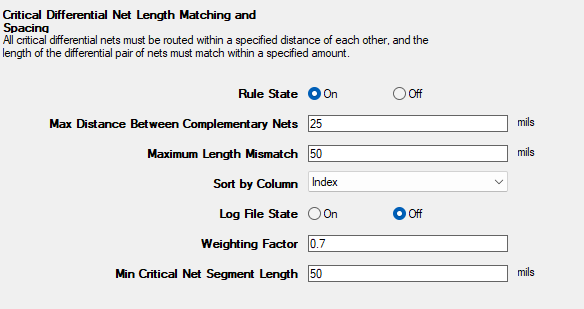

关键差分网络匹配

图 27:表单

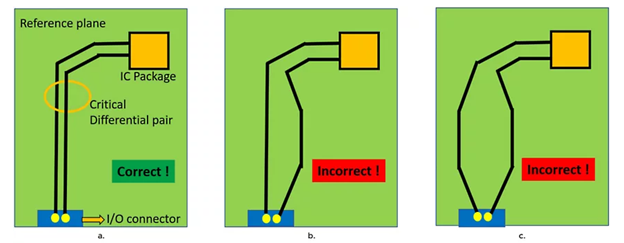

https://www.ansys.com/blog/pcb-design-rules-wiring-and-crosstalk

图 28:模型

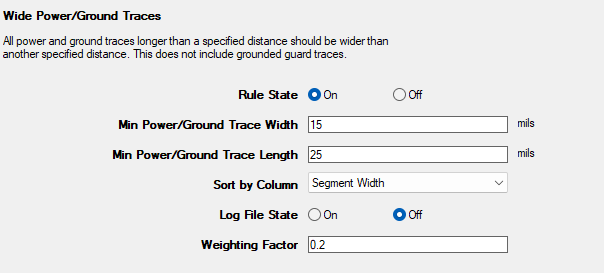

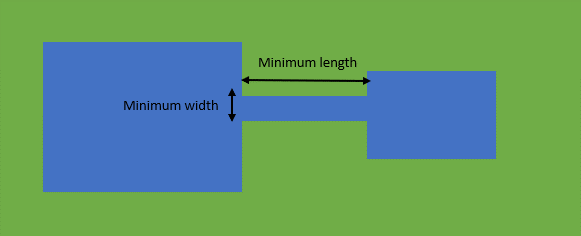

宽电源/接地走线

图 29:表单

图 30:模型

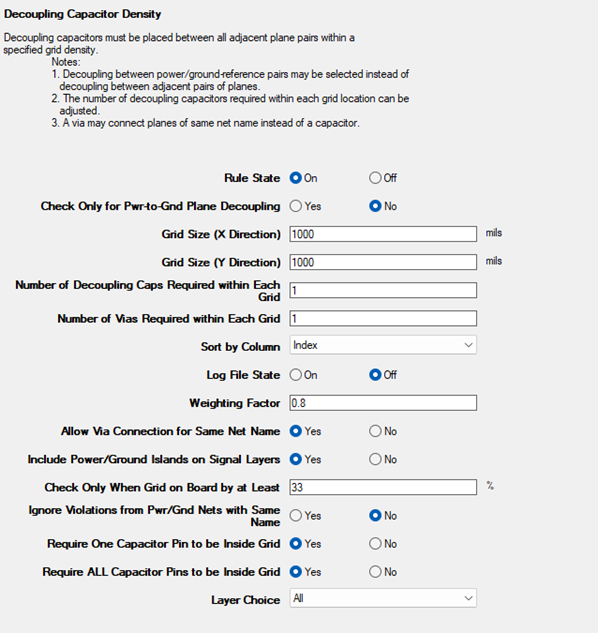

去耦电容器密度

图 31:表单

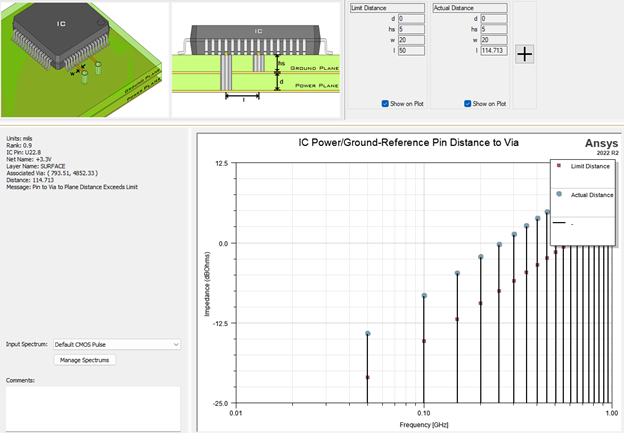

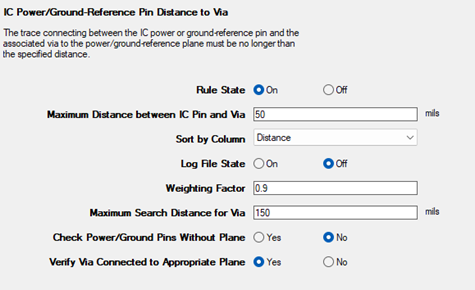

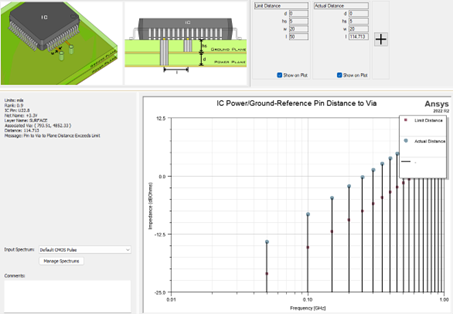

IC 电源/接地参考引脚到过孔的距离2

Figure 32: Form

Figure 33: Result

Figure 34: Models

https://harrisburg.psu.edu/files/pdf/16506/2019/04/24/ansys_penn_state_si_symp_2019_final.pdf

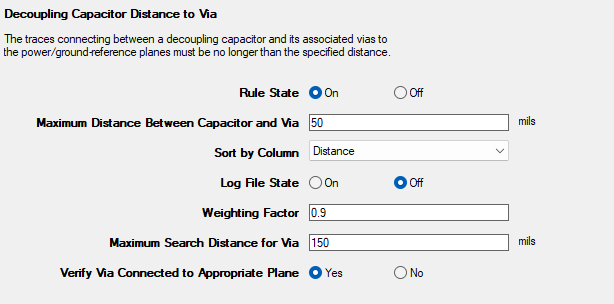

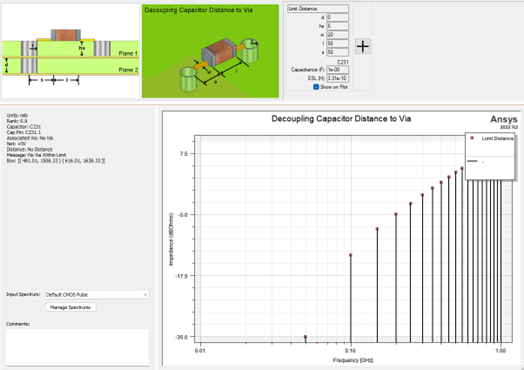

去耦电容到过孔的距离2

图 35:表单

图 36:结果

p_2019_final.pdf

图 37:模型

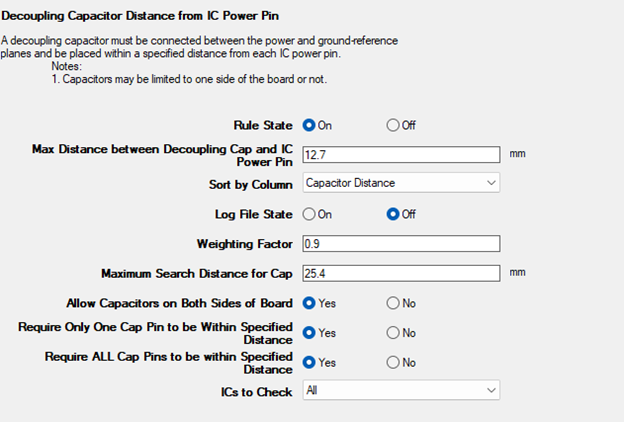

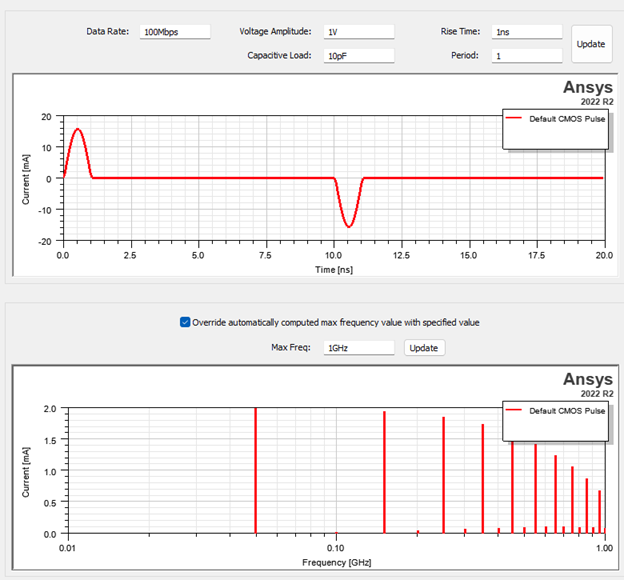

去耦电容器与 IC 电源引脚的距离(电源引脚电容器距离)

图 38:表单

Figure 39: Result

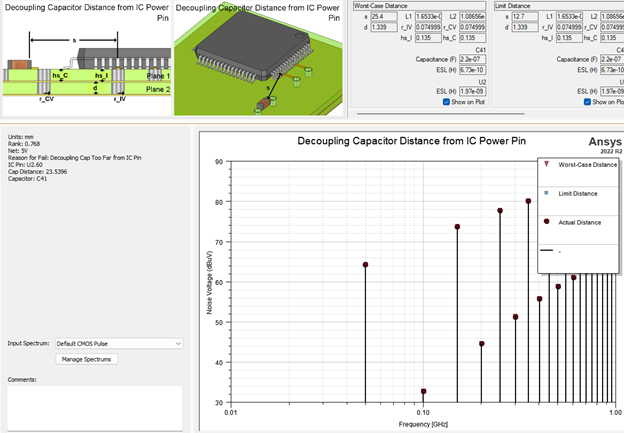

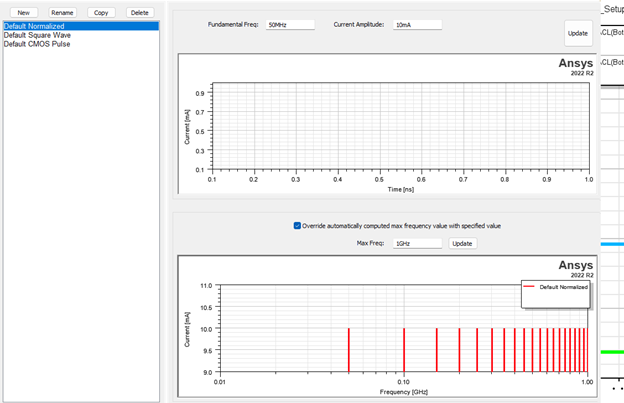

You can enter Normalized, square or CMOS pulse signal

图 40:信号

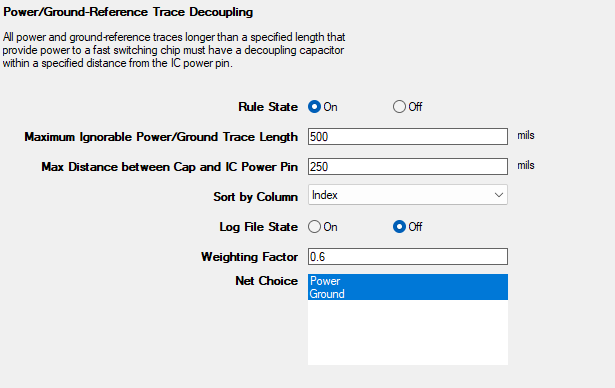

电源/接地走线去耦

图 41:表单

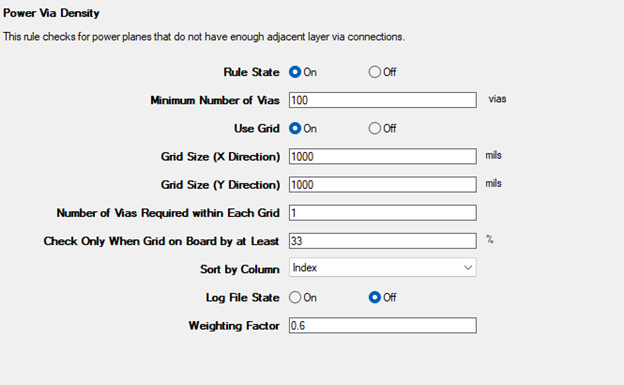

功率过密度

图 42:表单

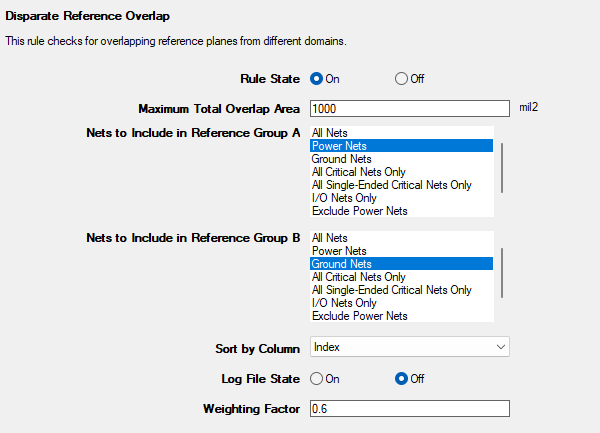

参考重叠

图 43:表单

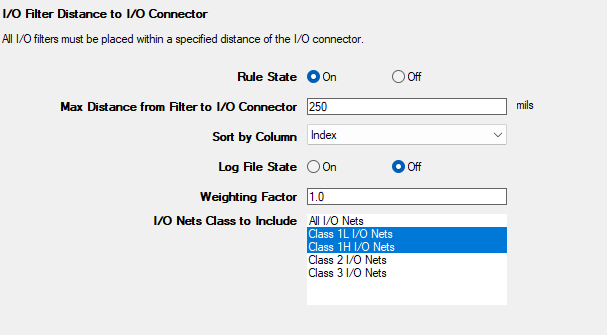

I/O 滤波器距离

图 44:表单

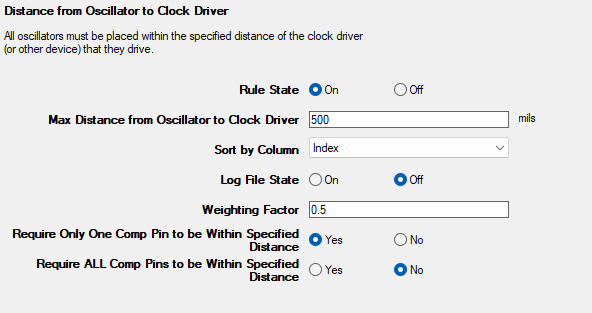

振荡器到时钟驱动器的距离

图 45:表单

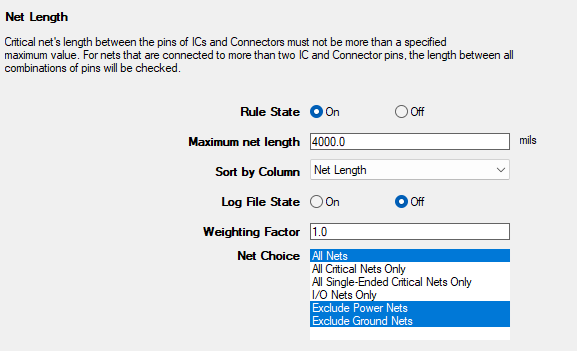

净长度

图 46:表单

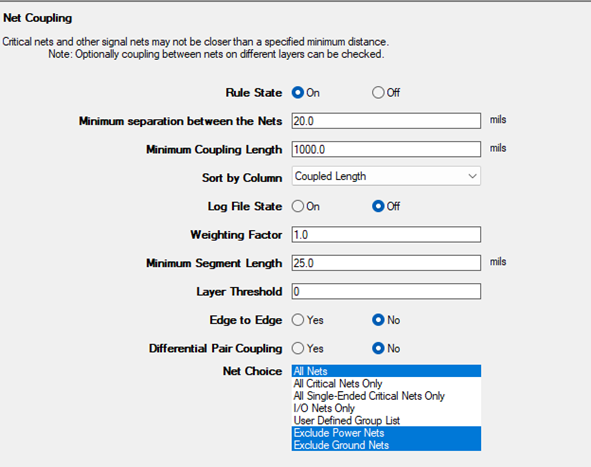

Net 到 Net 耦合

图 47:表单

https://harrisburg.psu.edu/files/pdf/16506/2019/04/24/ansys_penn_state_si_symp_2019_final.pdf

图 48:模型

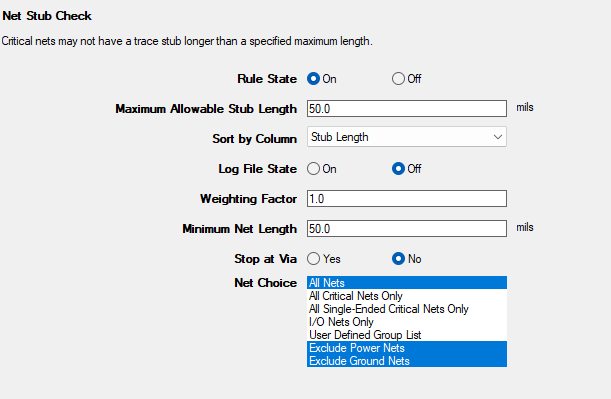

净潜

图 49:表单

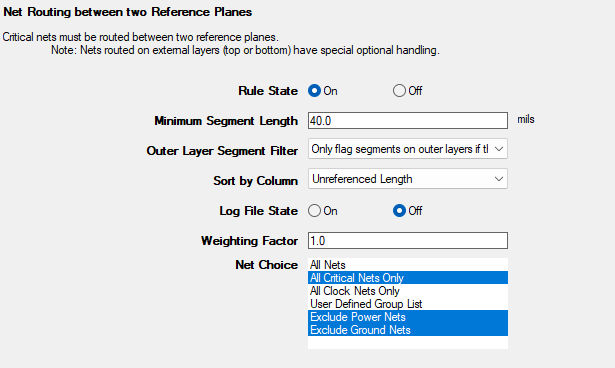

参考平面布线之间

图 50:表单

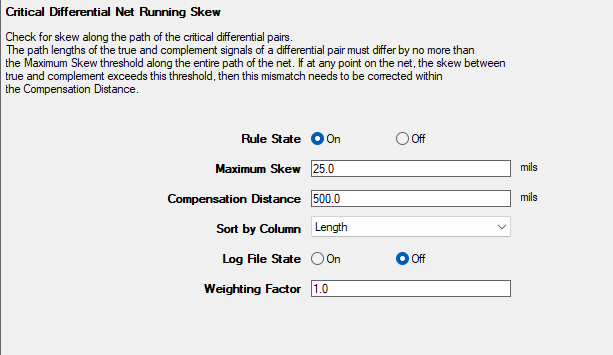

Diff running skew (差分运行偏斜)

图 51:表单

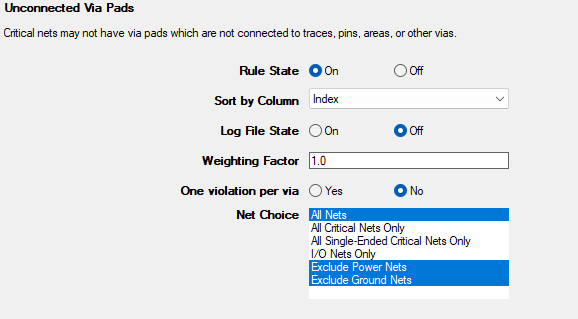

未通过焊盘连接

图 52:表单

过孔间隙重叠

Figure 53: Form

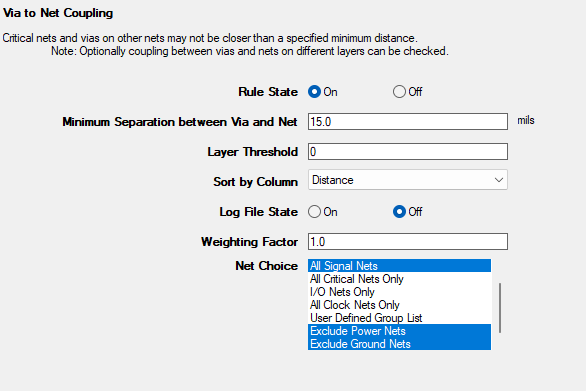

Via to net coupling

图 54:表单

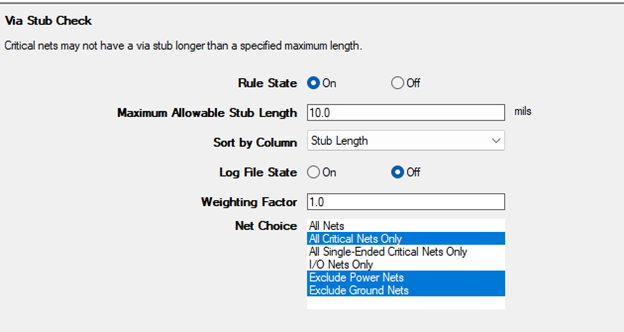

Via stub (过孔短线)

图 55:表单

https://harrisburg.psu.edu/files/pdf/16506/2019/04/24/ansys_penn_state_si_symp_2019_final.pdf

图 56:模型