STM32各模块

1.工程文件结构:

startup前缀的汇编文件是来调用system前缀的文件来进行系统初始化和时钟配置,然后调用自定义的main函数,包括很多stm32f10x_it文件定义的中断处理函数。

stm32f10x.h定义了stm32所有外设寄存器描述,core_cm3文件定义了内核寄存器的一些功能。stm32f10x_conf.h主要是对标准库函数的一些配置操作,内部包含了所有标准库函数的头文件,而stm32f10x.h中也包含了这个stm32f10x_conf.h,所以无需重复包含即可调用标准库的函数。

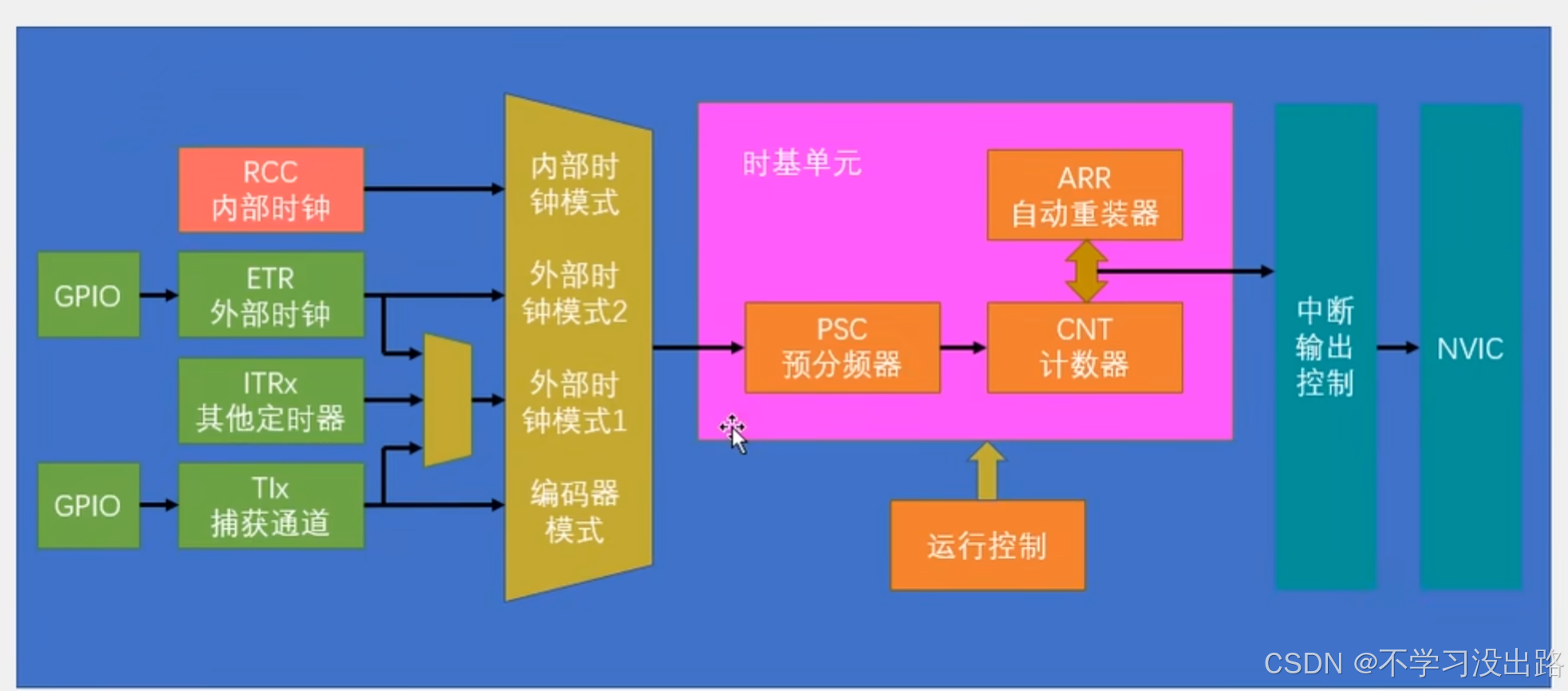

2.定时器结构

- 对于内部时钟RCC,只需要配置时基单元内的ARR自动重装器的

3.EXTI外部中断的结构

4.PWM模式

ADC

DMA

UART

起始位固定为低电平,停止位固定为高电平,停止位拉高电平,当新数据发送时,起始位会拉低电平表示发送开始。校验位要么无校验、偶校验或这奇校验。寄校验和偶校验都是确保1的个数为奇数或者偶数,若接收方收到后,1的数量与预期不符则判定发生错误。

停止位可以是0.5位、1位、1.5位、2位。最常见为1位。

数据位可以是5位、6位、7位、8位、9位。最常见的为8位。

IIC

所有设备都是开漏输出模式,原因是:

避免冲突:开漏输出+上拉电阻的设计

如果所有设备都使用推挽输出,在同一时刻可能会出现以下冲突:

一个设备试图将SDA线拉高(输出高电平),而另一个设备同时试图将SDA线拉低(输出低电平),这种情况会导致信号冲突,并可能损坏设备。

首先SDA和SCL由于上拉电阻的存在,当SDA和SCL都没有被设备驱动时,即总线空闲时,两个总线都是高电平。当主机要发送数据时,先将SDA拉低,以通知从设备准备接收数据,随后拉低SCL,往SDA上驱动高低电平数据,然后拉高SCL,方便从设备在SCK高电平阶段读取SDA获得一位数据,随后主设备再次拉低SCL,往SDA上发一位数据,再拉高SCL,让从设备读取SDA数据,依次类推,传输完7位地址数据+读写位以后,主设备释放SDA线(即SDA的GPIO口设置为输入状态),从设备的SDA线为开漏输出模式,在下一个时钟周期拉低SDA线表示确认收到数据ACK。在ACK之后,根据发送的最后一位是读还是写(0是写入,1是读取),来决定接下来是谁发送数据?如果是写,则主设备继续发送数据,还是按照SCK低电平时写入数据到SDA,从设备高电平时读取。如果是读,则从设备发送数据,SCL一直由主设备驱动,当SCL位低电平时,从设备传入一位数据到SDA,主设备在SCL高电平时读取该位。当接收方不再需要接收数据时,选择发送NACK,即不拉低SDA,保持SDA由上拉电阻导致的高电平,随后由主设备先拉高SCL,随后主设备拉高SDA,来生成停止条件,随后主设备释放SCL和SDK的输出控制。

SPI

在片选信号拉低时,开始传输,拉高时表示结束传输。