SIwave:释放 SIwizard 求解器的强大功能

SIwave 是一种电源完整性和信号完整性工具。SIwizard 是 SIwave 中 SI 分析的主要工具,也是本博客的主题。

SIwizard 用于研究 RF、clock 和 control traces 的信号完整性。该工具允许用户进行瞬态分析、眼图分析和 BER 计算。用户可以将 IBIS 和 IBIS-AMI 模型添加到 TX 和 RX 端。SIwave 支持 NRZ 和 PAM4 信号。

图 1:SIwizard 求解器 4th图标

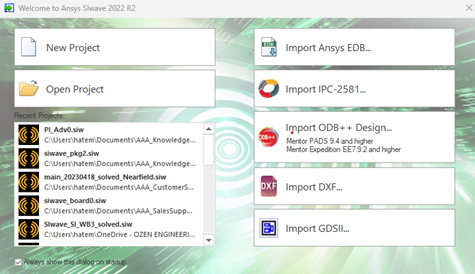

SIwave 不应用于构建 PCB。虽然这是可能的,但这不是使用 SIwave 的最佳方式。SIwave 可以导入以下类型的 CAD 文件:

图 2:SIwave 中的导入对话框

Allegro 和 Altium 的用户可以安装 Ansys EDB 转换器来生成 EDB 文件。对于使用 Orcad 的用户,建议使用 IPC-2581。使用 Mentor Expedition 的人应该使用 ODB++ 文件。对于 Cadence 用户,生成 BRD 文件并将其导入 3D 布局。为此,必须在同一台计算机上安装 Cadence,还必须安装 Extracta from Cadence,并且其位置应位于 Path 环境变量中。

SIwave 从 CAD 文件中提取大量信息,例如叠层、材料、组件和网络。因此,模型已准备好进行求解。

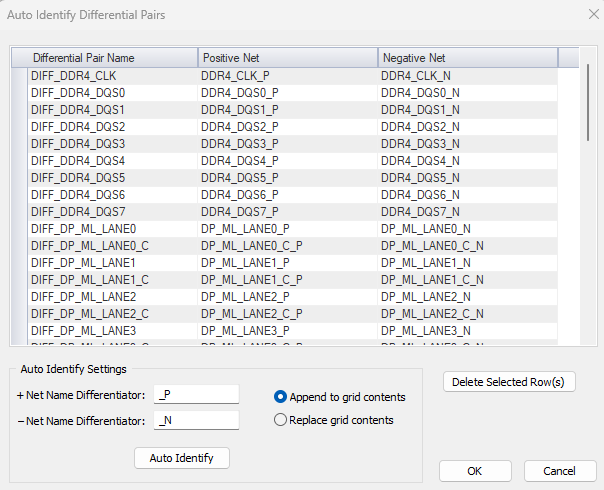

- 差分线路

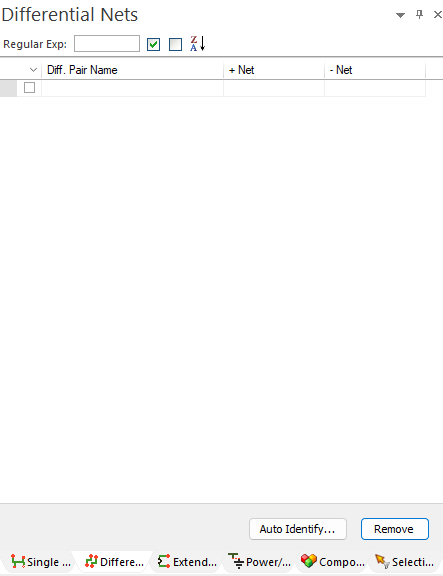

在启动 SIwizard 之前,请确保 SIwave 识别差分走线。从 Home 中,选择 differential 选项卡。

图 3:差分网络选项卡

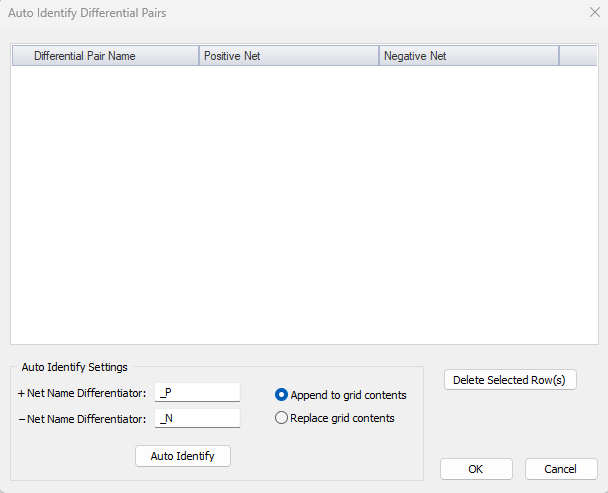

如果它是空的,但用户确定模型中存在差分线,则单击自动识别。SIwave 将打开一个新对话框,并显示它使用什么符号来识别 _P 和 _N 的差分线。如果正确,请单击 auto-identify(自动识别)。如果不同,用户必须在对话框中更改它们。

图 4:差分网络自动识别对话框

单击自动识别后:

图 5:自动识别走线后的 Differential nets 选项卡

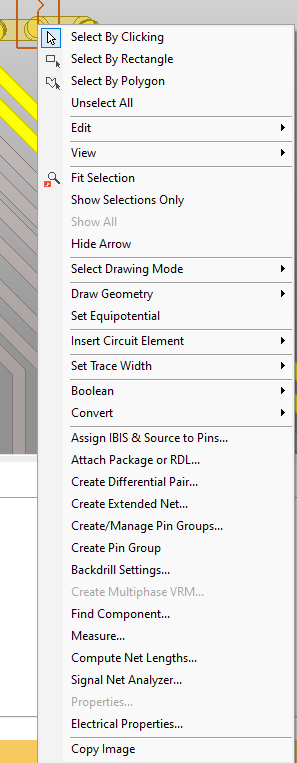

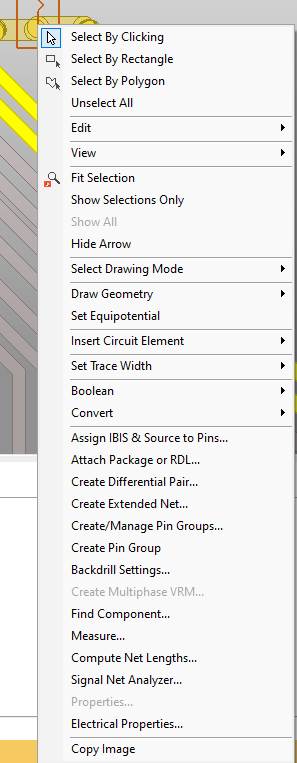

用户还可以手动选择两个网络,将鼠标移动到显示区域,右键单击,然后选择 Create Differential Pairs。

图 6:构建差分网络的替代方法

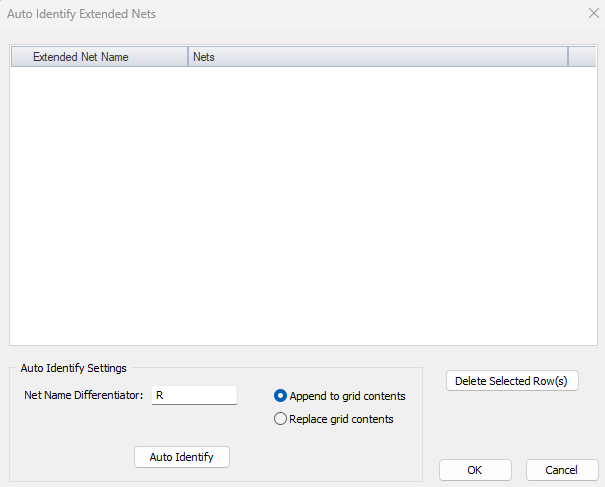

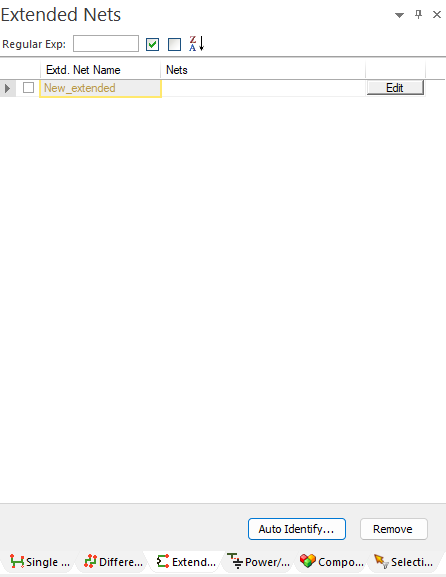

如果 DC 模块将差分线路分开,用户可以选择先将线路合并为扩展网络,然后从中创建差分线路。首先单击扩展选项卡,然后选择 auto-identify

图 7:扩展网络自动识别对话框

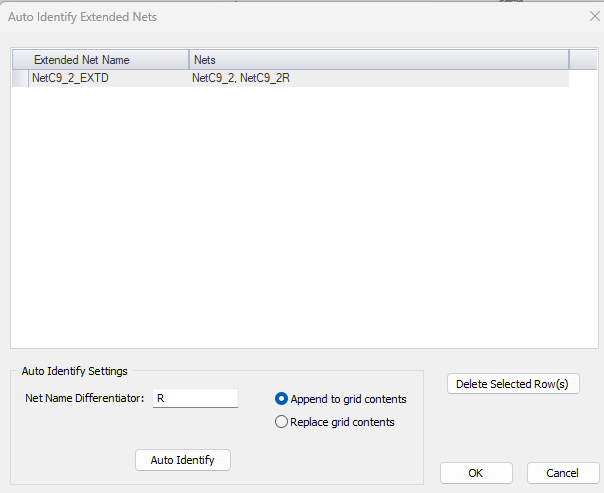

SIwave 将显示一个对话框,显示 SIwave 使用 R 来识别扩展网络。因此,任何两个名称相同但一个末尾有额外 R 的网络将被合并。

图 8:扩展网络自动识别对话框

创建扩展网络的另一种方法,特别是当网络有两个以上的网络时,是输入扩展网络的名称,然后单击 edit:

图 9:扩展网络选项卡

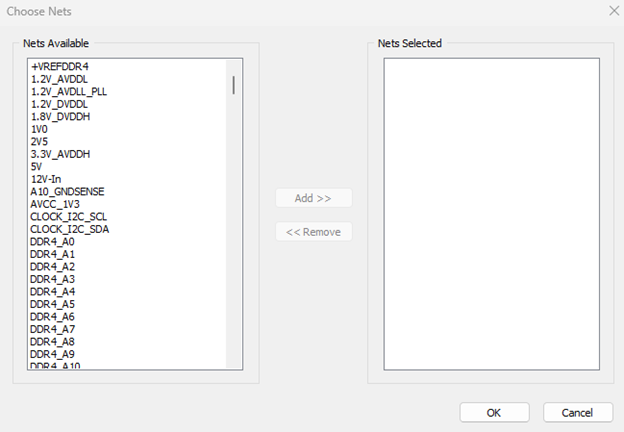

然后,从列表中选择可以连接的网络以创建扩展网络。

图 10:扩展网络:选择要加入的任何网络

另一种手动方法是,用户可以通过以下方式创建扩展网络:从 Single Ended 选项卡中选择单个网络,将鼠标移动到显示区域,右键单击,然后选择 Create Extended Net。

图 11:构建扩展网络的替代方法

现在,如果用户想将新的扩展网络更改为差分扩展网络,那么用户必须按照前面解释的相同步骤创建差分线。最好的方法是将 _P 和 _N 表示法与新的延长线一起使用,在差分选项卡中自动识别,然后让 SIwave 进行组合。

- 设置求解器

单击 SIwizard 求解器。

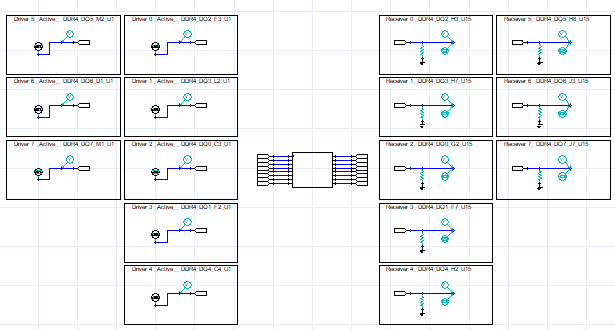

在设置求解器之前,用户需要了解 SIwave 究竟会产生什么。它将在电子桌面中创建电路并完成所有设置。在 SIwave 中,求解器仅计算 s 参数框。然而,它使用用户提供的所有信息在 Electronic desktop 中构建和运行电路。让我们看看这是如何完成的。

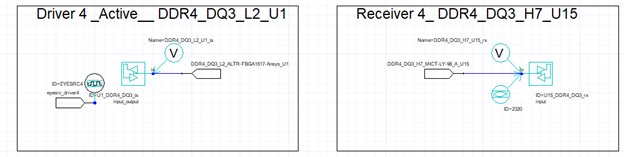

图 12:示意图:使用 Eyesource 和 Eyeprobe

SIwave: DC、PI、SI 或辐射中的任何过程都从选择求解器开始。选择求解器后,SIwave 会生成一个看起来像表单的对话框。用户需要检查表单并填写缺失的信息。

例如,SIwave 使用模型中的所有现有跟踪填充对话框。可以选择一些行或解决所有行。请注意,此处 SIwave 仅选择跟踪。任何被归类为功率平面 SIwave 的东西都不会将其放入表格中。

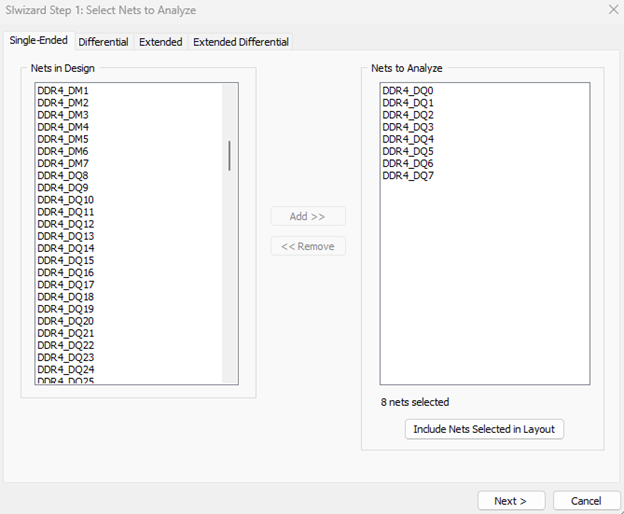

现在,在表中,有四个类别:单一、差异、扩展和扩展差异。确保检查这四个类别并选择跟踪以对它们执行 SI。为简单起见,选择使用 8 条单线。

图 13:选择跟踪

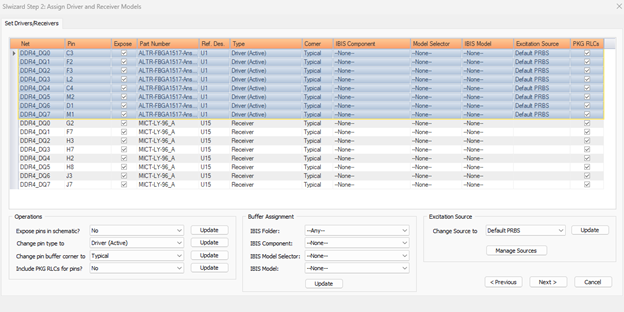

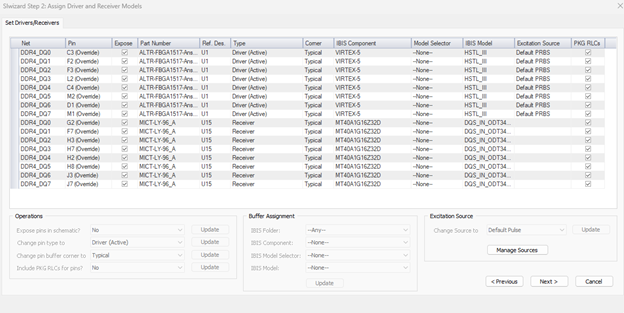

选择下一步以显示 Set Drivers/Receivers 对话框。这些列的含义是什么?

图 14:定义激励:驱动器和接收器

- 第一列是单端网络的名称。即使线路是差分的,SIwave 仍显示单端名称。

- 第二列是第五列 Reference Designator 中提到的 component 中的引脚名称。

- 第三列 Expose 表示用户希望 SIwave 在跟踪的该端放置一个端口。通常,只有连接到分立器件或集成电路的末端会暴露出来。这并不意味着如果两端连接到 R、L 或 C,则它不能暴露。

- 第 5 列是第 5 列的部件号。因此,同一部分可以在电路中多次使用。每个指标都有自己的参考标号,如第 <> 列所述

- 第 6 列,其中用户指定此端是 driver 还是 receiver(如果选中了 expose 选项)。在一端,选择 Driver (驱动程序);另一方面,选择 接收器.此信息将进入 circuit。SIwave 不使用此信息。

- 第 7 列是拐角,即如果用户添加了 IBIS 模型。这些通常与温度和电源电压条件有关。SIwave 在此处根据您的选择选择正确的数据集:Max、Min、...

- 第 8 列是 TX 或 RX 侧的 IBIS 模型。如果选中了一个选项,则用户还必须在第 9 列和第 10 列中指定选项。

- 第 12 列是 PKG RLC。如果您使用的是 IBIS 模型,并且希望将封装的 RLC 包含在 IBIS 模型中,这一点非常重要。

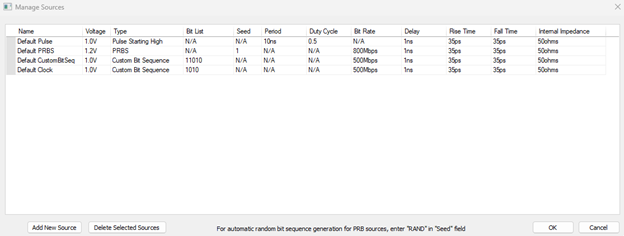

- 第 11 列是信号。用户可以选择 PRBS、clock、step 或随机 RPBS。在此列的正下方,有激发源框。单击 Manage sources(管理源)。请注意这四个选项。

图 15:定义信号

对于每个 API,用户需要指定

- 的电压 DDR4 它是 1.2伏

- 信号的类型,

- 如果是自定义 PRBS 或时钟,则为位列表,

- 种子(在定义 Bytes 时使用),

- 期间,

- 占空比,1 和 0 持续时间之间的比率,

- 比特率 /

- 延迟,

- 上升时间,在 DDR4-3200 中为 35ps

- 下降时间,与上升时间相同,最后

- Driver 的输入阻抗。

请注意,如果用户想要一个随机位序列 PRBS,请在种子字段中输入 RAND。

用户还可以添加更多源,但它们必须是以下四种类型之一:脉冲 PRBS、脉冲起始高电平、脉冲起始低电平或随机位序列。因此,可以添加具有不同数据速率或上升时间的 PRBS 信号。

返回设置 Driver 和 Receiver。有关信号的信息也进入 eye source 和 eye probe 定义中的电路中。

如果用户选择多行,则底部的选项将被激活。所以现在,用户可以一键更改多行。

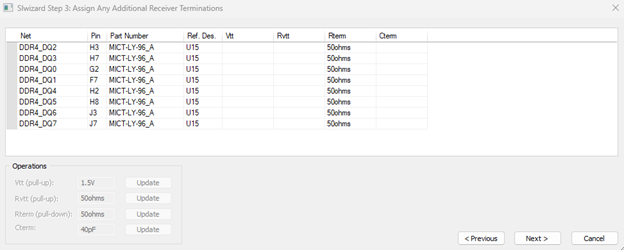

对选择感到满意后,单击 Next 为接收方分配适当的终端:

图 16:定义接收器设置:Vtt 上拉电压。

- 第一列是比赛名称,

- 第二列是引脚号,

- 第 3 列是部件号,

- 第四列是参考指示符,

- 第 2 列是 SDR 应用使用的 Vtt,通常等于 VddQ/<>。它是上拉电压,

- 第 6 列是用于 SDR 应用的 Rvtt,它是上拉电阻器,

- 第 7 列是端接电阻,

- 第 8 列是端接分流电容。

与 SIwave 中的每个对话框一样,如果用户选择多行,则下半部分将被激活。

单击 Next。

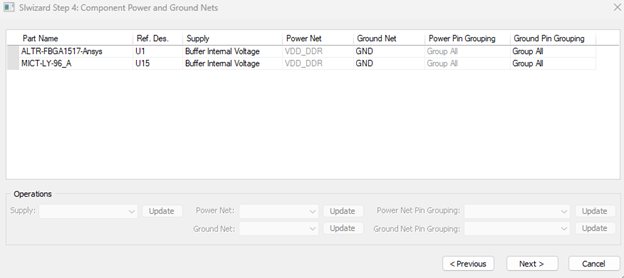

以下对话框是 power plane 设置。在此对话框中,用户可以调整电源网络,为输入或输出处的走线中使用的元件供电。用户通常不需要更改任何内容,因为 SIwave 会填充所有条目。

图 17:电源平面设置

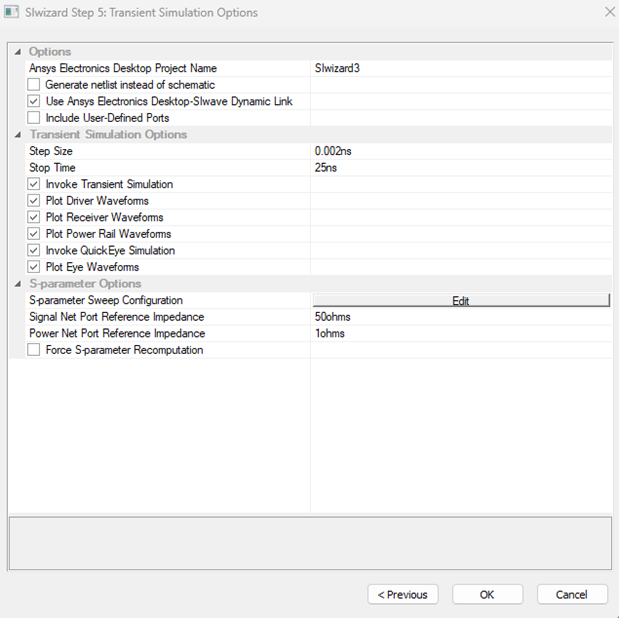

最后一步是求解器。

图 18:求解器设置

- 在第一行中输入解决方案的名称:SIwizard with no IBIS models。

- 在第二行中,如果选中,则 SIwave 不会生成原理图。

- 第三行,如果选中,SIwave 将在电子桌面中生成原理图。

- 第四行,如果用户希望 SIwave 包含用户定义的端口。这些端口是用户在 SIwizard 外部生成的,并希望它们包含在 s 参数中。类似于电源平面端口的接入点。

- 第 1 行是步长,这是最短上升时间的函数;5/<> 是最大值

- 第 6 行是 Stop time (停止时间);通常,它是最长结构的函数。第 5 行和第 6 行用于瞬态求解器的定义。

- 第 7 行强制电子桌面中的瞬态求解器进行求解

- 第 8 行、第 9 行和第 10 行用于绘制结果。

- 第 11 行用于调用电子桌面中生成眼图的快速眼图求解器。

- 第 12 行是在完成快速眼睛求解器后绘制眼睛。同样,电路中使用了 11 号线和 12 号线。

- 第 13 行用于 SIwave 中的 s 参数求解器。SIwave 只对 s 参数进行求解。瞬态和快速眼是在电子桌面中完成的。

- 第 14 行和第 15 行用于确认 s 参数端口的参考阻抗。

。

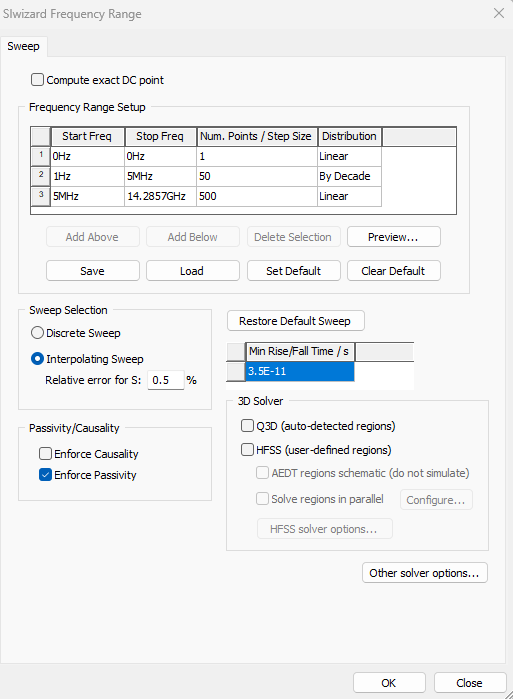

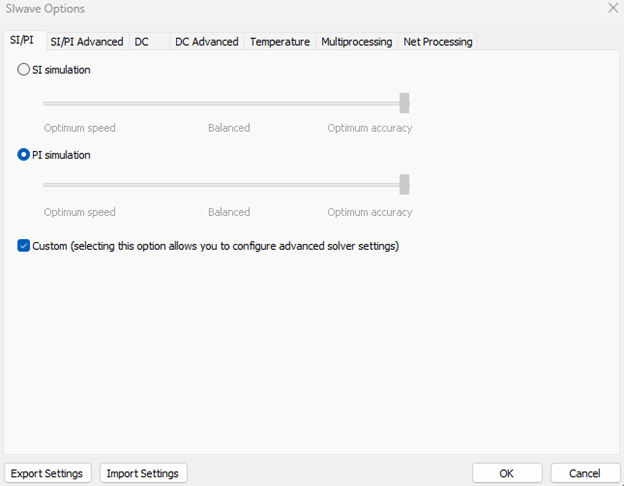

在第 13 行中,如果用户单击 edit(编辑),则会弹出 SYZ 求解器中解释的 s 参数求解器。请在此处观看 PI 求解器的视频,了解有关设置的更多信息。应该注意,最大频率与最小 Rise/Fall 时间有关。此外,请注意,如果用户单击其他求解器选项,则存在更多选项。

图 19:S 参数求解器设置

图 20:精度与速度设置

返回 transient solver 设置,然后按 OK

添加 IBIS 模型并使用 IBIS 模型将解决方案 SIwizard 命名为 SIwizard 后,重复相同的步骤。这样,用户就可以看到两者之间的区别。

- 解决 方案

- 瞬态解决方案

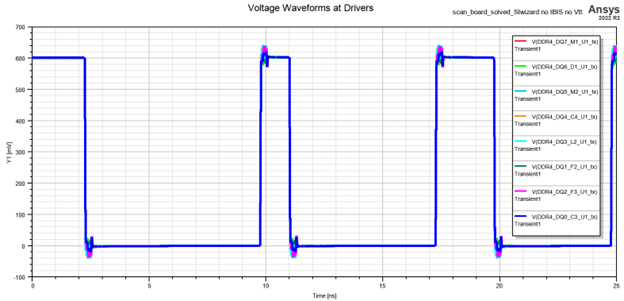

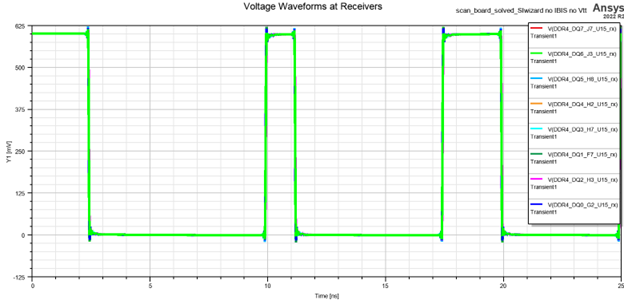

第一个结果来自瞬态求解器。瞬态求解器绘制用户要求的内容,当然,对于所选走线,Driver 和 Receiver 处的电压。请注意,在图中,p-p 电压是 1.2 伏特的一半。这是因为该电路充当电源和负载之间的功率分压器。因此,在设置中,始终输入两倍的电压。

图 21:瞬态响应 PRBS 信号

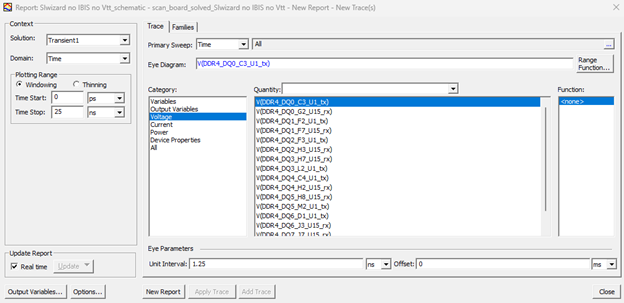

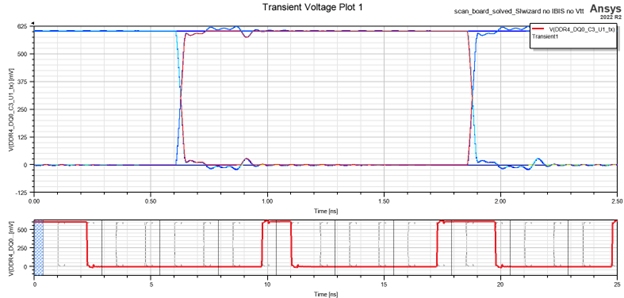

如果用户没有进行眼图分析的许可证,则用户始终可以使用瞬态求解器生成眼图。执行瞬态操作后,选择 Results->Create eye diagram report->Rectangular plot-。将解决方案保留在 Transient 上,但将单位间隔更改为 1 位的间隔。

图 22:从瞬态求解器生成眼图

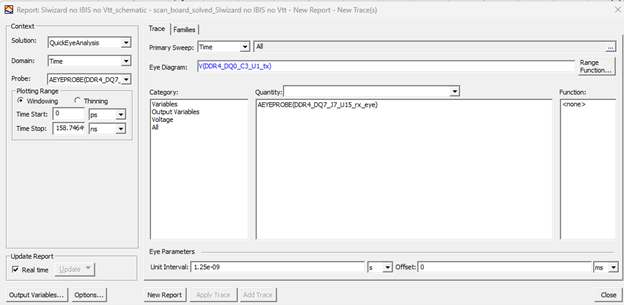

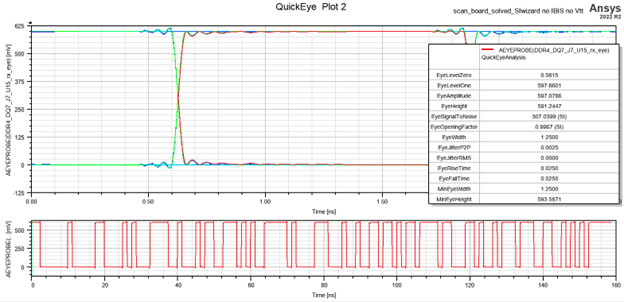

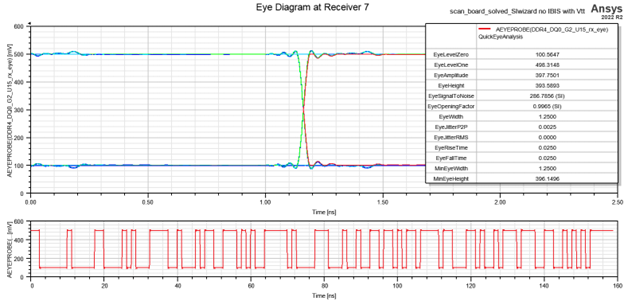

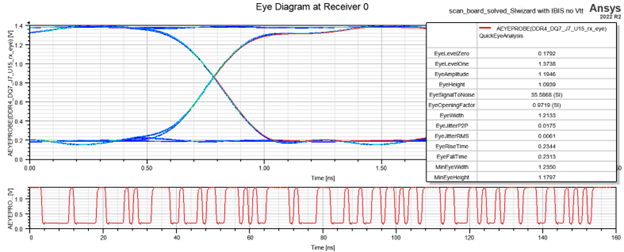

- Quick Eye 解决方案

第二个结果来自 Quick Eye。用户可以从快速眼图求解器中绘制三种类型的眼图。请注意,需要选择要绘制的探针。

- 结果->创建眼图报告->矩形图

- 可以添加眼睛信息和度量

- 是时间间隔的函数

- 显示信号形状的 10 倍于 Transient 求解器中指定的周期。

- 添加掩码:双击图形,再次选择 Mask (掩码)、Edit(编辑)、Edit(编辑),然后在电压和时间中输入掩码。

图 23: 结果->创建眼图报告->矩形图

图 24:眼图:结果->创建眼图报告->矩形图

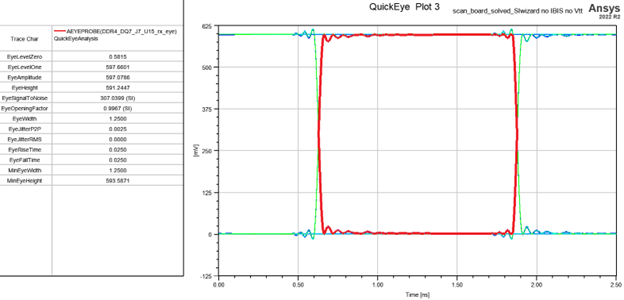

- 结果->创建 眼图 报表-> 堆叠眼图:

- 可以添加眼睛信息和度量

- 是时间间隔的函数

- 无法添加蒙版

- 眼睛测量值在侧面自动生成

图 25:眼图:结果->创建眼图报告->堆叠眼图图

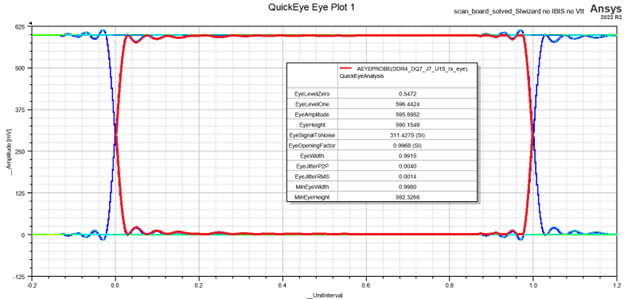

- 结果->创建统计眼图 - >统计眼图

- 可以添加眼睛信息和度量

- 是单位间隔的函数

- 可以添加所有眼睛信息

- 可以添加掩码:双击图表,再次选择 Mask, Edit, Edit,然后以电压和单位间隔输入掩码。

图 26:眼图:结果->创建统计眼图 - >统计眼图

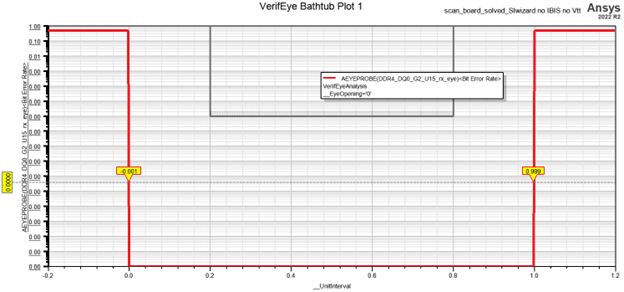

- Verify Eye 解决方案

如果用户添加了 Verify Eye 求解器,则第三个结果可用。然后,用户可以绘制 Bathtub 结果。用户可以从浴缸中确定特定 BER 的眼宽。只需选择 y 标记并将 y 值设置为所需的 BER。

Results->Create Standard Report->Rectangular Plot->Bathtub

- Can add a Y-marker to detect the eye-opening at any level (the Y-axis is the BER level)

- Can also add a limit line

Figure 27: Eye Bathtub from VerifyEye

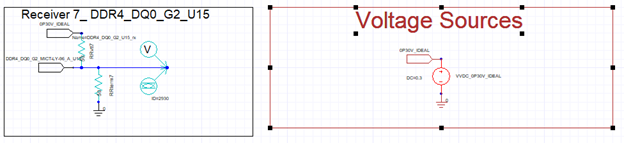

- Vtt 模型

将 Vtt 和 Rvtt 添加到设置中。如前所述,当您没有 IBIS 模型并且迹线用于 SRD 而不是 DDR 时,会使用此设置。电路如下所示。

图 28:原理图:使用 Eyesource 和 Eyeprobe 和 Vtt 电路

这就是结果。完全不同。

图 29:眼图:结果 - >创建 眼图 报告 - >矩形图

- IBIS 模型

添加 IBIS 模型后,电路将更改为在 Ansys 电路中包含 IBIS 组件。请注意,对于这些组件,用户仍然需要拥有 eye source 和 eye probe。

图 30:在激励定义中输入 IBIS 模型

如果用户想要使用 Quickeye 和 Verifyeye 解算器,则眼睛源和眼睛探针就在那里。但是,Eyesource 内部的设置是错误的,因为它没有被使用。有关信号的所有信息都来自 IBIS 模型。

图 31:原理图:使用 IBIS 模型

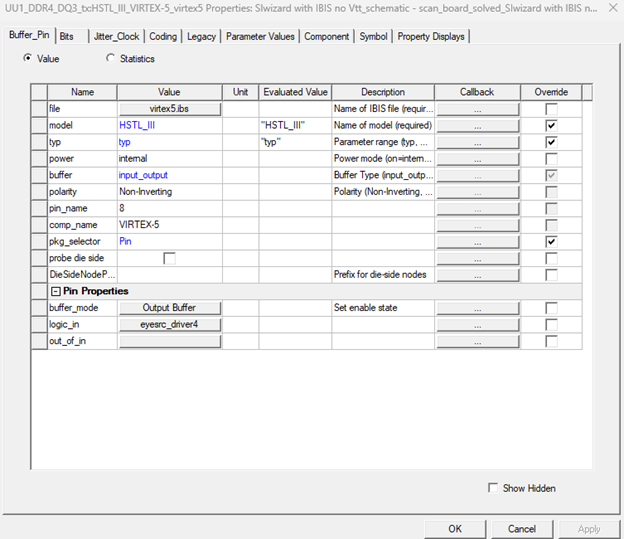

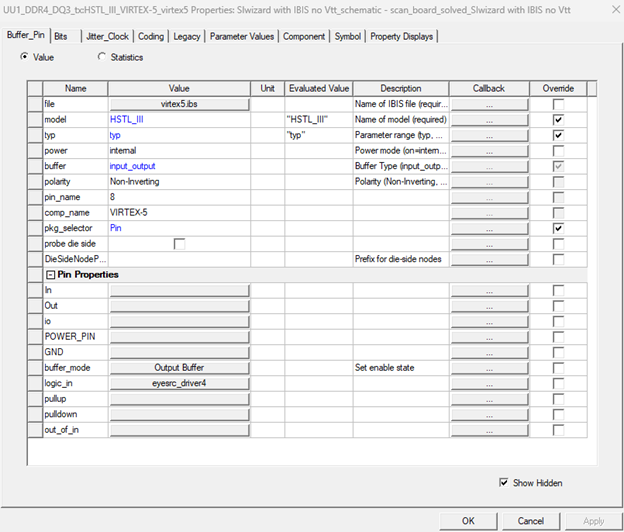

打开 IBIS 模型的对话框。

图 32:IBIS 模型对话框

- 文件名

- 文件名中使用的模型,在本例中选择 HSTL (high-speed transceiver logic)

- 键入角:是 typical、min、max 还是其他任何内容?这些是 IBIS 文件中的选项。

- 电源来自 IBIS 文件本身,而不是来自 Eyesource(内部)

- Buffer:输入 Rx、输出 Tx 或输入-输出。记录在 IBIS 文件中,用户无法更改它。对于 input-output,则在下面的 buffer_mode中,用户必须指定哪一个:input 或 output。

- 极性,反相或非反相

- 文件中的 Pin-name

- 组件名称

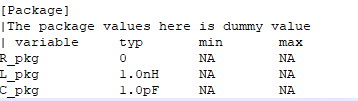

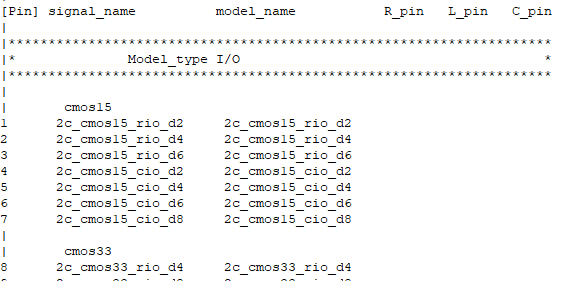

- 封装选择器(Pin/Package/None):在 IBIS 文件中,有两个部分,[Package] 部分和 [PIN] 部分。Package 具有传统的 R_pkg、 L_pkg 和 C_pkg。Pin 1 是 pin 名称的列表

- 探针芯片侧:

- Die Side Node Prefix(晶片侧节点前缀):如果晶粒引脚的名称中包含任何前缀。

- Buffer_mode:当缓冲区为 input-output 时使用。

- Logic_in 以用户输入 Eyesource 引脚的名称。如果设置为 internal,则用户需要转到 Bits 选项卡并输入信号的定义。

- Out-of-in(输出输入):

图 33:IBIS 文件:[package] 和 [pin] 部分

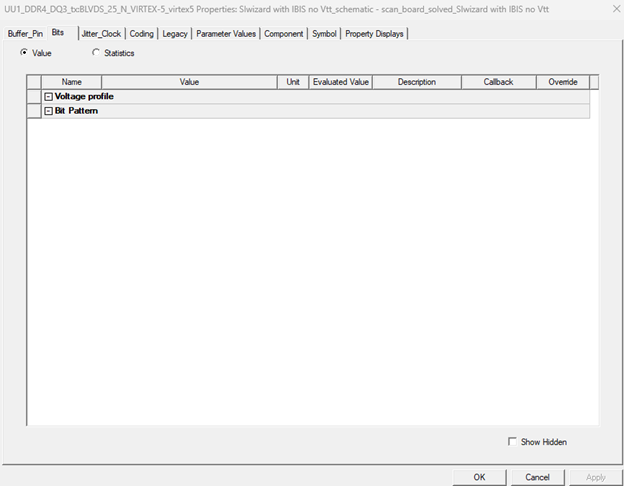

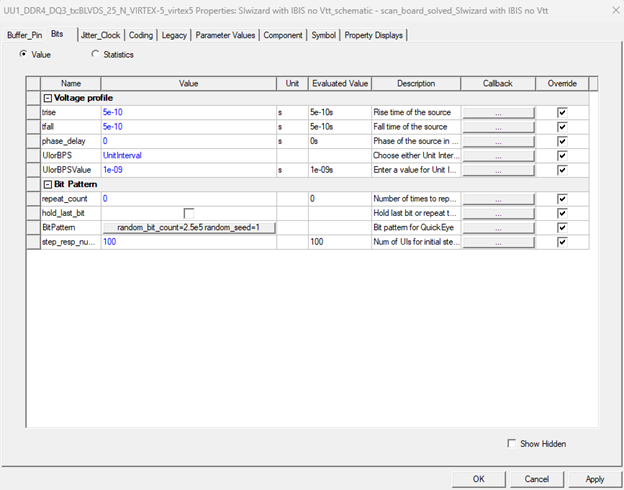

如果用户选择使用内部源而不是 eye 源,则 Bits 选项卡中会出现一个类似于 eye 源中的对话框。

Figure 34: Bits tab with and without Eyesource

If the IBIS file has more options, then activate show hidden, and the user can have more items to select.

图 35:具有更多选项的 IBIS 模型对话框

结果如下:

图 36:使用 IBIS 模型:结果 - >创建眼图报告 - >矩形图