Xilinx IP核(3)XADC IP核

文章目录

- 1. XADC介绍

- 2.输入要求

- 3.输出

- 4.XADC IP核使用

- 5.传送门

1. XADC介绍

xadc在 所有的7系列器件上都有支持,通过将高质量模拟模块与可编程逻辑的灵活性相结合,可以为各种应用打造定制的模拟接口,XADC 包括双 12 位、每秒 1 兆样本 (MSPS) ADC 和片上传感器。其中12位指的是ADC转换的精度,1MSPS说的是采样速率。如图所示,是XADC在FPGA内部电路的逻辑示意,注意区别于IP核形成的电路。

1.图中1部分是温度传感器和电压传感器,可监测如图所示的多组电压。

1.图中1部分是温度传感器和电压传感器,可监测如图所示的多组电压。

2.图中2部分是FPGA bank上的引脚。可以用来接模拟源,总共有17对差分组。其中VP-0与VAUXP有所区别,VP-0在不用来接模拟源时要接地,VAUXP在不用做模拟时,可与普通的数字IO一样使用。支持模拟输入的 FPGA I/O 在封装文件名中包含_ADxP_ 和 ADxN 标识,例如 IO_L1P_T0_ AD0P 35 是模拟辅助通道 VAUXP[0] 的输入引脚。 IO_L1N_T0 AD0N _35 为模拟辅助通道 VAUXN[0] 的输入引脚。Kintex-7 设备不支持辅助通道 6、7、13、14 和 15。可以在 I/O 组中启用任意数量的辅助模拟输入,并将剩余的用作数字 I/O。如果一个组中混合有模拟和数字 I/O,则该 I/O 组必须由满足所用数字 I/O 标准规范所需的电源供电。在这种情况下,模拟输入信号不应超过 I/O Bank 电源电压 (V CCO )。

3.图中3部分是ADC部分所需的模拟电压的基准源,可以选择外部基准源,基准源电压是1.25V,也可以选择内部基准源,这时VRE管脚要接地。

4.图中4部分是两个12位精度的ADC模数转换器。其中ADC A接内部的温度、电压传感器,ADC B主要接外部输入的模拟源。

5.图中5部分是对外的接口,可以使用JTAG或者FPGA内部逻辑通过访问DRP接口来读写内部的控制寄存器和读取状态寄存器。

2.输入要求

ADC 的标称模拟输入范围为 0V 至 1V。在单极模式(默认)下,当输入电压为 1V 时,ADC 的模拟输入会产生FFFh (12 位)的满量程代码。在双极性模式下,ADC 使用二进制补码编码,并在 +0.5V 输入时产生7FFh的满量程代码,在 –0.5V 输入时产生800h的满量程代码。

如下图所示,是xilinx推荐的模拟源的外部电路示意。阻器 R1 和 R2 将 10V 电源分压至 1V,以便与 XADC 配合使用。 R5 已与 R1 和 R2 的并联电阻进行阻抗匹配。模拟输入是高阻抗差分输入。差分输入方案可以抑制任何外部应用的模拟输入信号上的共模噪声。由于每个输入(例如 V P和 V N )的高阻抗,输入交流阻抗通常由传感器、驱动电路的输出阻抗或其他外部组件确定。

3.输出

基于上述的了解,我们得出结论,配置好电路之后,AD转换之后的结果将会存在相应的寄存器中。然后通过专用的引脚去读寄存器就可以了。如图所示,温度传感器的寄存器地址为00h。但是温度需要一个转换的过程,例如读出的ADC采样的值为997h,他所对应的值应该是25℃。因为要符合用以下公式转换。

需要注意,读出的寄存器位宽16bit,但只有12bit数据有效,12 位数据对应于 16 位状态寄存器中的 12 个 MSB(最高有效位)。

DRP时序

如果DWE为逻辑低,则执行DRP读操作。当 DRDY 变高时,该读操作的数据在 DO 总线上有效。因此,应使用 DRDY 来捕获 DO 总线。对于写操作,DWE 信号为逻辑高电平,DI 总线和 DRP 地址 (DADDR) 在 DCLK 的下一个上升沿被捕获。当数据成功写入 DRP 寄存器时,DRDY 信号变为逻辑高电平。在 DRDY 信号变低之前,无法启动新的读或写操作。

4.XADC IP核使用

可以使用原语来读取ADC转换后的值,也可以使用IP核。本文实现使用XADC IP核读取FPGA内部温度。

- A.选择DRP接口,如果不需要读出具体的AD转换之后的数值,则选择none;IP核的实际电路比上述XADC的电路多了AXI-Lite用于配置寄存器。在没有软核和PS端时,用DRP更为方便。

- B.选择连续采样模式,包括了电压采集和电压转换两个阶段。在连续采样模式下,ADC 在当前转换周期结束时自动启动新的转换。在事件采样模式下,您必须在当前转换周期结束后使用 CONVST 或 CONVSTCLK 输入启动下一次转换,适用于精准时刻采集。

- C.通道选择,这里选择单一通道,只工作在单一通道监测温度即可。° Simultaneous Selection允许同时监测两个通道。° Independent ADC独立监视外部通道,同时监测温度和电压。Channel Sequencer 任意监视多个通道。

其余关于DRP的配置、是否勾选AXI-Stream、以及复位信号的选择保持默认即可。

第二页配置一些ADC的增益、补偿、没有深入研究,保持默认。Alarms页配置相关通道的报警信息,本次演示不需要,只看到温度值即可,这里不勾选。由于前面选了单一配置,这里channel页也无需配置直接生成IP即可。

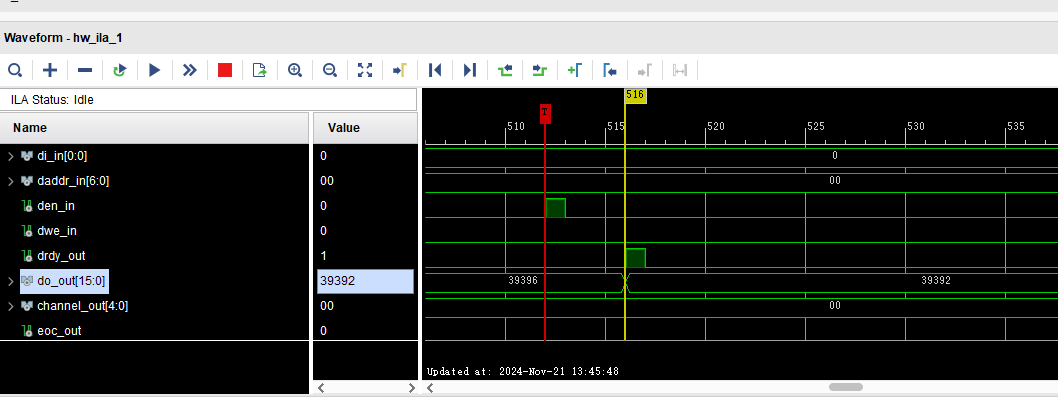

如下图所示为实测结果,在den_in有效时向地址为0的寄存器下发读取指令,在drdy_out为高时,do_out输出有效,可以看到寄存器中16bit的值为39392,右移4为的值2462带入上述温度转换的式子得到当前FPGA温度值为29.77摄氏度。

部分代码如下,有每个引脚含义的注释可供参考

reg [31:0]tim_cnt;

always @(posedge clk_100 or negedge clk_rst) begin

if(!clk_rst)begin

tim_cnt <= 0;

den_in <= 0;

end

else begin

den_in <= 0;

tim_cnt <= tim_cnt + 1;

if(tim_cnt == 32'd100_000_000)begin

tim_cnt <= 0;

den_in <= 1;

end

end

end

xadc_wiz_0 xadc_fun (

.di_in(di_in), // Input data bus for the dynamic reconfiguration port (DRP).

.daddr_in(daddr_in), // input wire [6 : 0] daddr_in

.den_in(den_in), // Enable signal for the dynamic reconfiguration port.

.dwe_in(dwe_in), // Write enable for the dynamic reconfiguration port.

.drdy_out(drdy_out), // Data ready signal for the dynamic reconfiguration port.

.do_out(do_out), // Output data bus for the dynamic reconfiguration port.

.dclk_in(clk_100), // input wire dclk_in

.reset_in(~clk_rst), // input wire reset_in

.vp_in(vp_in), // input wire vp_in

.vn_in(vn_in), // input wire vn_in

.channel_out(channel_out), // Channel selection outputs. 只是正在采样的通道

.eoc_out(eoc_out), // End of Conversion signal.

.alarm_out(alarm_out), // output wire alarm_out

.eos_out(eos_out), // End of Sequence

.busy_out(busy_out) // ADC busy signal

);

5.传送门

- 我的主页

- FPGA开发必备技能专栏汇总导航

| END |

💎文章原创,首发于CSDN论坛。

💎欢迎点赞💖收藏✨打赏💷!

💎欢迎评论区🎤或私信指出错误🎤,🗣️提出宝贵意见或疑问。