一种基于动态部分重构的FPGA自修复控制器

1.FPGA动态部分重构技术

动态部分重构技术指在FPGA运行时,通过加载部分位流文件来修改FPGA可重构区域中的逻辑设计,修改过程中其余逻辑功能不受影响整个系统也能够持续运行。

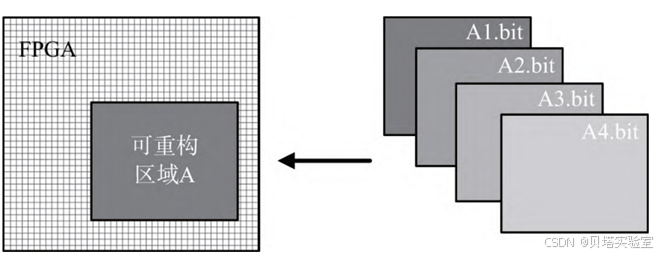

下图为FPGA动态部分重构的基本原理图。通过下载A1.bit、A2.bit、A3.bit 或A4.bit 中任一位流文件,可以修改可重构区域A 中的逻辑功能。FPGA设计中的逻辑可分为静态逻辑和可重构逻辑,图中密集方格区域中的逻辑为静态逻辑,区域A中的逻辑为可重构逻辑。当系统加载部分位流文件时静态逻辑保持运行状态,而可重构逻辑由部分位流文件的配置信息代替。

FPGA动态部分重构技术可以通过有限的硬件资源实现FPGA内部逻辑的动态实时多路复用。

2.基干动态部分重构的FPGA自修复控制器设计

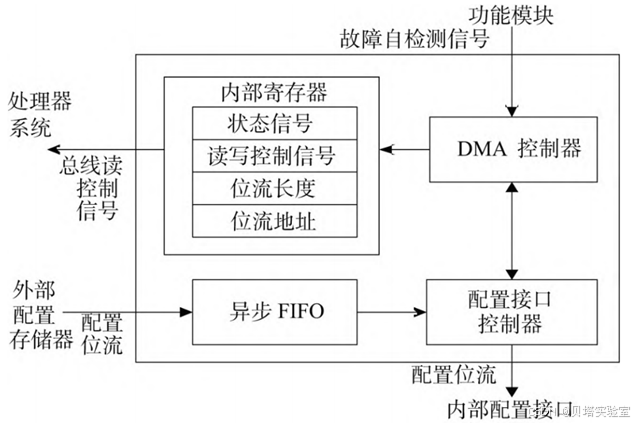

介绍一款基于AXI总线协议设计了FPGA自修复控制器,如下图所示。当接收到功能模块发出的故障自检测信号后,根据所需配置位流的大小和地址信息,通过DMA控制器生成对应的总线读控制信号送入处理器系统。经过处理器系统的接口协议转换后,DMA控制器读取外部配置存储器中指定地址和长度的配置位流并传输到内部的异步FIFO中,再经过配置接口控制器将配置信息传输到内部配置接口,完成对FPGA动态部分重构。

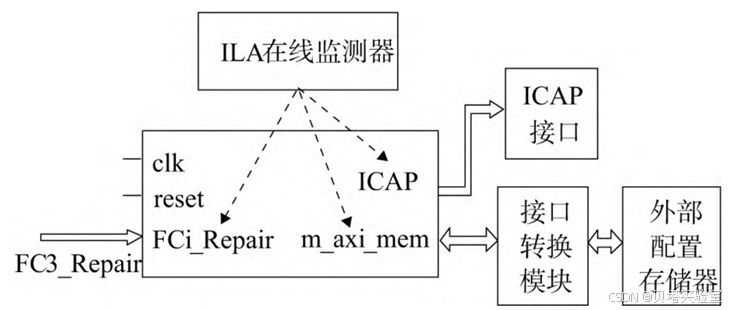

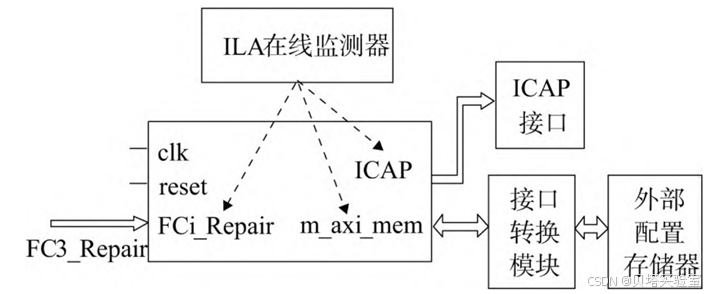

顶层电路如下图所示,其中FCi_Repair表示系统中功能模块FCi的故障自检测信号。

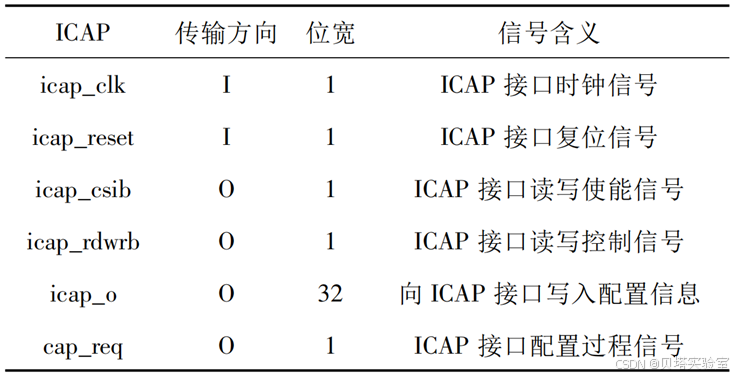

下表为自修复控制器与ICAP接口之间的通信信号,主要用于自修复控制器对ICAP接口的配置控制将配置信息写入ICAP接口并返回重构过程信号。

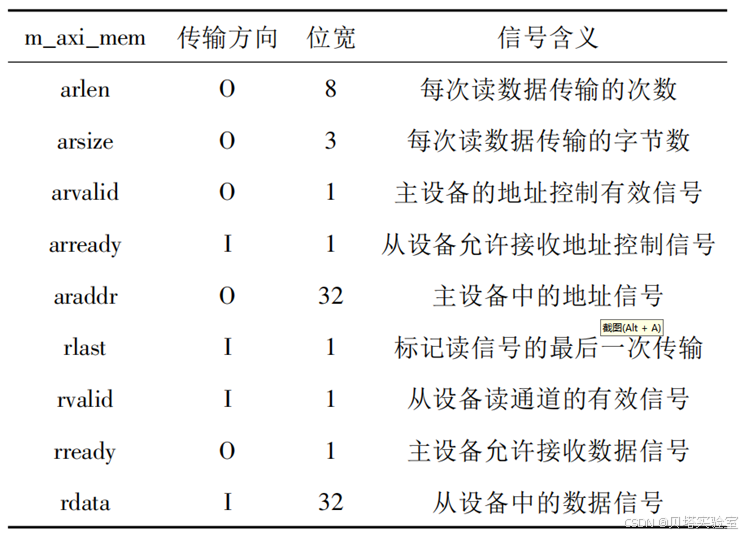

下表为自修复控制器与外部存储器通信的AXI总线读控制信号。

3.电路验证方案

上图为自修复控制器的电路验证实验方案图,将自修复控制器与ICAP接口、接口转换模块和外部配置存储器相连接手动触发系统功能模块FC3的故障自检测控制信号,通过用FPGA的内嵌逻辑分析仪ILA观察自修复控制器的位流配置过程。其中,自修复控制器工作时钟频率和ICAP接口时钟频率为100MHz采用DDR3芯片作为外部配置存储器进行实验。

4.电路结果

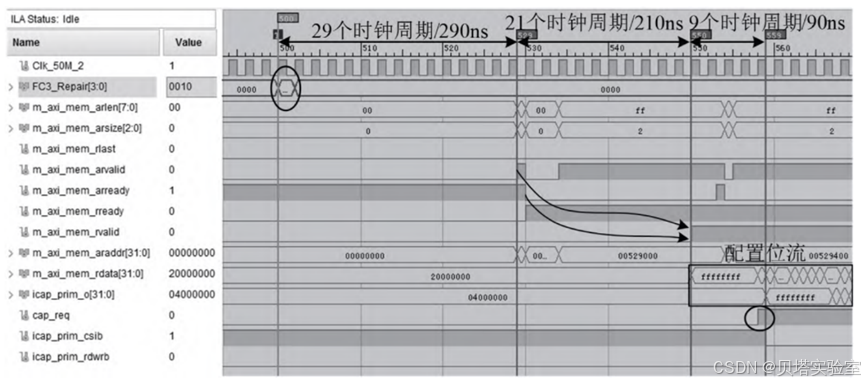

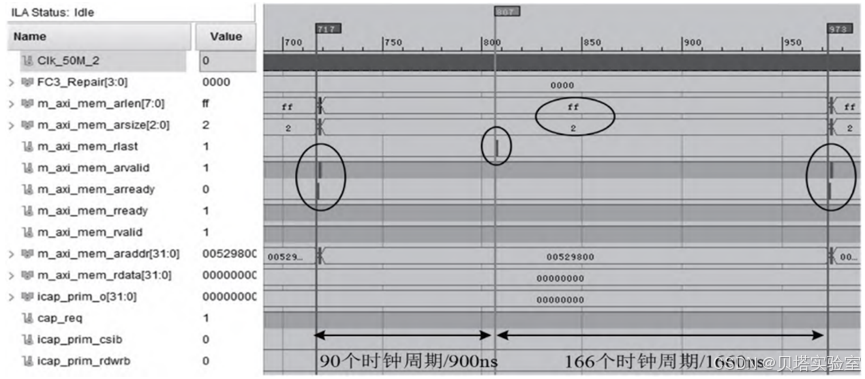

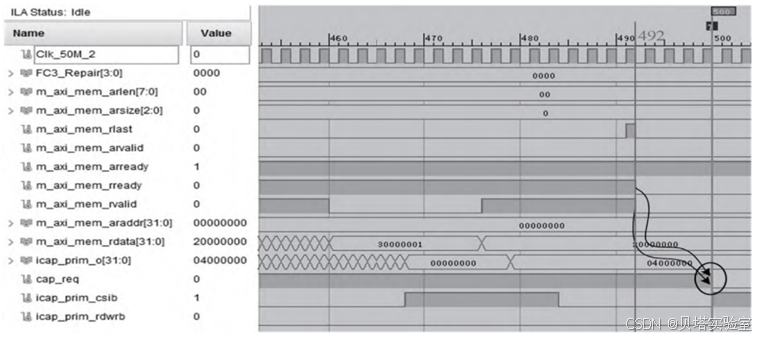

如图所示在ILA监测窗口的第500个监测点处捕获到功能模块FC3的故障自检测信号,290ns后,自修复控制器开始工作,地址控制有效信号arvalid被拉高有效,同时读控制信号arlen、arsize和地址信号araddr准备传输。10ns后arvalid 和 arready(低有效)同时被拉低,存储器等待接收地址/控制信号,rready拉高有效自修复控制器允许接收存储器配置数据。40ns后,自修复控制器拉高地址控制有效信号arvalid,开始向存储器发送配置位流的地址信号。在第550个监测点时存储器向自修复控制器发送读通道的有效信号rvalid,配置位流开始读入,经过自修复控制器内部32位的异步FIFO向ICAP接口传输。当cap_req信号拉高后,配置信息开始从异步FIFO传输到ICAP接口功能模块开始重构。图中可以看出从自修复信号触发到数据配置到ICAP接口,一共经历了59个时钟周期。

如上图所示在第717个监测点时,自修复控制器和存储器完成一次握手,开始向存储器传输地址信号,持续900ns后读信号的最后一次传输标记rlast被拉高,存储器向自修复控制器输送地址段对应的数据流,直到第973个监测点时,一个地址段的数据传输完成,开始传输下一地址段数据。由arlen和arsize可以看出每个地址段传输一共读了两次数据,每次读了255个字节的数据,历时256个时钟周期共2560ns,可以计算出100M工作频率下,重构速度约为200bit/ms。

上图所示在第492个监测点时ready和rvalid信号同时拉低,自修复控制器不再发送地址和读控制信号,也不再向ICAP接口传输配置信息。80ns后自修复控制器拉低cap_reqg 信号重构自修复完成。

5.性能分析

5.1可靠性

评价系统可靠性的定量测度称为可靠度,可靠度指系统在t时刻正常工作的条件下,在时间区间[t0,t]内能正常工作的概率常用 R(t)表示。若一个模块的失效率为常数λ,则它的可靠度为

R(t)=e-λt

对于一个可维修的系统,它的平均寿命可以用系统的平均无故障间隔时间TMTBF(mean time between failures,MTBF)来表示[即可靠度R(t)的均值表达式如下:

![]()

对于一个不可维修的系统,它的平均寿命可以用系统的平均无故障运行时间MTTF(mean time to failures,MTTF)来表示,MTTF和MTBF表达式完全相同,只是针对不同类型系统的可靠性表达方式。

采用本文自修复控制器的系统与故障自检测电路的设计方式相关,当系统采用时间余自检测电路时,该自修复控制器可靠性与回读刷新及定时刷新相同,设刷新可修复率为μ,则配置刷新的可靠性可以表示为

![]()

可以计算出三模余的可靠性为

![]()

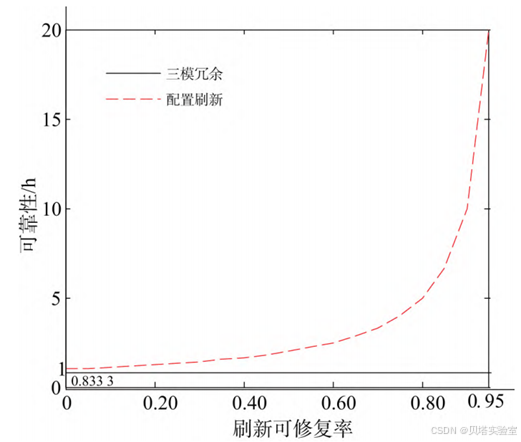

以失效率λ=1x10-6/h刷新可修复率为μ∈[0,1]为例绘制如下图所示的可靠性MTTF/MTBF对比分析图。由图可知,配置刷新法的可靠性MTBF都随μ增大而快速提升且始终高于三模冗余。

5.2硬件资源消耗

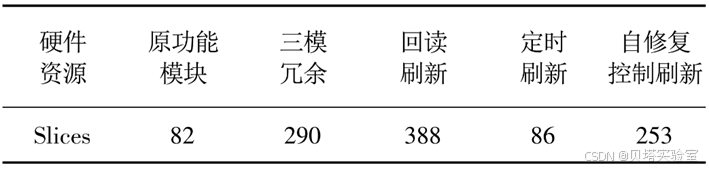

以32位流水线乘法器功能为例分别对三模冗余、回读刷新、定时刷新和采用自修复控制器的配置刷新进行硬件资源消耗对比。如下表所示,采用自修复控制器的配置刷新资源消耗是定时刷新法的2.94倍,较三模冗余法减少了12.76%,较回读刷新法减少了34.79%。

5.3时间消耗分析

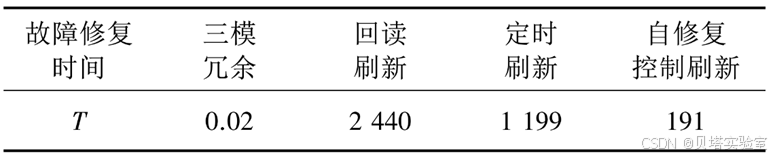

设系统的工作时钟周期为Tclk,重构时钟周期为Treclk部分配置位流的大小为Nbit(字节)则本文应用系统的故障修复时间为5Tclk+58Treclk+(Nbit/200)μs,物理实验中取Tclk =50MHz,Treclk =100MHz。基于zynq7020系SOC芯片其中最小重构单元即一帧位流的大小为Nbit =37381个字节,全局位流大小为151484个字节,可以计算出一次故障修复时间约为190.84μs。下表为一次故障的修复时间对比分析表,可见在配置刷新中,基于动态部分重构的配置刷新最快只需要191μs,实验中较回读刷新法减少了92.17%,较定时刷新法减少了84.07%。