PCB模块化设计11——VGA高速PCB布局布线设计规范

目录

- PCB模块化设计11——VGA高速PCB布局布线设计规范

- 1、什么是VGA?

- 2、VGA接口管脚定义

- 3、VGA电缆究竟是如何工作的?

- 4、VGA参考设计原理图

- 5、PCB设计指南

- 1、R,G,B LAYOUT注意事项

- 2、HSYNC,VSYNC Layout注意事项

- 3、其他注意事项

PCB模块化设计11——VGA高速PCB布局布线设计规范

1、什么是VGA?

说到VGA接口,相信很多朋友都不会陌生,因为这种接口是电脑显示器上最主要的接口,从块头巨大的CRT显示器时代开始,VGA接口就被使用,并且一直沿用至今,另外VGA接口还被称为D-Sub接口。

早前大多数的计算机和外部显示设备的连接还是通过模拟VGA接口进行的,计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。对于模拟显示设备,比如说模拟CRT显示器,信号被直接送到相应的处理电路,驱动控制显像管生成图像;而对于LCD、DLP等数字显示设备,显示设备中需配置相应的A/D(模拟/数字)转换器,将模拟信号转变为数字信号。在经过D/A和A/D这两次转换后,不可避免地造成了一些图像细节的损失。VGA接口应用于CRT显示器无可厚非,但用于连接液晶之类的显示设备,则转换过程的图像损失会使显示效果略微下降。

VGA连接器用于显示设备,用于将计算机连接到显示器,投影仪或电视。

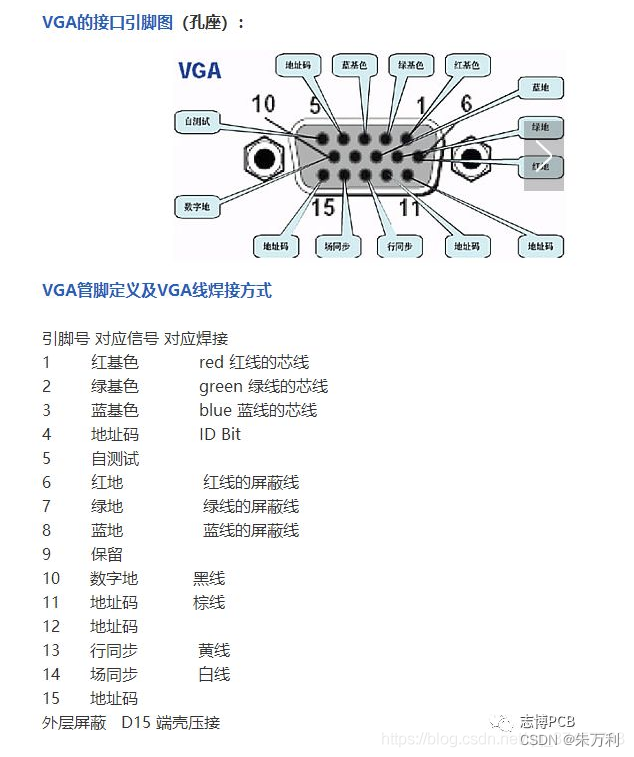

2、VGA接口管脚定义

管脚定义:

3、VGA电缆究竟是如何工作的?

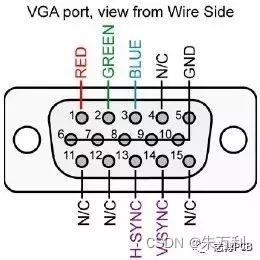

这是一个DE-15 15针连接器(有点像用于RS-232的DB-9连接器,VGA多了一个行):

H-SYNC和V-SYNC代表水平和垂直同步。其余的都是不言自明的。H-SYNC和V-SYNC是数字(TTL)电平信号,低电平有效,彩色信号是模拟信号,0V(黑色)到0.7V(全彩色)。

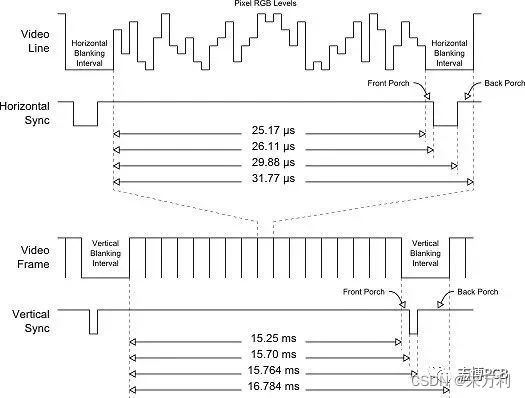

正如H-SYNC和V-SYNC的存在所暗示的那样,存在水平定时和垂直定时。此图显示了640x480 VGA的时序,这是原始VGA格式之一。

如上图所示的水平定时表示屏幕的一行(例如640x480显示器的640个可见像素)。在每行像素数据之间,存在水平消隐区域,其中没有显示视频(这最初主要用于电视中以允许CRT迹线从屏幕的右侧移回到左侧,为下一个准备好线)。

水平同步用于开始每条线的定时。它不像消隐区那么宽。就在水平脉冲之前,有一个称为前沿的延迟。紧接着水平脉冲是另一个叫做后门廊的延迟。

虽然显示了640个像素,但每行实际需要800个像素:水平同步为96,后沿为48,视频为640,前沿为16。

如图所示,每条线长31.77μs。以800像素潜水,每像素39.7 ns。这相当于25.1 MHz的时钟速率。

线条被聚集成帧,显示在图片的底部。与每条线的时序一样,每帧开始时都有一个垂直消隐间隔(这最初主要用于电视机,以允许CRT轨迹从屏幕底部向后移动到顶部,为下一帧做好准备)。在一些较旧的CRT电视机上,有可能将照片“滚动”下来,实际上将这个间隔看作屏幕上的黑条。与线路时序一样,时间有前廊和后廊区域。

尽管显示了480行,但每帧实际需要521行:垂直同步为2行,后沿为29行,可见行视频为480行,前沿为10行。

如图所示,每帧的长度为16.784 ms。这对应于59.5Hz的帧速率。

4、VGA参考设计原理图

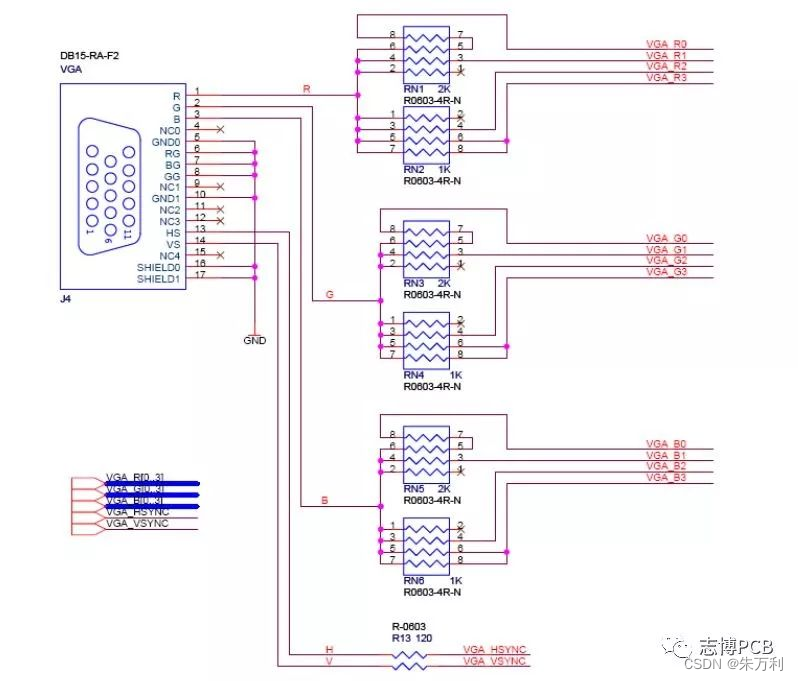

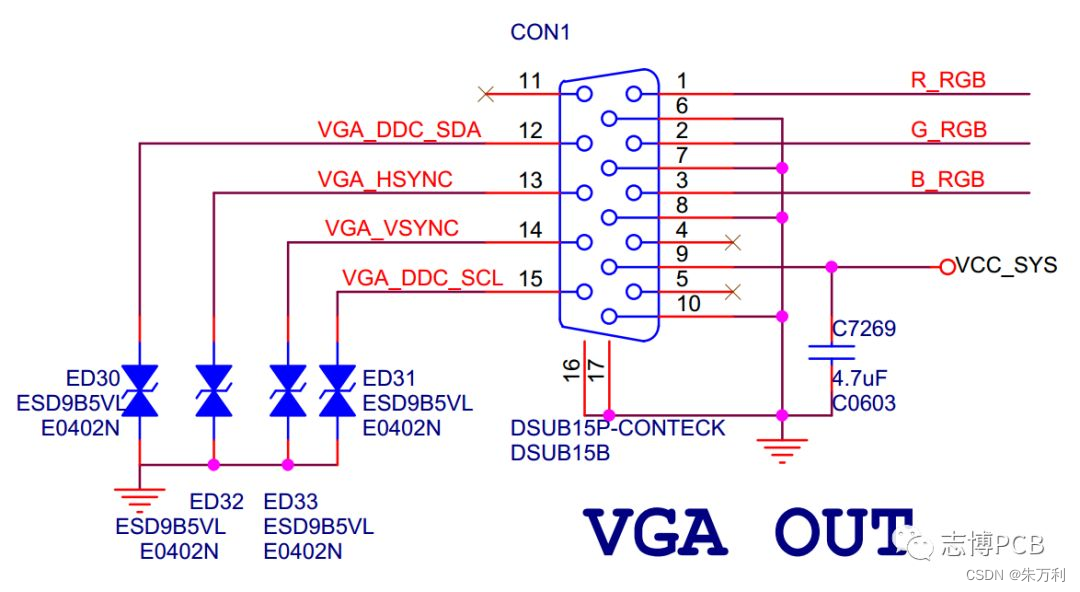

参考一:

参考二:

5、PCB设计指南

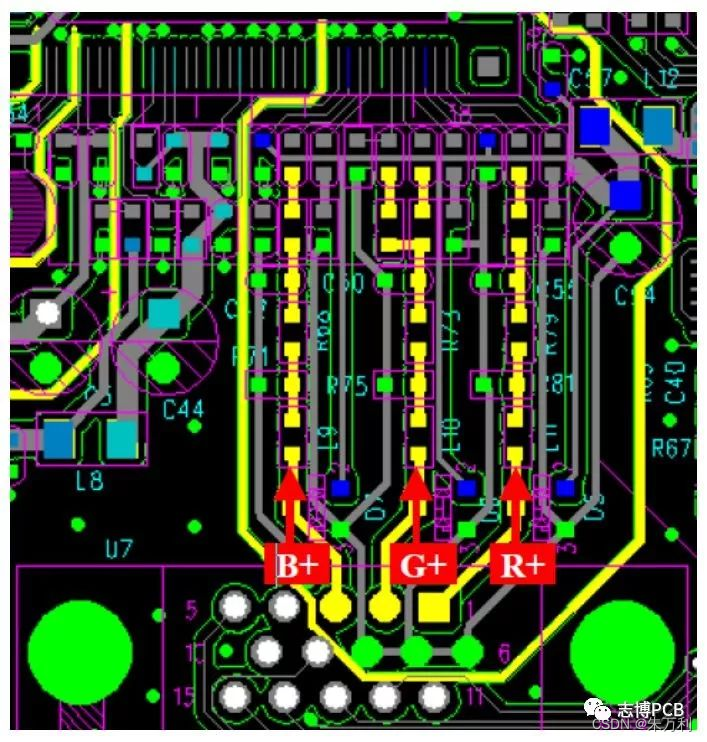

1、R,G,B LAYOUT注意事项

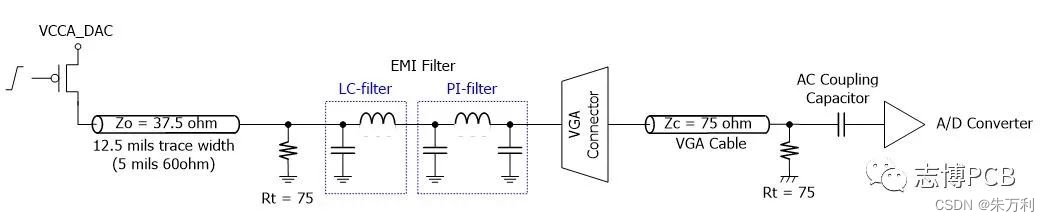

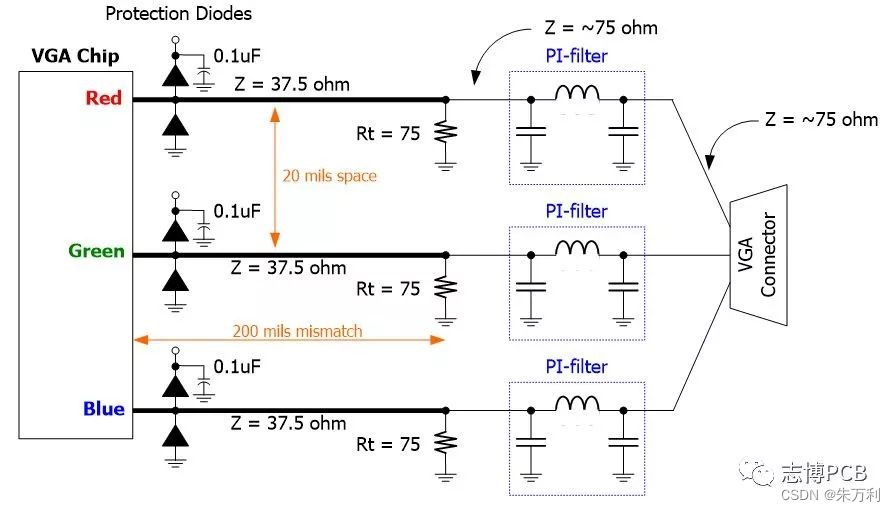

rgb 输出缓冲区为"开源", 每个 dac输出时的等效 dc电阻为37.5。每个通道上也有一个用于降低高频噪声和 emi 的可比滤波器。上图是一个示例。为了最大限度地提高性能, 应匹配滤波器阻抗、电缆阻抗和负载阻抗。

rgb 跟踪应以37.5 的目标阻抗从输出缓冲器路由到75 1% 终止电阻, 然后继续以理想的跟踪目标阻抗75, 一直路由到至少有20英里间距的vga连接器。

rgb信号的长度应尽可能匹配,不应超过200英里的不匹配。用于rgb信号的端子电阻和可滤波器是相同的, 并且可滤波器靠近vga连接器。

rgb信号需要 dac 电源和接地之间的保护二极管。这些二极管的位置取决于dac功率平面。功率导轨与上拉二极管的电感应该是最小的, 以最大限度地提高性能。有关详细信息, 请参见图。

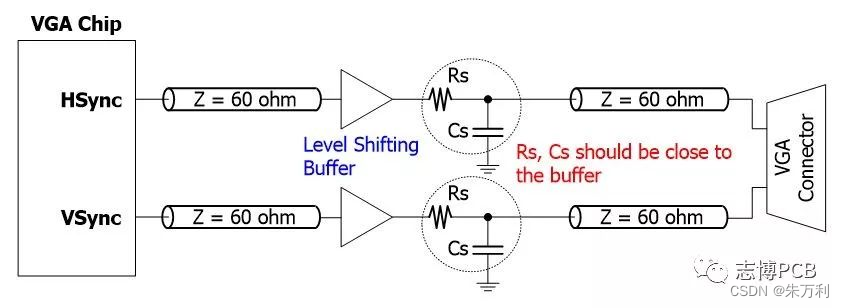

2、HSYNC,VSYNC Layout注意事项

hsync 和 vsync是 vga 芯片的输出或由液位移动设备缓冲的输出, 并且每个电平上都有串联源端接电阻, 如上图所示。r 和 c 应接近水平转移缓冲区。

3、其他注意事项

①:模块化布局操作,电阻电容离VGA接口最少保持1.5mm以上的间距,确保烙铁能方便焊接维修。

②:RGB信号,尽可能加粗,推荐线宽为6-8mil。

③:空间允许情况下对RGB信号做包地处理。

④:线和线之间尽可能满足3W原则。

⑤:VGA前端滤波器应遵循差分布局规则。

⑥:VGA前端滤波器靠近D-SUB连接器。

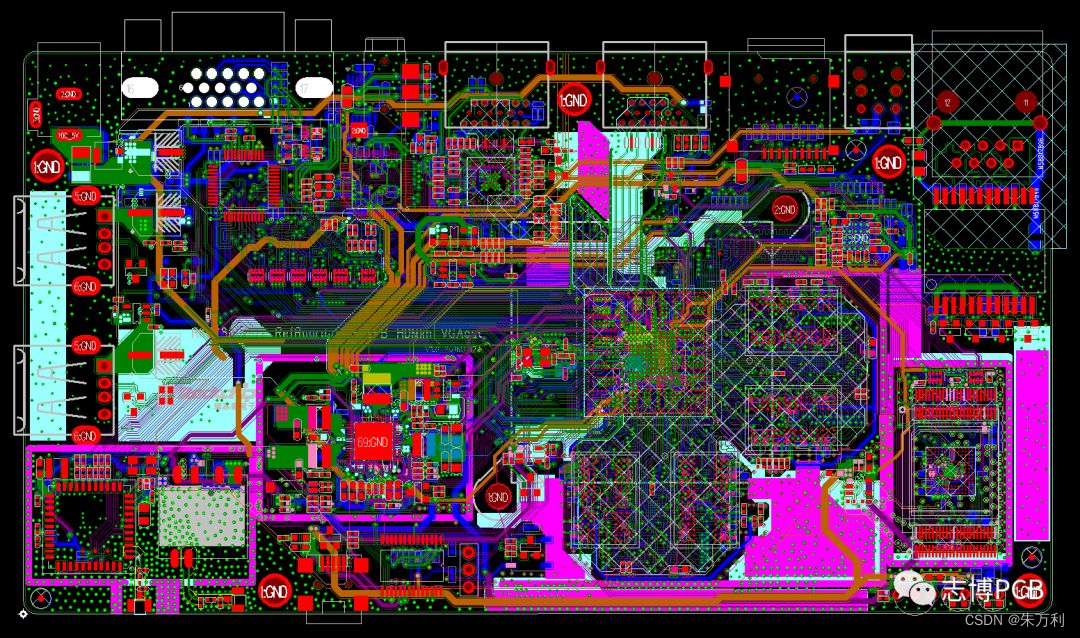

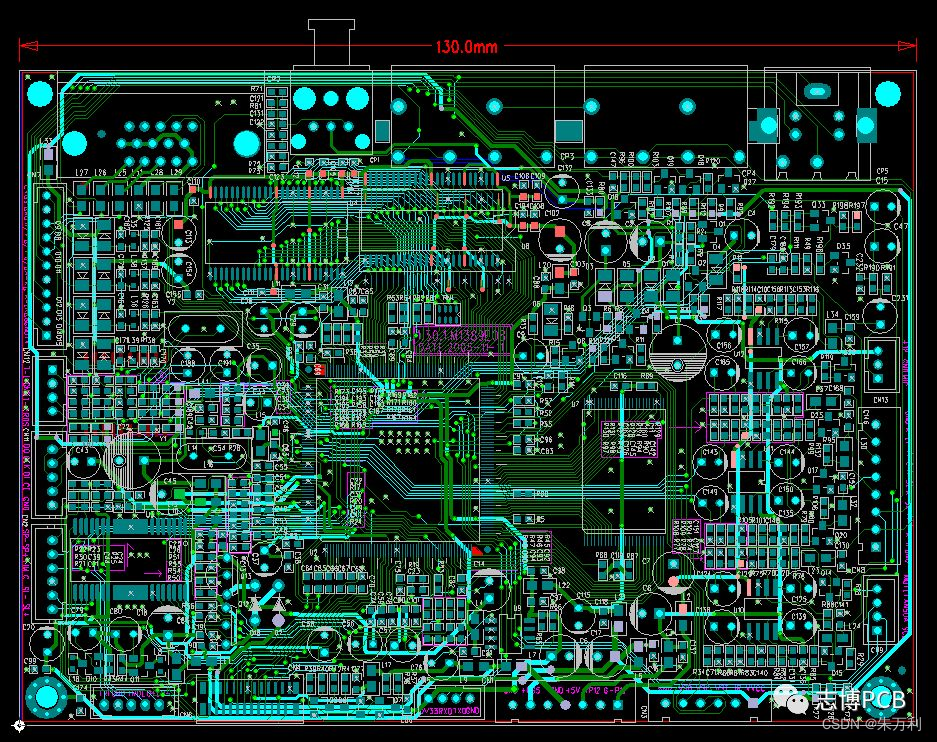

1、工控主板

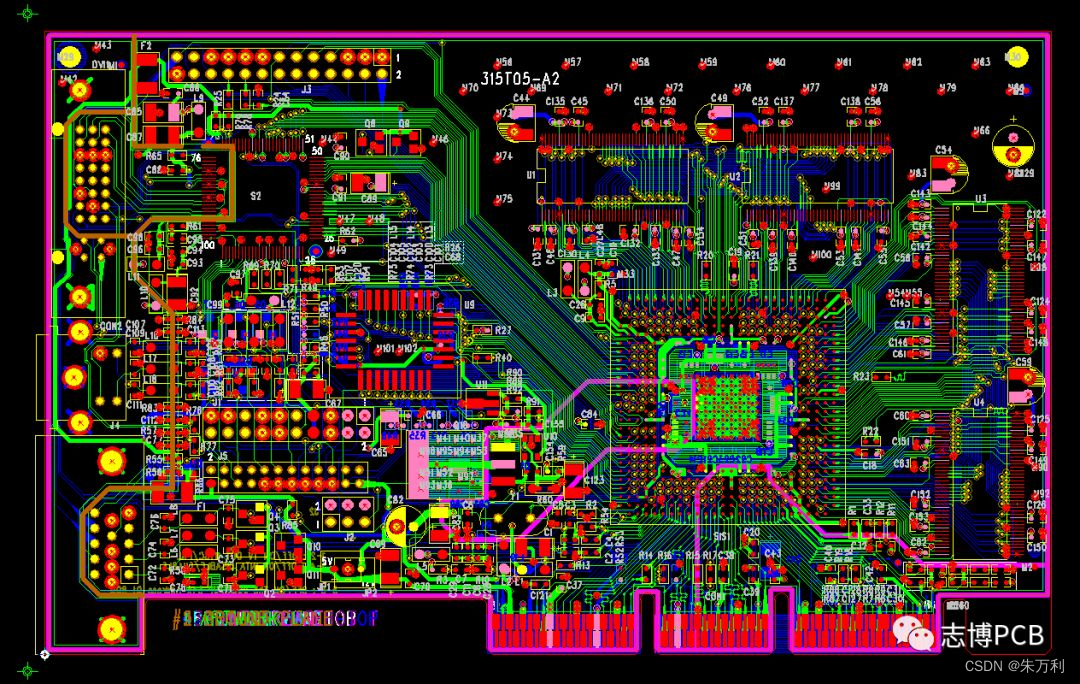

2、DVD主板

3、SIS显卡主板

4、RK3288安卓广告机