什么是PCB走线的3W原则

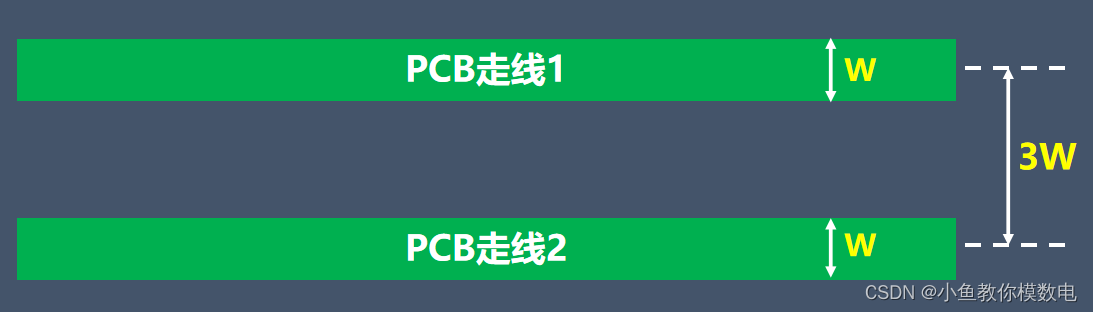

在设计PCB的时候我们会经常说到3W原则, 它指的是两个PCB走线它们的中心间距不小于3倍线宽,这个W就是PCB走线的宽度。

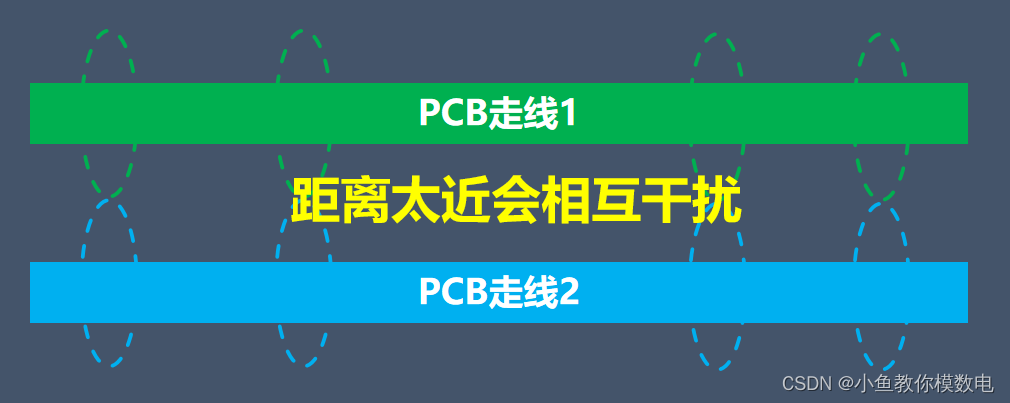

这样做的目的主要是为了减小走线1和走线2之间的串扰,一般对于时钟信号,复位信号等一些关键信号需要遵循3W原则。

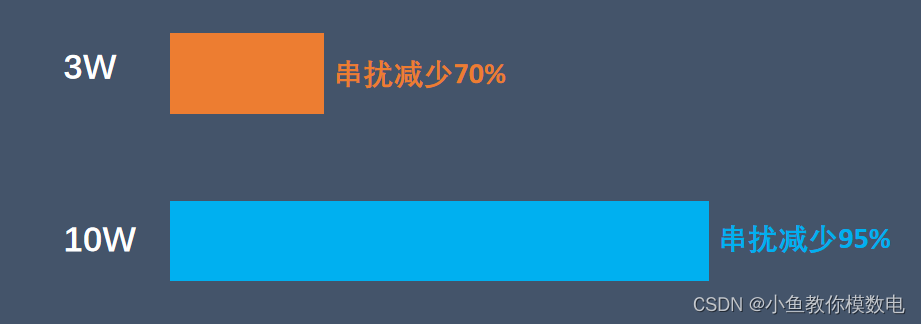

当满足3W原则时,走线间的串扰可减少70%,如果是10W的话串扰可以减少95%。

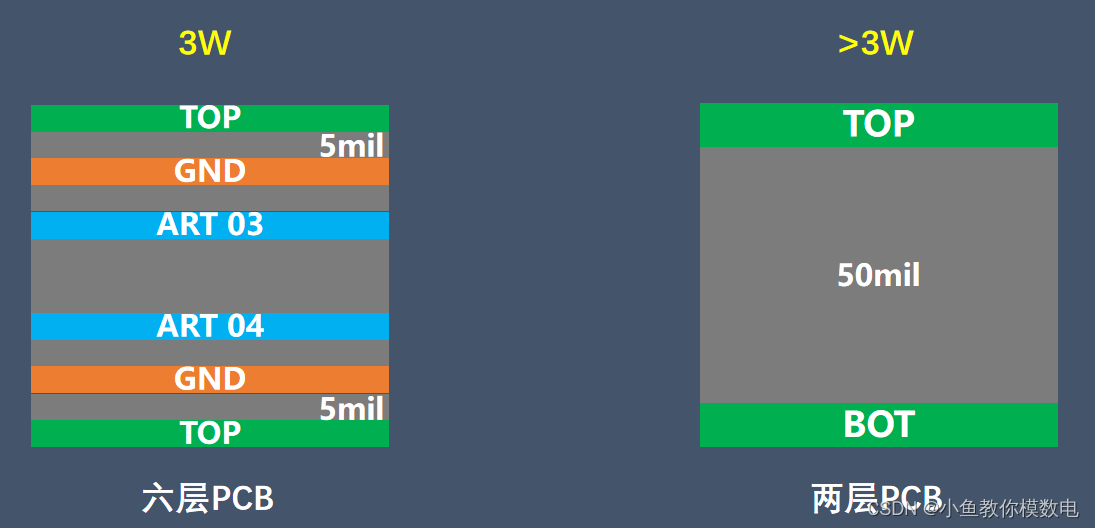

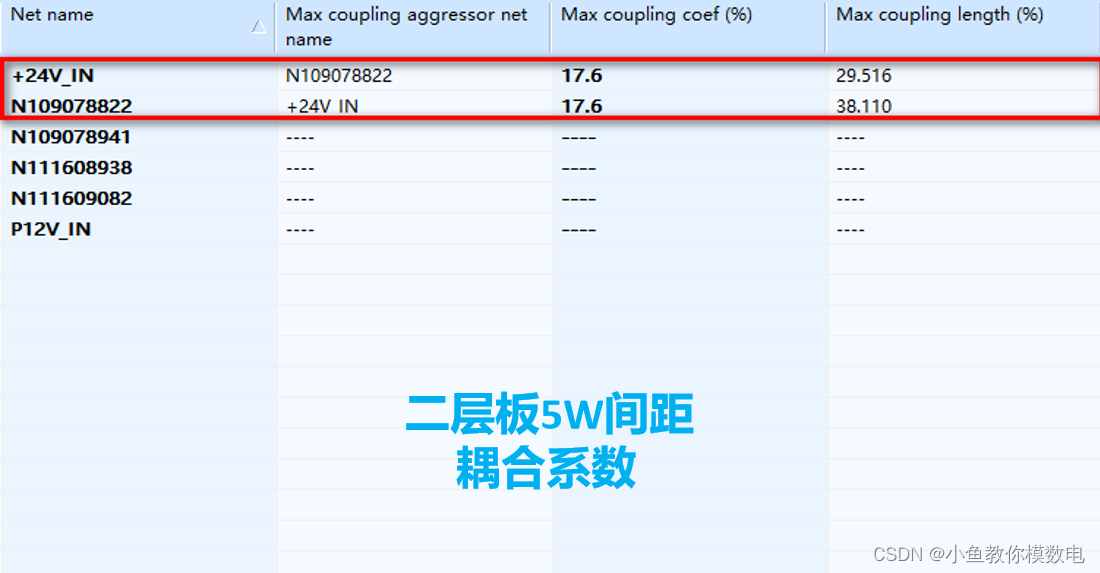

3W原则也是有条件的,它和走线与参考平面的间距也有关系,比如四层板,六层板,走线与参考平面的间距一般在5mil左右,走线间距遵守3W原则可以有效避免串扰,但是如果是两层板,走线与参考平面间距可能在50mil,为了有效减少串扰,走线间距可能要大于3W。

在对PCB走线串扰进行评估的时候我们一般参考耦合系数,耦合系数越大表示PCB走线间越容易发生串扰,当然串扰还和走线间的耦合长度,信号的频率有关,耦合长度越长越容易发生串扰。

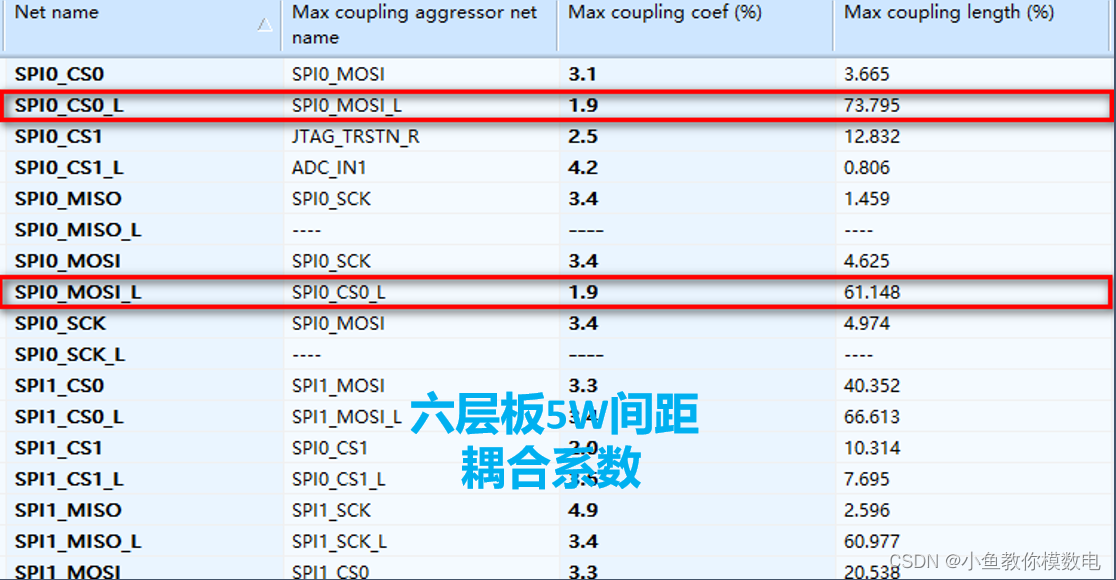

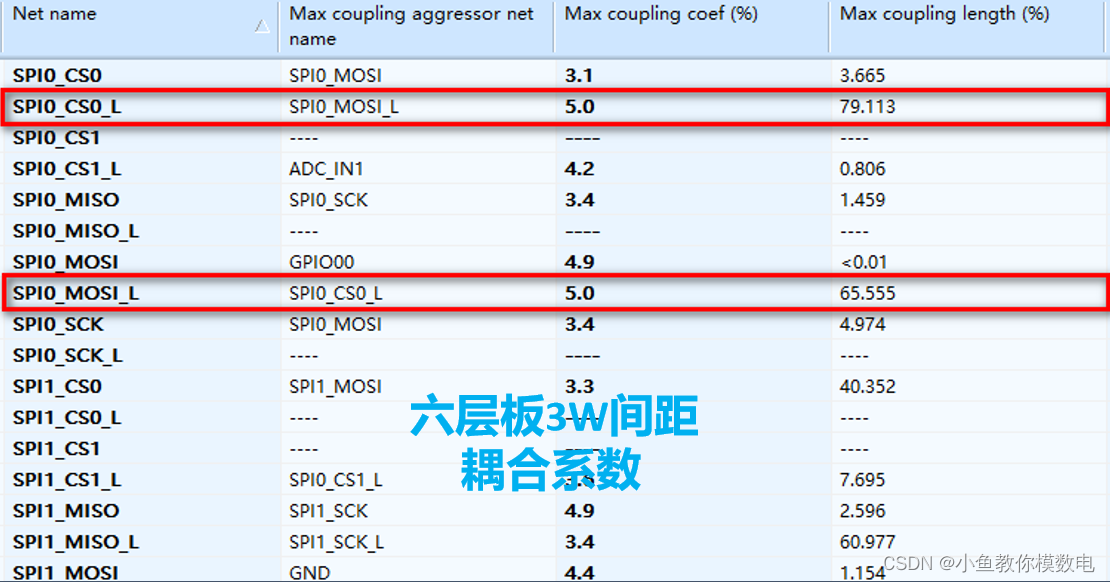

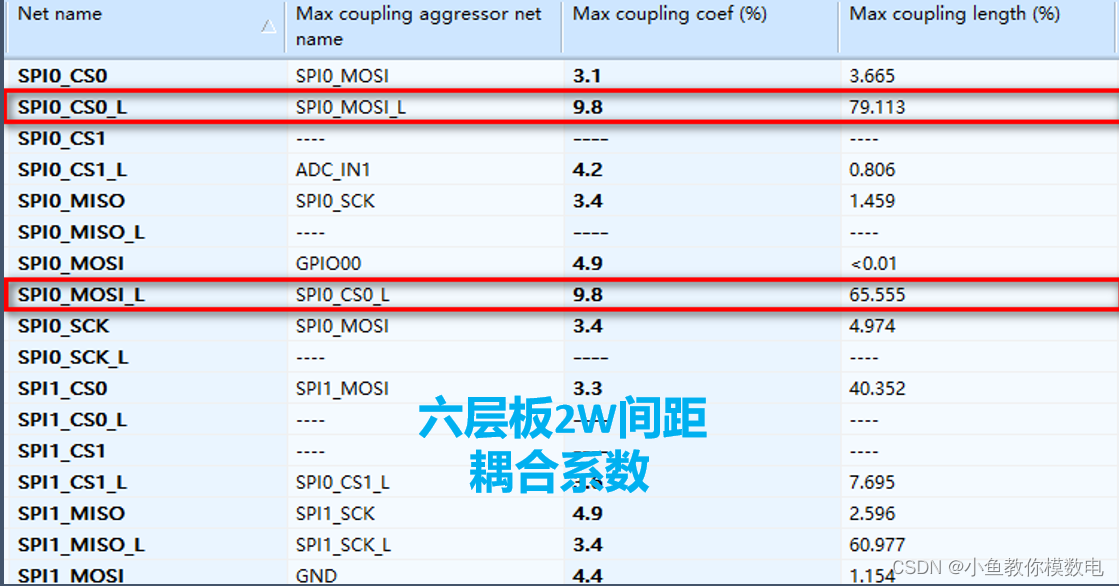

我用软件仿真了一个六层板和一个两层板PCB走线的耦合情况,PCB走线线宽是5mil,中心间距分别为25mil,15mil和10mil,信号上升沿选择的100ps。

下面我们来看下仿真结果:

六层板走线间距为25mil时,也就是中心间距为5W时,耦合系数为1.9,比较小,我们认为走线是OK。

当走线间距为15mil时,也就是中心间距为3W时,耦合系数为5,我们认为走线也是OK的,一般我们在做PCB走线耦合仿真时,耦合系数5%是一个临界值,小于5%我们认为走线是OK,大于5%可能就需要调整走线的间距了。

当间距为10mil时,也就是中心间距为2W时,耦合系数为9.8,我们认为走线有发生串扰的风险需要调整走线的间距。

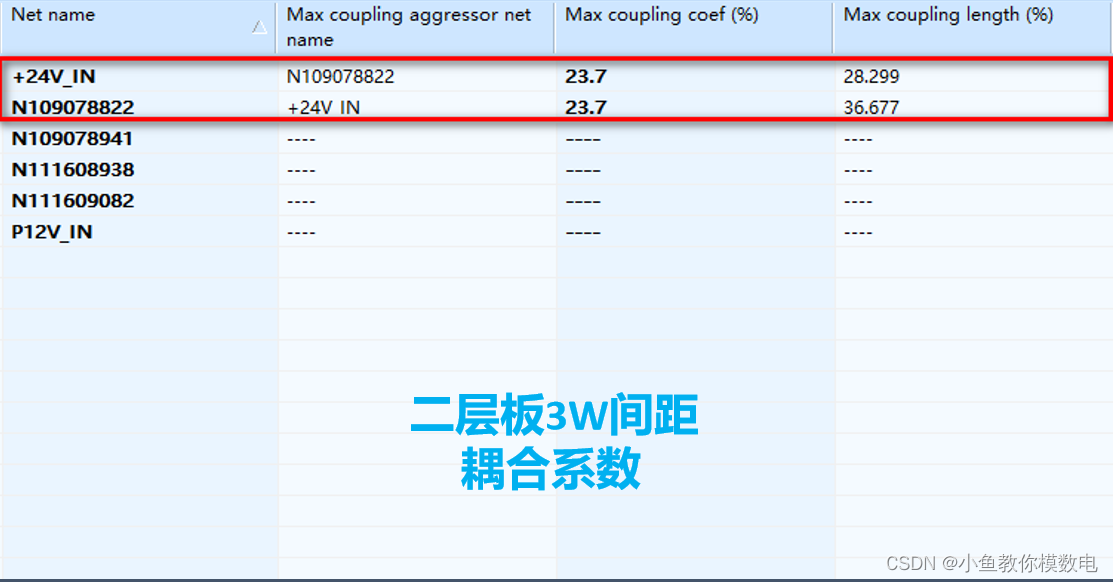

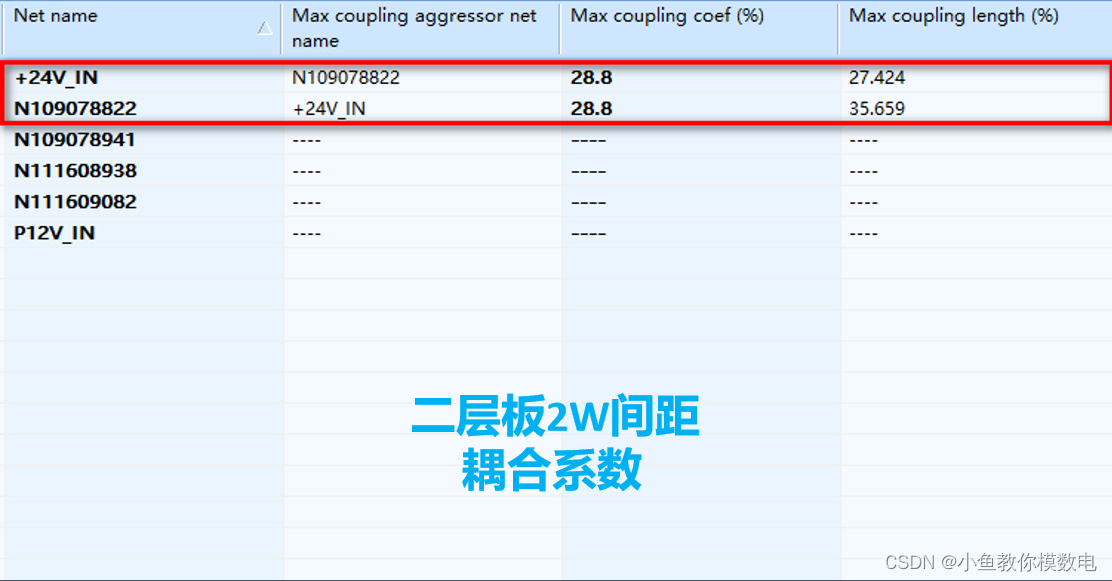

下面我们来看下两层板的仿真。

间距为25mil时,耦合系数为17.6

间距为15mil时,耦合系数为23.7。

间距为10mil时,耦合系数为28.8。

这几种间距耦合系数都大于5%,就像我们前面说的为了有效减少信号串扰,两层板的关键信号走线间距一般要大于3W。