DAC芯片AD5689控制代码SPI接口FPGA代码,视频

名称:DAC芯片AD5689控制代码SPI接口

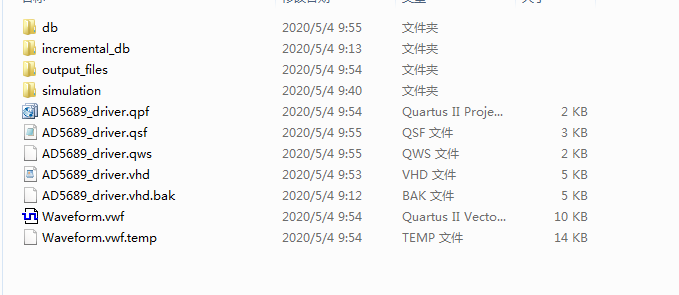

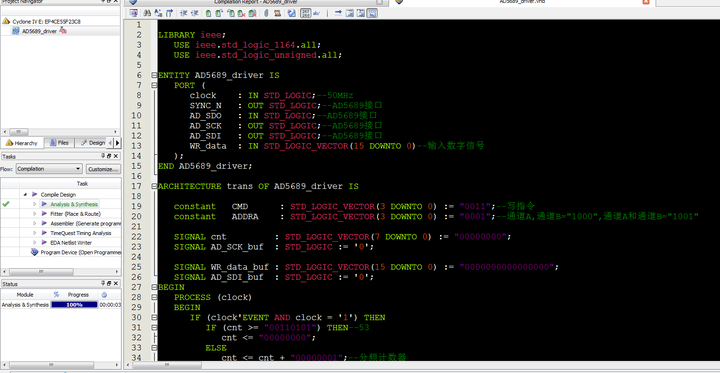

软件:QuartusII

语言:VHDL

代码功能:

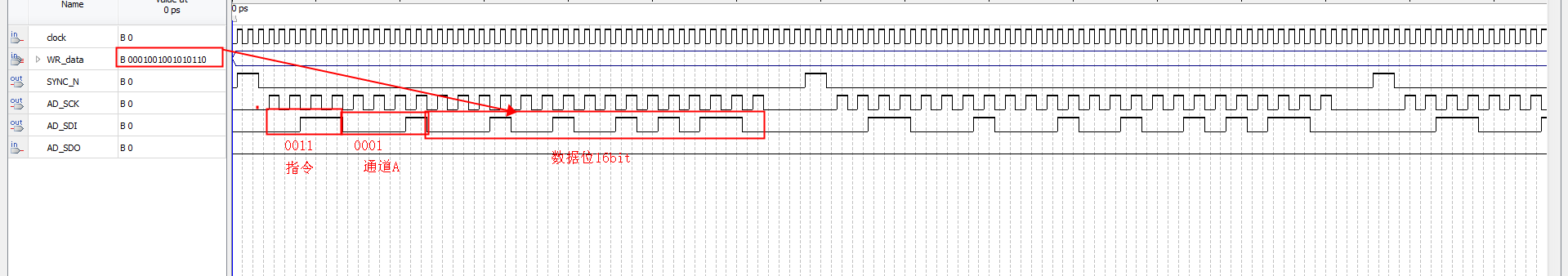

控制DAC芯片AD5689,通过芯片的SPI接口,进行命令和地址、数据写入,控制DAC输出模拟信号。

AD5689/AD5687采用多功能SPI接口,时钟速率高达50 MHz,并均包含一个为1.8 V/3 V/5 V逻辑电平准备的VLOGIC引脚。

设计语言使用VHDL,本代码简单易懂,注释详细,可以方便改写为verilog代码。

演示视频:DAC芯片AD5689控制代码SPI接口VHDL_Verilog/VHDL资源下载

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:DAC芯片AD5689控制代码SPI接口VHDL_Verilog/VHDL资源下载名称:DAC芯片AD5689控制代码SPI接口(代码在文末付费下载)软件:QuartusII语言:VHDL代码功能: 控制DAC芯片AD5689,通过芯片的SPI接口,进行命令和地址、数据写入,控制DAC输出模拟信号。 AD5689/AD5687采用多功能SPI接口,时钟速率高达50 MHz,并均包含一个为1.8 V/3 V/5 V逻辑电平准备的VLOGIC引脚。 设计语言使用V![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=216

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=216

部分代码展示

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY AD5689_driver IS PORT ( clock : IN STD_LOGIC;--50MHz SYNC_N : OUT STD_LOGIC;--AD5689接口 AD_SDO : IN STD_LOGIC;--AD5689接口 AD_SCK : OUT STD_LOGIC;--AD5689接口 AD_SDI : OUT STD_LOGIC;--AD5689接口 WR_data : IN STD_LOGIC_VECTOR(15 DOWNTO 0)--输入数字信号 ); END AD5689_driver; ARCHITECTURE trans OF AD5689_driver IS constant CMD : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0011";--写指令 constant ADDRA : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0001";--通道A,通道B="1000",通道A和通道B="1001" SIGNAL cnt : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000"; SIGNAL AD_SCK_buf : STD_LOGIC := '0'; SIGNAL WR_data_buf : STD_LOGIC_VECTOR(15 DOWNTO 0) := "0000000000000000"; SIGNAL AD_SDI_buf : STD_LOGIC := '0'; BEGIN PROCESS (clock) BEGIN IF (clock'EVENT AND clock = '1') THEN IF (cnt >= "00110101") THEN--53 cnt <= "00000000"; ELSE cnt <= cnt + "00000001";--分频计数器 END IF; END IF; END PROCESS; PROCESS (clock) BEGIN IF (clock'EVENT AND clock = '1') THEN IF (cnt >= "00000000" AND cnt <= "00000001") THEN SYNC_N <= '1';--40ns之后,SYNC拉低,开始进入读取数据的状态 ELSE SYNC_N <= '0'; END IF; END IF; END PROCESS; PROCESS (clock) BEGIN IF (clock'EVENT AND clock = '1') THEN--clock2二分频得到sck的值为--25MHz IF (cnt > "00000001" AND cnt < "00110011") THEN--1~51 IF (cnt(0) = '0') THEN AD_SCK_buf <= '0'; --cnt[0]==0的时候,sck为下降沿 ELSE AD_SCK_buf <= '1';--cnt[0]==1的时候,sck为上升沿

设计文档:

-

工程文件

-

程序文件

-

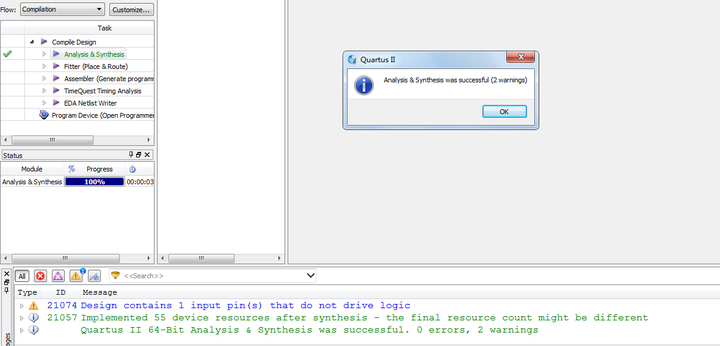

程序编译

-

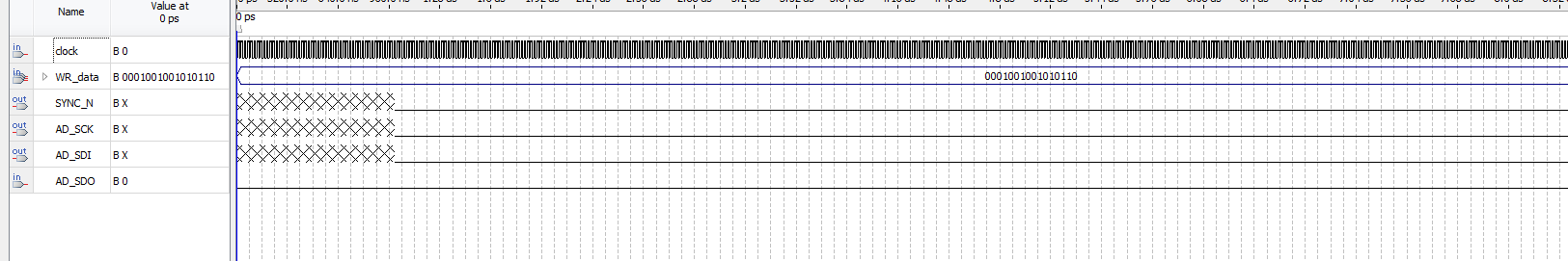

仿真文件

-

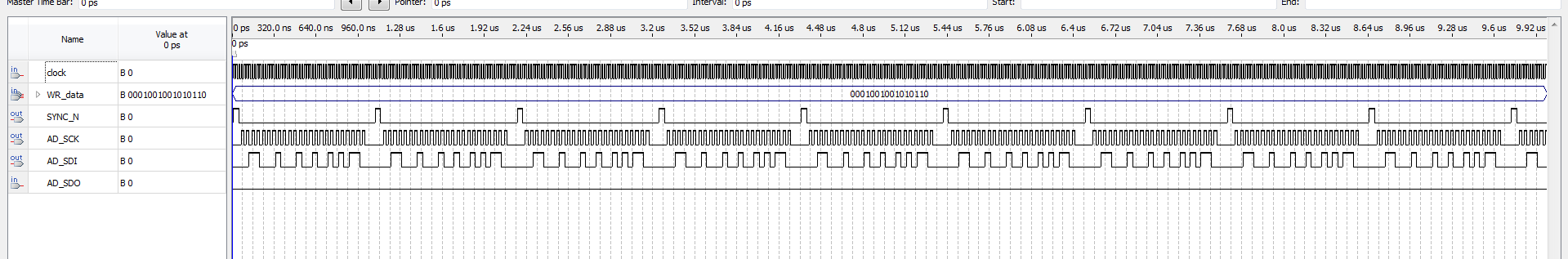

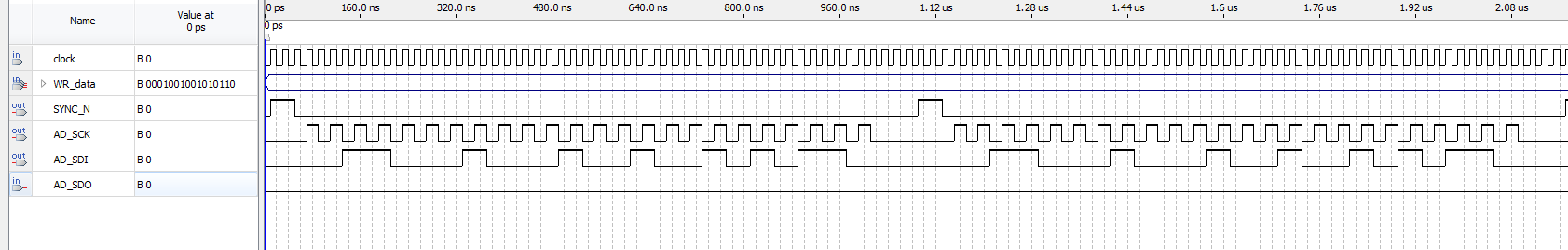

仿真图