三极管与mos管的区分与应用

三极管与mos管的区分与应用

这部分知识每次用都要查,隔一段时间就忘记了.忍无可忍,再此写下来,作为之后然后查找的笔记

这里先推荐几篇我查阅到的笔记,

<<三极管和MOS管驱动电路的正确用法>> https://blog.csdn.net/qq_21794157/article/details/122736035

<<PNP与NPN三极管开关特性>> https://zhuanlan.zhihu.com/p/143366794

插曲,不知道为啥Multisim老是仿真失败,试了好久没成功,最后重开新建文件才顺利.所以仿真也不是很好使.

一、符号和标识

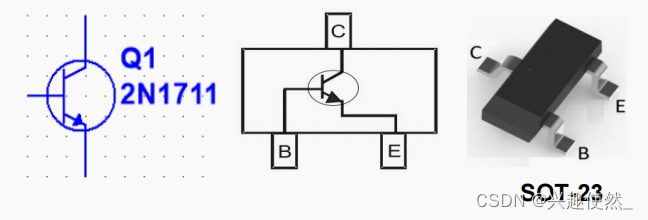

1.NPN(S8050)

- NPN,即

P指向N.箭头朝外指. - 实物封装的c极是单独一侧.将c极(

输入)朝右边,那么左上就是b极(控制),左下就是e极(输出)

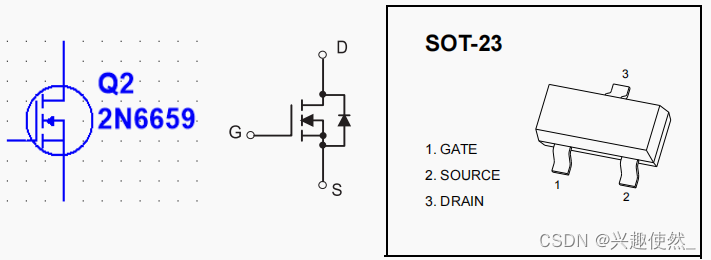

2.N沟道(2N7002)

- N沟道和NPN的箭头符号相反;即

N指向P,箭头朝内指. - 实物封装的d极是单独一侧.将d极(

输入)朝右边,那么左上就是g极(控制),左下就是s极(输出) - (寄生二极管和箭头方向一致)

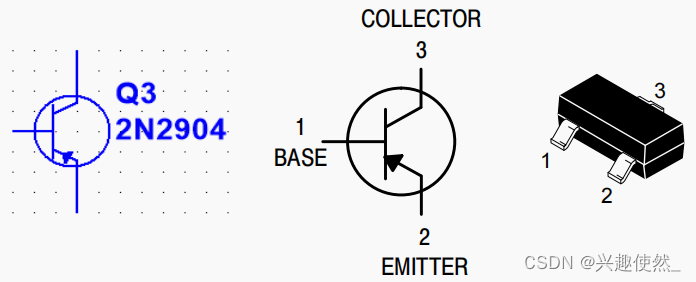

3.PNP(MMBT4403L)

- PNP,即

P指向N.箭头朝内指. - 实物封装的c极是单独一侧.将c极(

输出)朝右边,那么左上就是b极(控制),左下就是e极(输入)

4.P沟道(AO3401A)

- P沟道和PNP的箭头符号相反;即

N指向P,箭头朝外指. - 实物封装的d极是单独一侧.将d极(

输出)朝右边,那么左上就是g极(控制),左下就是s极(输入) - (寄生二极管和箭头方向一致)

二、电路特性

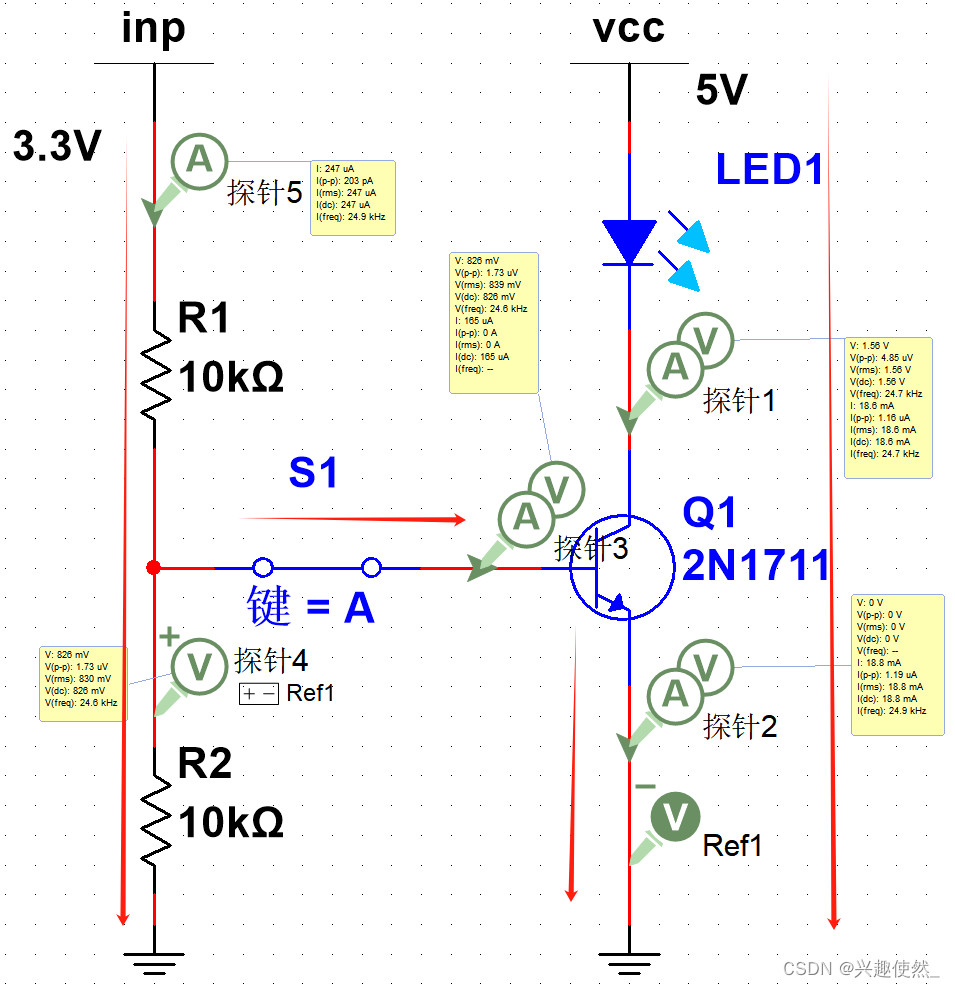

1.NPN

- 电流顺着三极管内的箭头流动,

Ie = Ib + Ic,18.8mA = 0.165mA + 18.6mA; - 电源经过负载接在c极,控制接在b极,地接在c极;

- 经过仿真发现:电流

Ie和Ib正相关;也就是说,如果减小限流电阻R1,那负载电流就会飙升.同时二者的关系总是保持Ie远大于Ib; - c极是接地GND,如果接了限流电阻,负载电流就会严重不足,如果要调整负载电流,应该调整控制端

Ib的限流电阻.因为这同时也是减小控制端的输出电流.

引用大佬的笔记解释:

(1)NPN型三极管,适合射极接GND集电极接负载到VCC的情况。只要基极电压高于射极电压(此处为GND)0.7V,即发射结正偏(VBE为正),NPN型三极管即可开始导通。基极用高电平驱动NPN型三极管导通(低电平时不导通);基极除限流电阻外,更优的设计是,接下拉电阻10-20k到GND。优点是:①使基极控制电平由高变低时,基极能够更快被拉低,NPN型三极管能够更快更可靠地截止;②系统刚上电时,基极是确定的低电平。

(2)对NPN三极管来说,最优的设计是,负载接在集电极和VCC之间。不够周到的设计是,负载接在射极和GND之间。

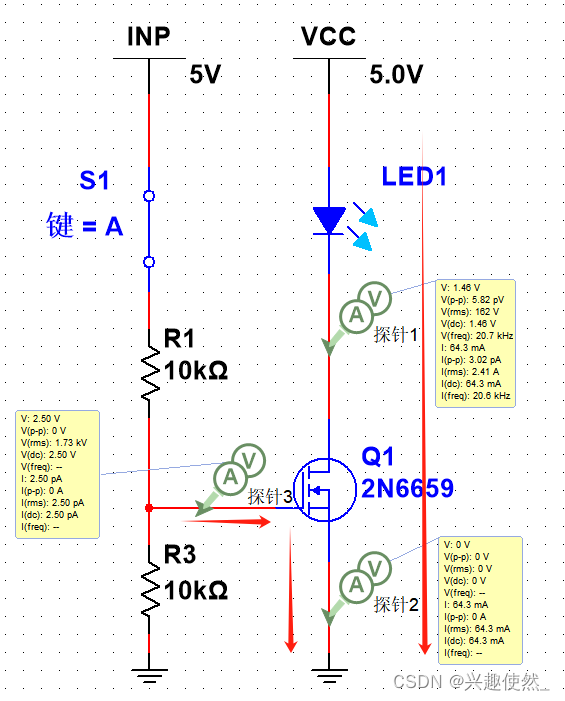

2.N沟道

- 电流逆着mos管内的箭头流动,

Is = Ig + Id,64.3mA = 0mA + 64.3mA; - 电源经过负载接在D极,控制接在G极,地接在S极;

- 对比NPN,N沟道的控制电流

Ig更加小,可以忽略不计的程度;同时也保留:电流Id和Ig正相关;也就是说,如果减小限流电阻R1,那负载电流就会飙升.同时二者的关系总是保持Id远远远远大于Ig, - s极是接地GND,如果接了限流电阻,负载电流就会严重不足.这点和NPN一致;控制电流太小,忽略不计.

引用大佬的笔记解释:

(1)NMOS,适合源极接GND漏极接负载到VCC的情况。只要栅极电压高于源极电压(此处为GND)超过Vth(即Vgs超过Vth),NMOS即可开始导通。栅极用高电平驱动NMOS导通(低电平时不导通);栅极除限流电阻外,更优的设计是,接下拉电阻10-20k到GND,使栅极控制电平由高变低时,栅极能够更快被拉低,NMOS能够更快更可靠地截止。

(2)对NMOS来说,最优的设计是,负载接在漏极和VCC之间。不够周到的设计是,负载接在源极和GND之间。

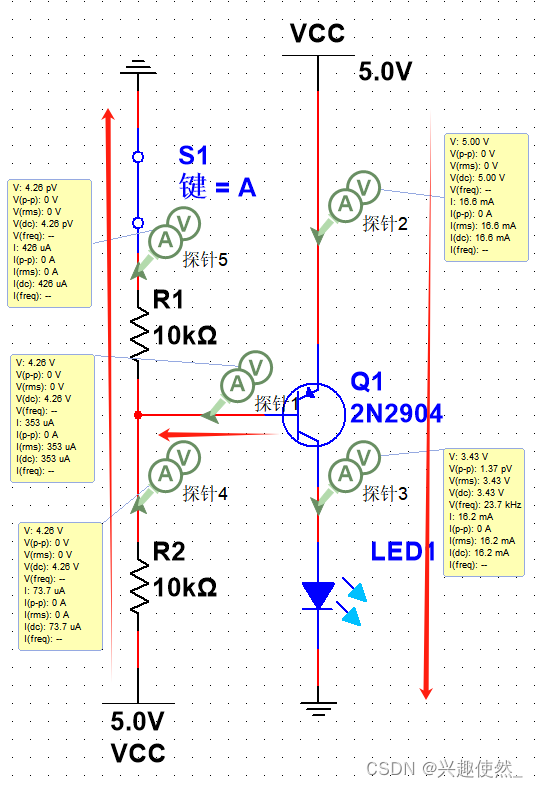

3.PNP

- 电流顺着三极管内的箭头流动,

Ie = Ib + Ic,16.6mA = 0.353mA + 16.2mA; - 电源接在e极,控制接在b极,地经过负载接在c极;

- 经过仿真发现:电流

Ie和Ib正相关;也就是说,如果减小限流电阻R1,那负载电流就会飙升.同时二者的关系总是保持Ie远大于Ib, - e极是接电源,如果接了限流电阻,负载电流就会严重不足,如果要调整负载电流,应该调整控制端

Ib的限流电阻.因为这同时也是减小控制端的输出电流.

引用大佬的笔记解释:

(1)PNP型三极管,适合射极接VCC集电极接负载到GND的情况。只要基极电压低于射极电压(此处为VCC)0.7V,即发射结反偏(VBE为负),PNP型三极管即可开始导通。基极用低电平驱动PNP型三极管导通(高电平时不导通);基极除限流电阻外,更优的设计是,接上拉电阻10-20k到VCC;优点是:①使基极控制电平由低变高时,基极能够更快被拉高,PNP型三极管能够更快更可靠地截止;②系统刚上电时,基极是确定的高电平。

(2)对PNP三极管来说,最优的设计是,负载接在集电极和GND之间。不够周到的设计是,负载接在发射极和VCC之间。这样,就可以避免负载的变化被耦合到控制端。从电流的方向可以明显看出。

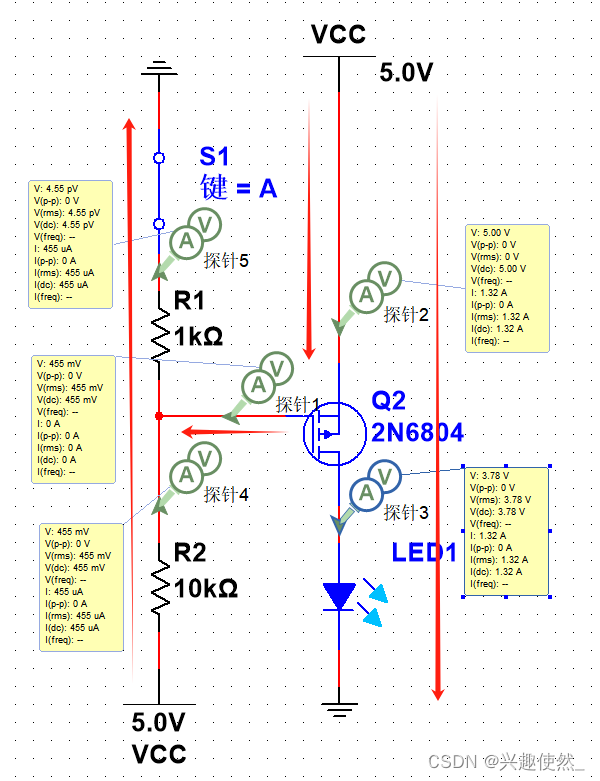

4.P沟道

- 电流逆着mos管内的箭头流动,

Is = Ig + Id,1.32A = 0mA + 1.32A; - 电源接在D极,控制接在G极,地经过负载接在S极;

- 对比PNP,P沟道的控制电流

Ig更加小,可以忽略不计的程度;同时也保留:电流Id和Ig正相关;也就是说,如果减小限流电阻R1,那负载电流就会飙升.同时二者的关系总是保持Id远远远远大于Ig, - d极是接电源,如果接了限流电阻,负载电流就会严重不足.这点和PNP一致;控制电流太小,忽略不计.

引用大佬的笔记解释:

(1)PMOS,适合源极接VCC漏极接负载到GND的情况。只要栅极电压低于源极电压(此处为VCC)超过Vth(即Vgs超过-Vth),PMOS即可开始导通。栅极用低电平驱动PMOS导通(高电平时不导通);栅极除限流电阻外,更优的设计是,接上拉电阻10-20k到VCC,使栅极控制电平由低变高时,栅极能够更快被拉高,PMOS能够更快更可靠地截止。

(2)对PMOS来说,最优的设计是,负载接在漏极和GND之间。不够周到的设计是,负载接在源极和VCC之间。

三、总结

- 三极管和mos管,特性接近;电压导通,电流控制;

- 以三极管为例: 电流顺着箭头,箭头始末两端压差大于

0.7V时,就可以导通;箭头是由P指向N; - mos管和三极管相反;电流逆着箭头;

有点绕,如果发现写错了请评论区指出,我看到后会立刻更正;.(

不自信)

- 最后一张大合照,不多说,