FPGA模块——AD高速转换模块(并行输出转换的数据)

FPGA模块——AD高速转换模块(并行输出转换的数据)

- (1)AD9280/3PA9280芯片

- (2)代码

(1)AD9280/3PA9280芯片

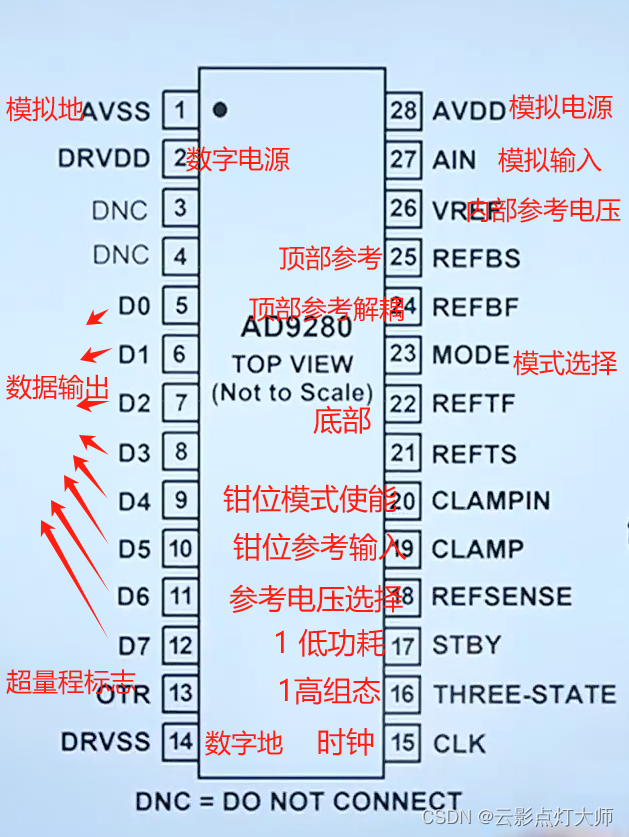

AD9280/3PA9280芯片的引脚功能:

工作电压2.7到5.5v

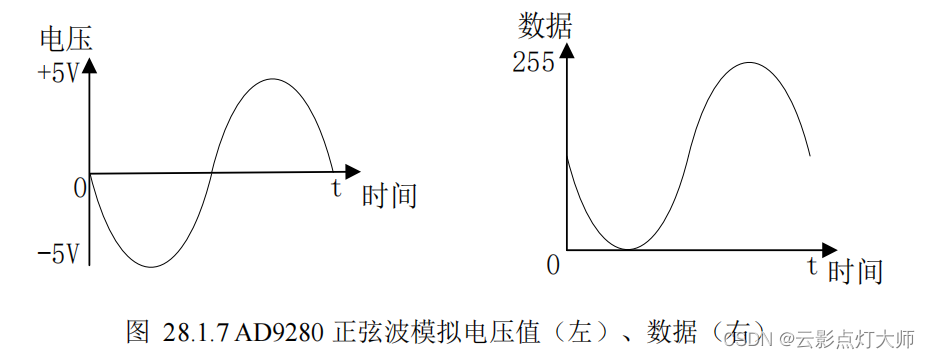

数据对应:

AD9280 支持输入的模拟电压范围是 0V 至 2V,0V 对应输出的数字信号为 0,2V 对应输出的数字信号为 255。而 AD9708 经外部电路后,输出的电压范围是-5V到+5V,因此在 AD9280 的模拟输入端增加电压衰减电路,使-5V到+5V 之间的电压转换成 0V 至 2V 之间。

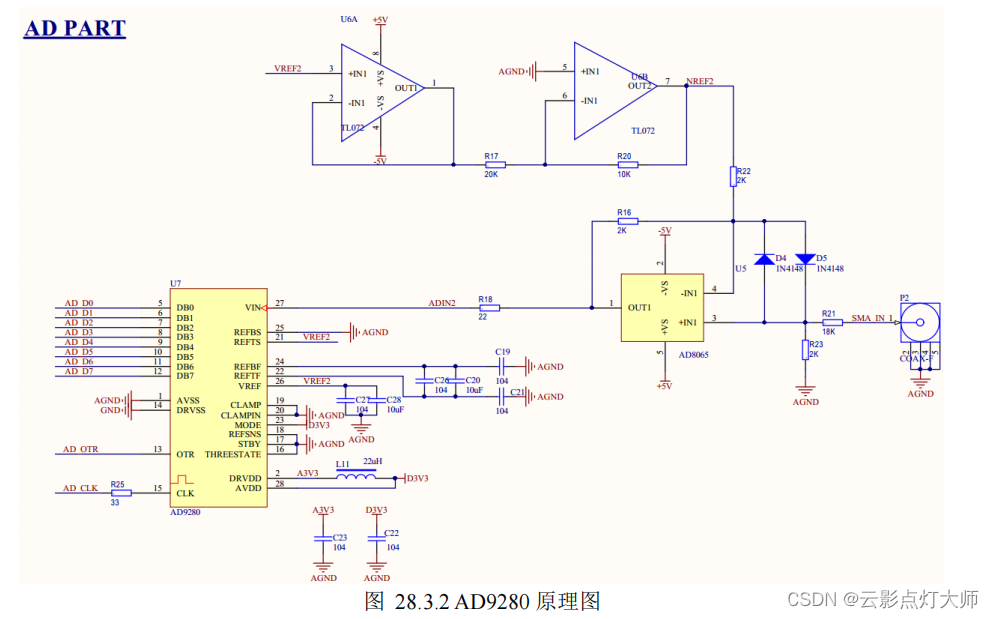

应用电路图:

包括电压跟随器,反向放大器,减法器。

(2)代码

并行输入8位数据和超量程标志,要提供一个AD_clk给AD转换芯片。

module ad_wave_rec(

input clk , //时钟

input rst_n , //复位信号,低电平有效

input [7:0] ad_data , //AD输入数据

//模拟输入电压超出量程标志(本次试验未用到)

input ad_otr , //0:在量程范围 1:超出量程

output reg ad_clk //AD

);

//时钟分频(2分频,时钟频率为25Mhz),产生AD时钟

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

ad_clk <= 1'b0;

else

ad_clk <= ~ad_clk;

end

endmodule