制作一个RISC-V的操作系统二-RISC-V ISA介绍

文章目录

- ISA的基本介绍

- 啥是ISA

- 为什么要设计ISA

- CISCvsRISC

- ISA的宽度

- 知名ISA介绍

- RISC-V历史和特点

- RISC-V发展

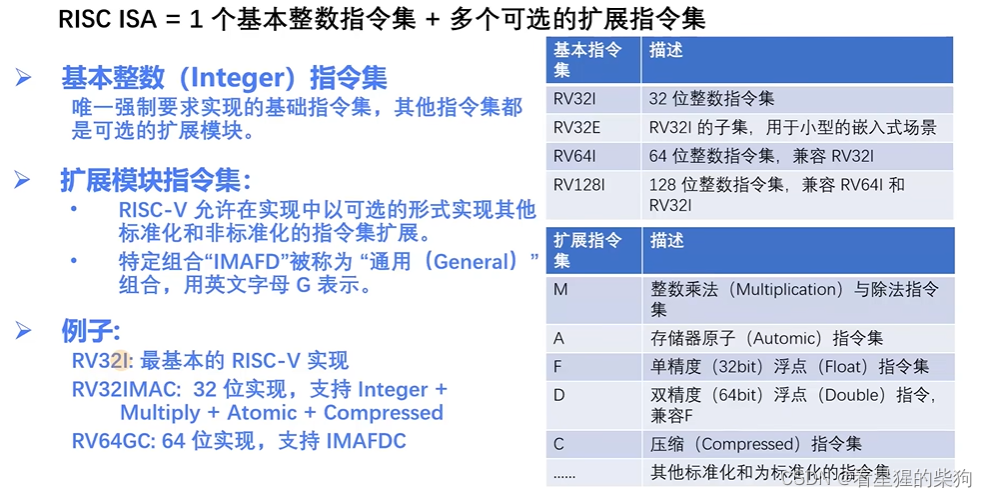

- RISC-V ISA 命名规范

- 模块化的ISA

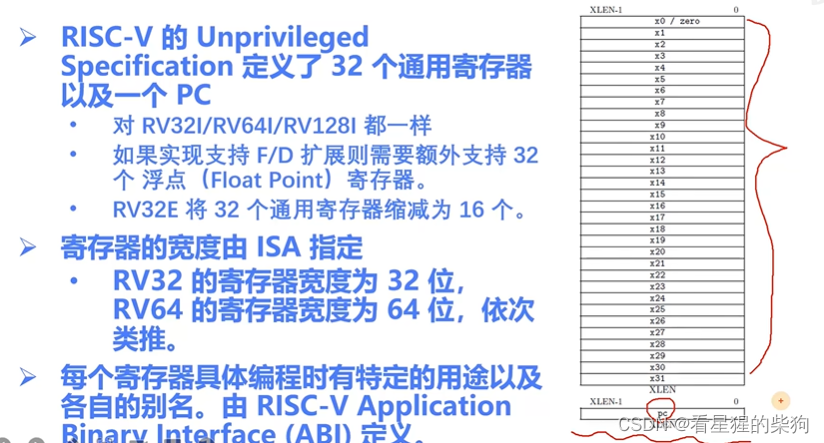

- 通用寄存器

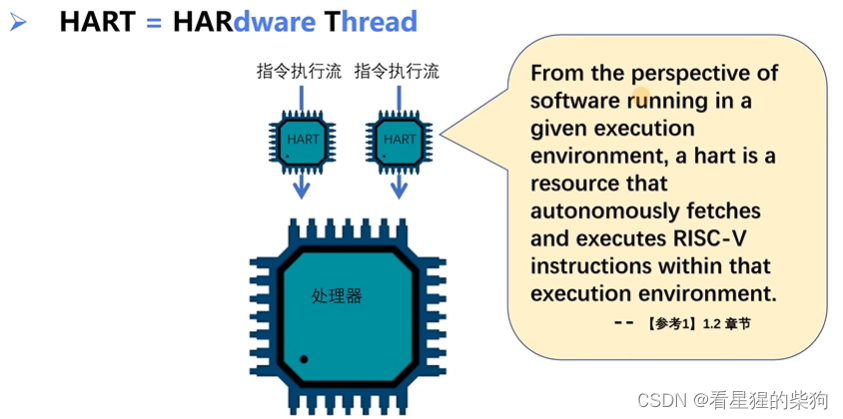

- Hart

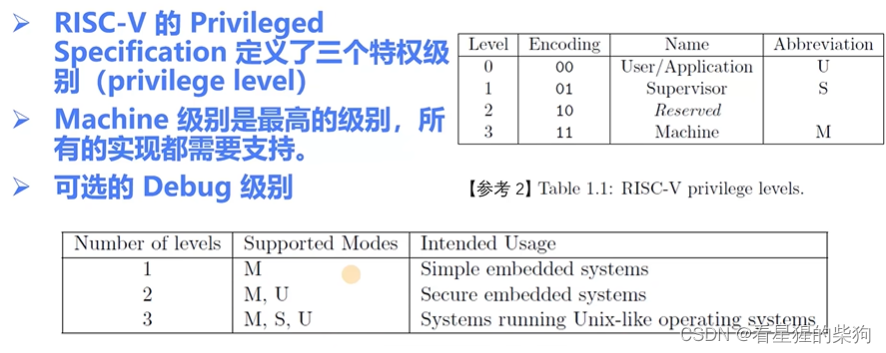

- 特权级别

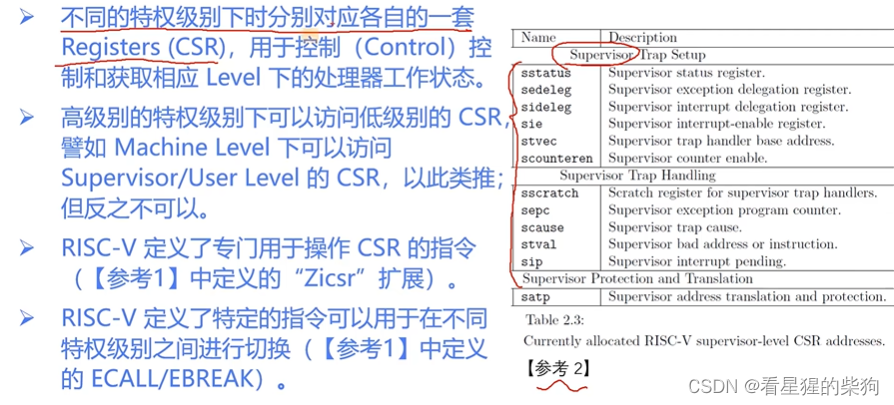

- Control and Status Register(CSR)

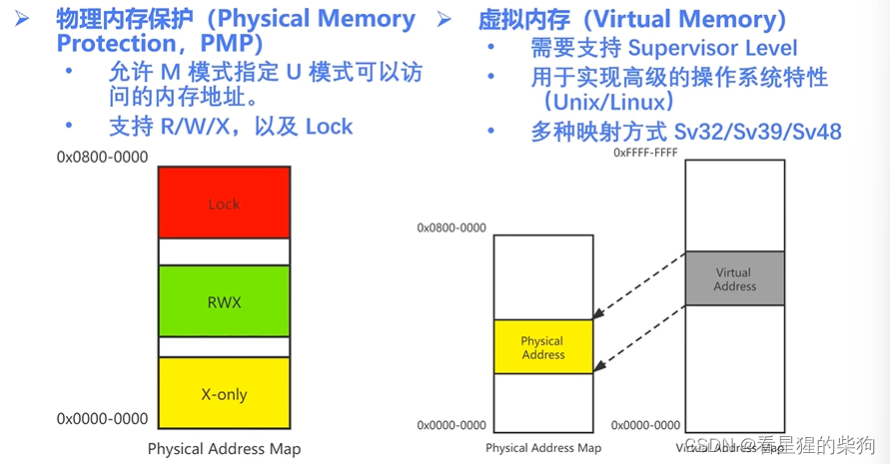

- 内存管理与保护

- 异常和中断

ISA的基本介绍

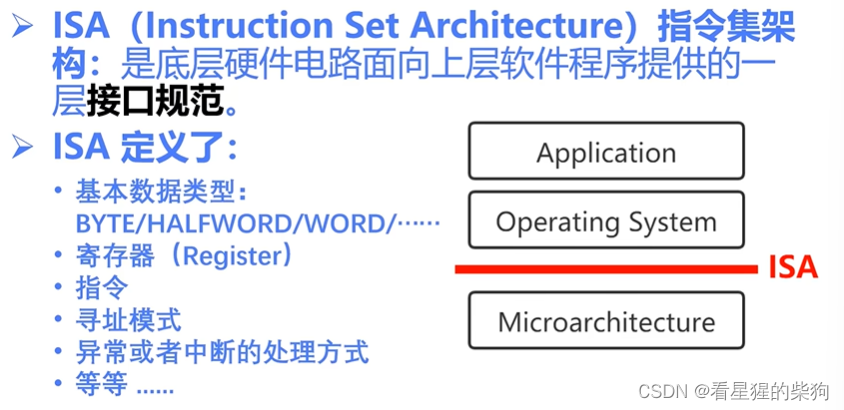

啥是ISA

接口规范:可理解为一种标准

Microarchitecture:微架构(是对指令集架构的一种硬件上的实现,如两种硬件架构都可以实现x86,那么可称这两种硬件架构是微架构)

为什么要设计ISA

为上层软件提供一种抽象,制定规则和约束,让编程者不用操心具体的电路结构或者说不用担心导致硬件运行出问题

CISCvsRISC

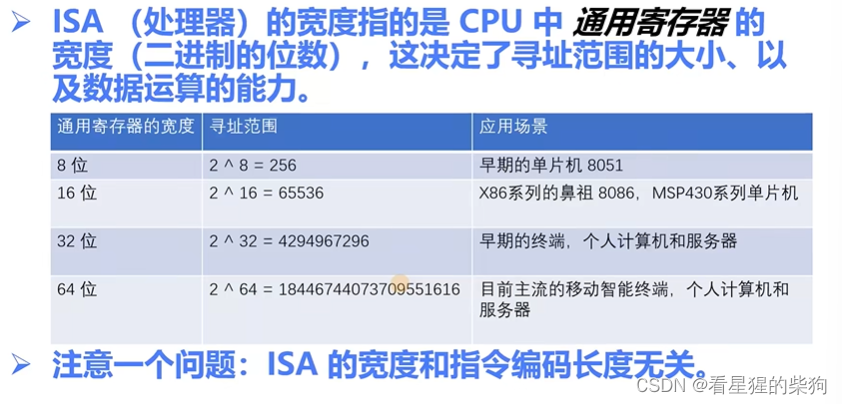

ISA的宽度

ISA的宽度和指令的宽度无关(即不能说32位的机器,那么指令也是32位)

知名ISA介绍

CISC:X86

RISC:图中剩下都是

RISC-V历史和特点

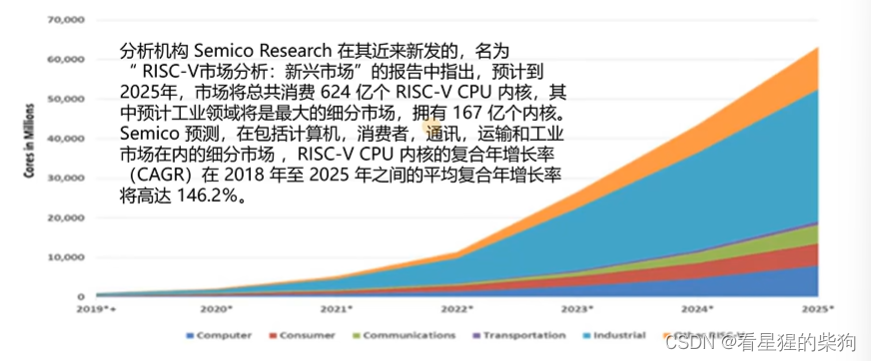

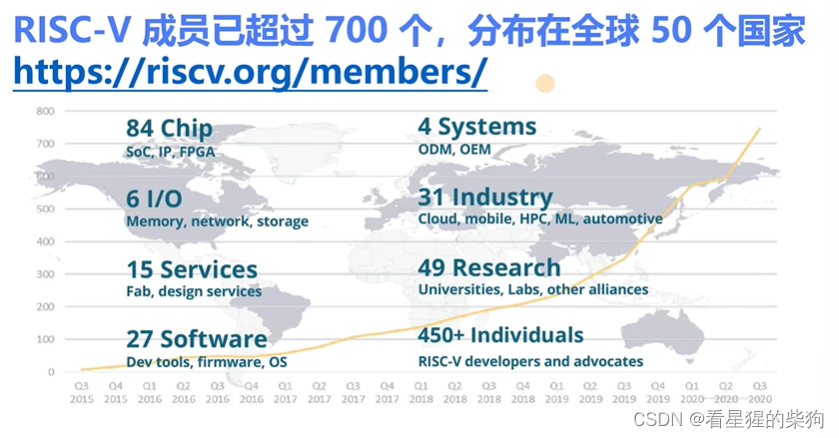

RISC-V发展

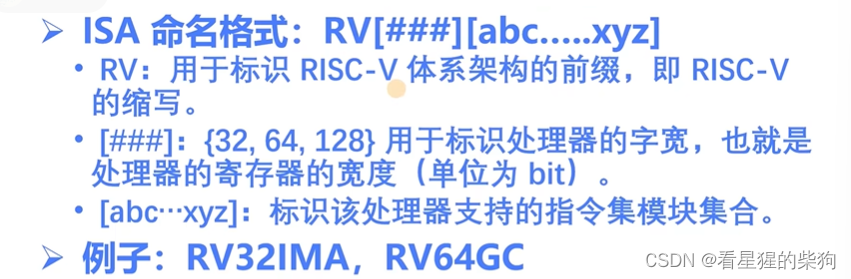

RISC-V ISA 命名规范

RV32IMA:32位 I模块 M模块 A模块

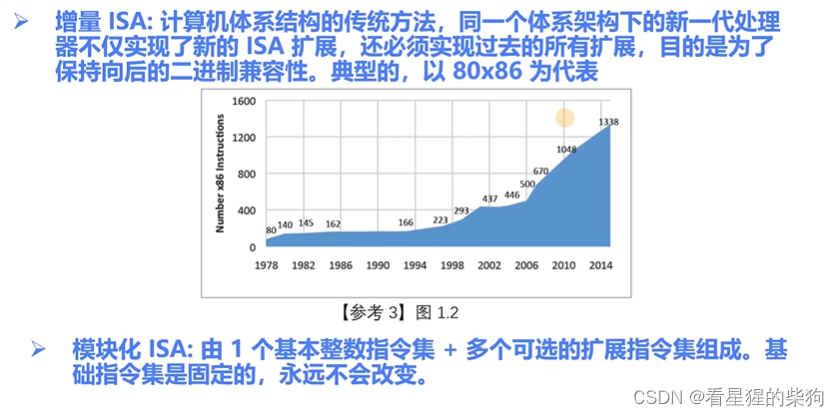

模块化的ISA

32位和64位的指令都是32位,而使用压缩指令集即可使指令为16位

通用寄存器

Hart

一个CU:一个指令流

Hart相当于一个指令流

特权级别

Control and Status Register(CSR)

内存管理与保护

Lock:不能使用

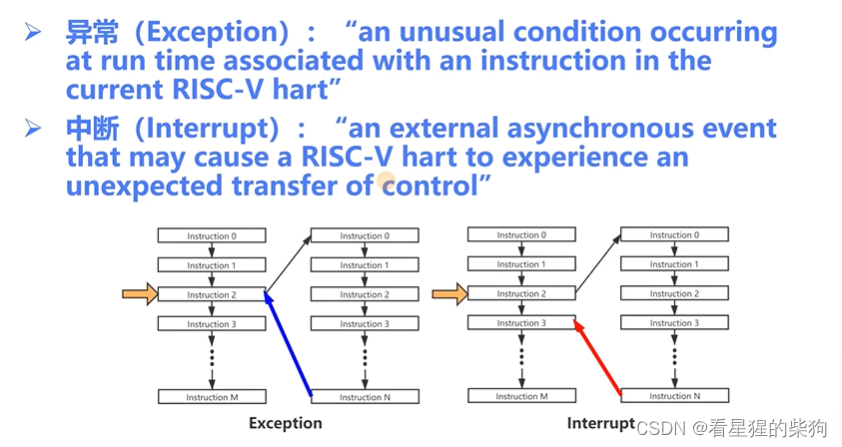

异常和中断

异常会跳转到异常处理程序,执行完后再回来继续执行原指令

中断也跳转到中断处理程序,执行完后再回来执行原指令的下一条指令