pci总线协议学习笔记——PCI总线基本概念

1、pci总线概述

(1)PCI,外设组件互连标准(Peripheral Component Interconnection),是一种由英特尔(Intel)公司1991年推出的用于定义局部总线的标准;

(2)最早提出的PCI总线工作在33MHz频率之下,传输带宽达到133MB/s(33MHz * 32bit/s)。后面提出64bit的pci总线,总线频率也提升到66MHz;

(3)pci协议已经被pcie总线替代,现在pcie总线是主流,但是软件编程上pci和pcie两个总线是兼容的,几乎可以不用做区分,只需要在配置、传输等底层操作去区分两种总线协议;

2、pci总线特点

(1)pci总线是串行总线,有32/64根地址线。地址和数据都通过这32/64根地址线进行传输,分时复用;

(2)pci总线上可同时挂载多个设备,设备分为主设备和从设备,主设备一般是主控芯片的pci控制器,需要负责pci总线上的总裁;

(3)pci设备将共享总线。同一条pci总线上的设备,总线都是接在一起的,会通过片选引脚、地址范围、总线号、设备号、功能号等机制来觉得当前和哪个设备通信;

(4)pci总线通信大致分为两个阶段:配置阶段、通过地址访问阶段;

(5)配置阶段:pci总线控制器去依次扫描接在pci总线上的所有设备,访问设备的配置空间,知道设备的类型、要申请的资源,然后给设备分配总线号、设备号、功能号、地址空间,并写进设备的配置空间;

(6)地址访问阶段:在配置阶段给每一个pci设备分配pci地址范围并写进设备寄存器,以后设备会监听地址线,当监听到地址线上传输的地址是自己的地址范围,就会去处理;

(7)pci采用同步时序协议,信号线里有clk时钟线;

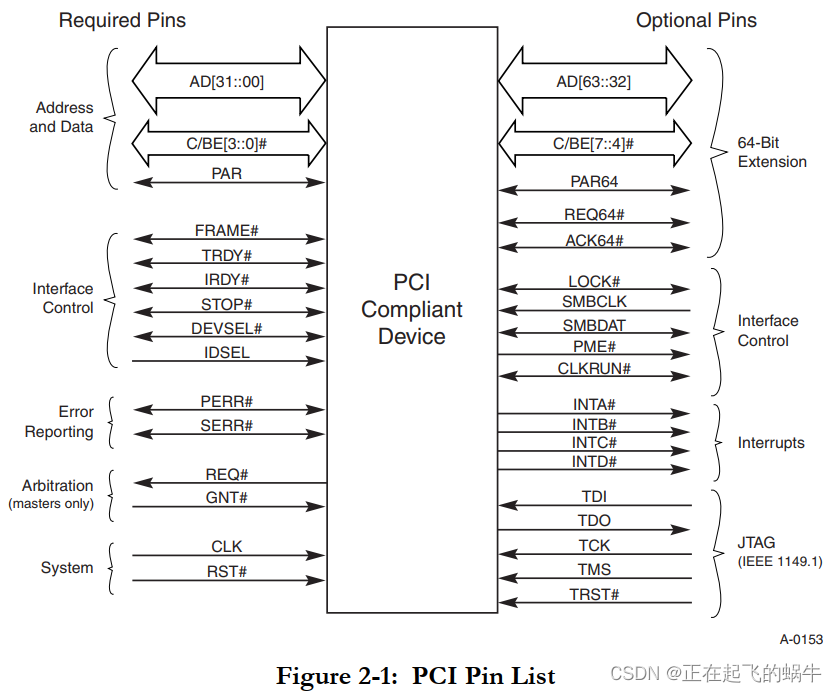

3、pci信号线

| 信号线 | 功能描述 |

|---|---|

| CLK | 总线的时钟线,提供同步时序基准,由pci控制器提供 |

| RST# | 复位信号线,强制所有pci寄存器、排序器、信号回到初始状态 |

| AD[0:63] | 地址和数据复用线 |

| FRAME# | 帧信号,表示传输开始和结束 |

| C/BE[3:0] | 总线命令编码 |

| INTA#—INTD# | 终端信号线 |

| IRDY | Master可以传输数据的标志 |

| TRDY | Slave可以转输数据的标志 |

| DEVSEL# | 当Slave发现自己被寻址时置低应答 |

| GNT# | 总裁器允许Master得到总线使用权的信号 |

| IDSEL | 片选引脚,高电平表示该设备被主设备选中 |

4、PCI总线的命令码

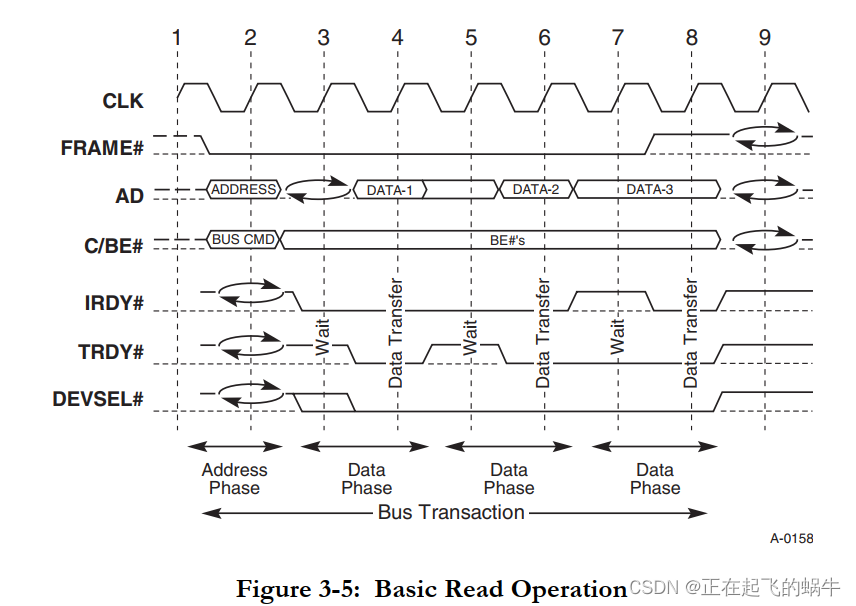

5、 PCI总线读周期时序分析

(1)知识点补充:PCI总线是在下降沿改变信号线上的状态,在上升沿锁定信号线的状态;圆形箭头符号,表示信号线的所有权发送变化;

(2)第一个周期上升沿:此时FRAME#是高电平,表示没有开始传输数据,此时总线空闲;

(3)第二个周期上升沿:此时主设备将地址发到AD线上,将命令码发到C/BE#线上,FRAME#拉低表示数据传输开始,FRAME#拉低的第一个时钟周期AD线上传输的是地址,后续时钟周期AD线上传输的是数据;

(4)第三个周期上升沿:从设备开始解析地址和命令码,地址匹配的从设备将DEVSEL#拉低;主设备将IRDY#线拉低,表示准备好接收数据;

(5)第四个周期上升沿:从设备将数据发送到AD线上,并将TRDY#拉低,表示从设备准备好数据;主设备接收数据;

(6)第五个周期上升沿:从设备没有准备好数据,将TRDY#线拉高,插入一个等待周期;

(7)第六个周期上升沿:从设备将数据发送到AD线上,并将TRDY#拉低,表示从设备准备好数据;主设备接收数据;

(8)第七个周期上升沿:从设备将数据发送到AD线上,并将TRDY#拉低,表示从设备准备好数据;主设备将IRDY#拉高,表示没有准备好接收数据,插入一个等待周期;

(9)第八个周期上升沿:主设备从AD线上接收数据,并且FRAME#被拉高,表示数据传输结束,当前这是最后一个字节;

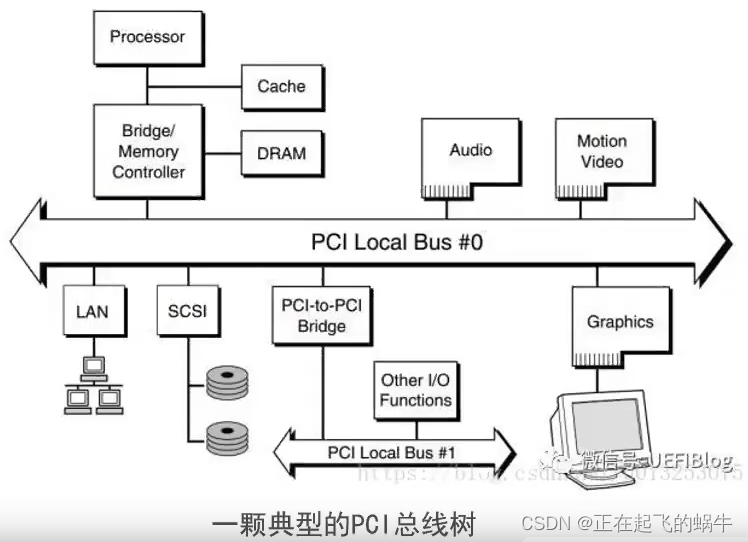

6、典型pci总线拓扑

PCI总线上不仅可以挂载多个PCI设备,还可以挂载PCI桥,形成多级的PCI总线架构;

推荐

给大家推荐一个学校嵌入式知识的网站,博主在大学时候学习嵌入式知识、找工作的时候都在用这个网站,网站里有C语言、Linux等等的笔试题、面试常问问题等等知识,无论是学习基础知识、面试刷题、交流工作经验都是不错的选择。大家一起进步,欢迎留言交流。

链接:学习神器跳转