vivado实现分析与收敛技巧9-分析使用率统计数据

实现问题的常见原因之一是未考量显式和隐式物理约束。例如

,

管脚分配

(pinout)

在逻辑布局上变为显式物理约束。 slice(

分片

)

逻辑在大部分器件中都是一致的。但如下专用资源表示的是隐式物理约束

,

因为这些资源仅在某些位置可用,

并且会影响逻辑布局

:

•

I/O

• 千兆位收发器

•

DSP slice

• 块

RAM

• 时钟管理块

,

如

MMCM

• 时钟缓冲器

,

如

BUFG

在为设计的其余部分设计接口时

,

大量耗用这些专用资源的块可能必须围绕器件分散排列并采用物理约束布局布线。此 外,

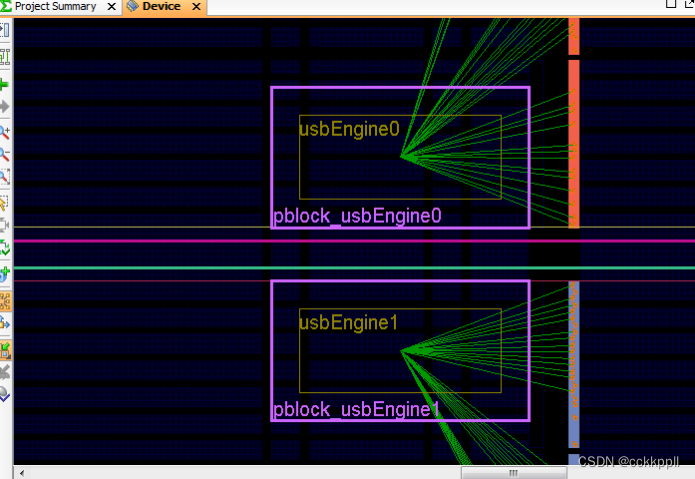

Pblock

为显式物理约束

,

用于为指定逻辑定义允许的布局区域。通过搭配使用以下方法来分析器件上的块资源使用率:

• 使用率报告

• 网表属性

•

Pblock

属性

将特定逻辑锁定到器件站点

您可将单元布局在

FPGA

上的特定位置

,

例如将所有

I/O

端口都布局在

AMD 7

系列

FPGA

设计上。

AMD

建议您在尝试时序收敛前完成 I/O

布局。I/O 布局可能影响

FPGA

互连结构中的单元布局。对互连结构中的其他单元进行手动布局有助于为时钟逻辑和宏布局提供一致性,

目的是提升实现运行的一致性。

固定单元和非固定单元

固定单元和非固定单元适用于已布局的单元。这两类单元用于描述

Vivado

工具查看设计中已布局的单元的方式。

对堆叠硅片互联

(SSI)

器件进行布局规划

对于堆叠硅片互联

(SSI)

器件

,

存在额外的注意事项。

SSI

器件是由多个以中介层相连的超级逻辑区域

(SLR)

组成的。中介层连接称为超长线路 (SLL)

。当跨

SLR

交汇时会发生延迟惩罚。构造设计、生成管脚分配和布局规划时,

请时刻留意

SLR

。将关键时序路径的逻辑单元保持在单一

SLR

内

,

从而最大限度减少 SLL

交汇。

I/O

必须与相关

I/O

接口电路布局在同一个

SLR

内。为

SSI

器件布局逻辑时

,

也必须仔细考量时钟布局。

判断保持修复对设计是否存在负面影响

Vivado Design Suite

布线器认为保持时间的修复优先级高于建立时间。这是因为实验室内的设计即使不满足建立时间,

只要差距较小则仍可能有效。并且始终可以选择降低时钟频率。但如果存在保持时间违例

,

则设计几乎不可能正常运行。

大部分情况下

,

布线器可在不影响建立时间的情况下满足保持时序要求。在某些情况下

(

主要由于设计或约束中存在的错误),

建立时间会受到显著影响。通常导致保持检查错误的原因主要是

set_multicycle_path

约束错误

(

未指定 -hold

)

。其他情况下

,

保持时间要求过高则是由时钟偏差过大而导致的。在此情况下

,

AMD

建议您复查此特定电路的时钟设置架构如果设计布局后可满足建立时序要求,

但布线后不满足建立时间

,

则可能出现此问题。为了修复保持时间违例

,

布线器

会添加布线绕行

,

使用

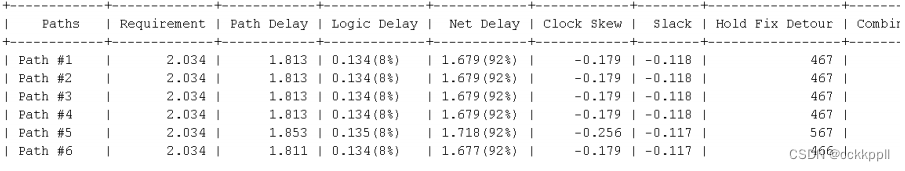

report_design_analysis

命令搭配

-show_all

选项即可查看由此所导致的路径延迟。下图显示的 report_design_analysis

报告示例中包含“

Hold Fix Detour

”

(

保持修复绕行

)

列

,

用于指示布线器由于保持时间修复而添加到时序路径中的延迟 (ps)

。

如果怀疑保持修复影响时序收敛

,

可使用以下任一方法来判断

:

•

方法

1

:

不含保持修复情况下的布线

•

方法

2

:

在失败的最差建立时间路径上运行

report_timing -min

方法

1

:

不含保持修复情况下的布线

1.

将布局后检查点读取到

Vivado Design Suite

中。

2.

添加约束以禁用所有保持检查

:

set_false_path -hold -to [all_clocks]

3.

请运行

route_design

和

report_timing_summary

。

如果含保持时间检查的

WNS

与不含该检查的

WNS

之间存在明显差异

,

则表明保持违例可能过大

,

而建立路径正受到影响。

方法

2

:

在失败的最差建立时间路径上运行

report_timing -min

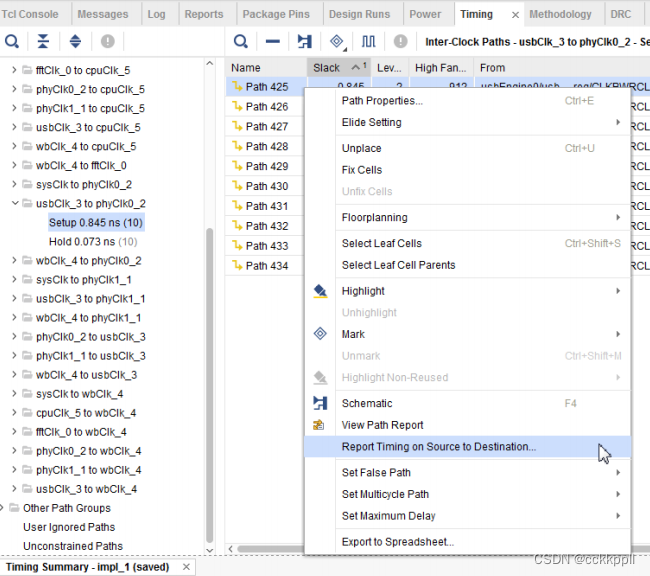

请复查该路径的保持时间以判定失败的最差建立时间路径是否是由于保持时间修复所导致的。在

Vivado IDE

中

,

右键单击并单击“Report Timing on Source to Destination

”

(

报告从源到目标的时序

)

。与执行建立时序分析相反

,

查看保持时序至关重要。获得保持时间报告后,

请验证要求

,

确保在路径上未添加额外延迟以满足保持时间要求。