PCIe物理层弹性缓存机制(详细)解析-PCIe专题知识(四)

目录

- 前言

- 一、简介

- 二、详细解析

- 2.1 实例解析

- 2.2 具体实现过程

- 三、总结

- 四、其他相关链接

- 1、PCI总线及发展历程总结

- 2、PCIe物理层总结-PCIE专题知识(一)

- 3、PCIe数据链路层图文总结-PCIe专题知识(二)

- 4、PCIe物理层链路训练和初始化总结-PCIe专题知识(三)

- 5、8b/10b编码方式详细总结

前言

本文主要介绍PCIe物理层弹性缓存机制用于同步时钟。

一、简介

PCIe物理层弹性缓存(Elastic Buffer,又称为CTC Buffer或者Synchronization Buffer)。其本质上是一种FIFO,主要用于解决跨时钟域问题。当然,PCIe的弹性缓存还用于补偿时钟误差(Compensate for the clock differences)。实际上,除了PCIe,弹性缓存还广泛应用于其它的高速串行接口——USB、InfiniBand、Fibre Channel、Gigabit Ethernet等基于SerDes的应用。

二、详细解析

由于PCIe采用的基于8b/10b的嵌入式源同步时钟,接收端存在两个时钟域:

1、是通过CDR(Clock Data Recovery)从数据流中解析出来的时钟,用该时钟对数据进行采样;

2、是本地时钟域,用于其他的逻辑的。借助弹性缓存(FIFO),可以实现数据在这两个时钟域的转换。

PCIe的时钟是嵌入到差分信号中的,PCIe总线在训练之初会完成一个bit lock,在这个过程中链路上会传输一段0和1间隔序列,即是连续的高低电平,就是用来给Receiver提取时钟的。Receiver提到到时钟后,才能够继续捕获一位一位的数据,也就是做bit的识别,再往后则是做多个bit的识别,即序列识别。

在PCIe Transmitter里会进行编码操作,这个编码即是让0和1的数量更加均衡,以防止总线时钟丢失。另外,总线处于空闲状态时,也会持续传输时钟对齐码流,以防止丢了时钟,突然有数据过来的时候找不着北。

2.1 实例解析

以PCIe Gen1为例,链路上的数据速率为2.5Gbps。但实际上,任何晶振(或者其他频率发生器)都是有误差的,PCIe Spec允许的误差范围为±300ppm(Parts Per Million)。即,链路上实际的频率范围为2.49925GHz~2.50075GHz。借助弹性缓存,通过删除或者插入SKP Ordered Set可以消除链路频率误差的影响。如下图所示:

需要注意的是PCIe Spec并没有规定弹性缓存的具体位置,设计者可以将弹性缓存放在8b/10b解码器之前,也可以把弹性缓存放在8b/10b解码器之后。不过,Mindshare的建议是将弹性缓存放置于8b/10b解码器之前的。

2.2 具体实现过程

1、插入SKP序列

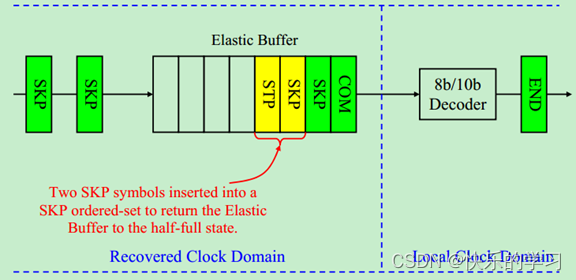

当本地时钟域的时钟(Local Clock)的速度比数据流通过CDR解析出的时钟(Recovered Clock)的时钟要快时,且弹性缓存即将被读空之前,可以向SKP Ordered Set中插入1~2个SKP,填充buffer。如下图所示:

2、移除SKP序列

2、移除SKP序列

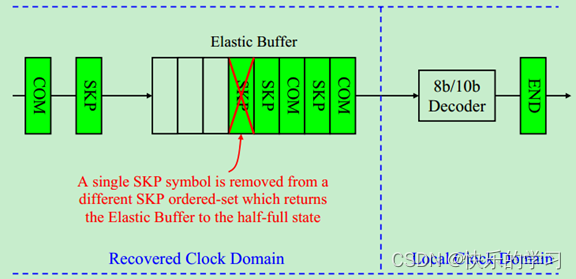

当本地时钟域的时钟(Local Clock)的速度比数据流通过CDR解析出的时钟(Recovered Clock)的时钟要慢时,且弹性缓存即将溢出之前,SKP发挥作用的方式很简单,当数据进入的时钟频率(CDR解析出的时钟频率)大于数据出的时钟频率(本地时钟频率)时,数据进的比走的快,会导致进入buffer的数据累积越来越多,甚至可能溢出丢失,在这种情况下,可以从SKP Ordered Set中移除1~2个SKP,将位置空出来,那么数据就不会溢出了。如下图所示:

需要特别注意的是,Intel提出的PIPE规范(并非PCI-SIG强制的规范,具体参考前面关于PIPE的文章)中,只允许每次从一个SKP Ordered Set中插入或者移除一个SKP。如果需要插入或者移除两个SKP,则需要对两个SKP Ordered Set进行操作。如下图所示:

三、总结

通过抽走和插入SKP序列的方式,可以解决两边时钟频率差异的问题。弹性缓冲自身有状态检测功能,能够不断监测buffer内的数据量,从而做出响应,具体操作的SKP数量,根据不同厂家的controller设计而不同。