《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(11)

接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(10)

4.2 PCIe体系结构的组成部件

PCIe总线作为处理器系统的局部总线,其作用与PCI总线类似,主要目的是为了连接处理器系统中的外部设备,当然PCIe总线也可以连接其它处理器系统。在不同的处理器系统中,PCIe体系结构的实现方法略有不同。但是在大多数处理器系统中,都使用了RC、Switch和PCIe-to-PCI桥这些基本模块连接PCIe和PCI设备。在PCIe总线中,基于PCIe总线的设备,也被称为EP(Endpoint)。

4.2.1 基于PCIe架构的处理器系统

在不同的处理器系统中,PCIe体系结构的实现方式不尽相同。PCIe体系结构以Intel的x86处理器为蓝本实现,已被深深地烙下x86处理器的印记。在PCIe总线规范中,有许多内容是x86处理器独有的,也仅在x86处理器的Chipset中存在。在PCIe总线规范中,一些最新的功能也在Intel的Chipset中率先实现。本节将以一个虚拟的处理器系统A和PowerPC处理器为例简要介绍RC的实现,并简单归纳RC的通用实现机制。

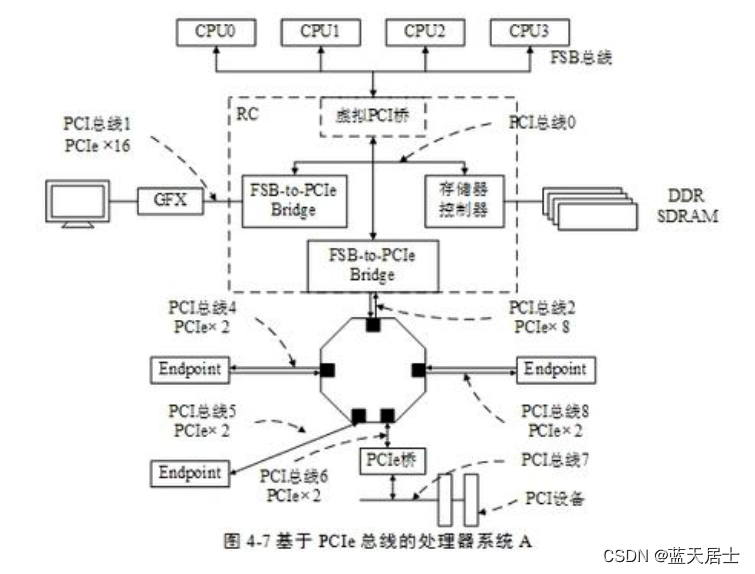

1. 处理器系统A

在有些处理器系统中,没有直接提供PCI总线,此时需要使用PCIe桥,将PCIe链路转换为PCI总线之后,才能连接PCI设备。在PCIe体系结构中,也存在PCI总线号的概念,其编号方式与PCI总线兼容。

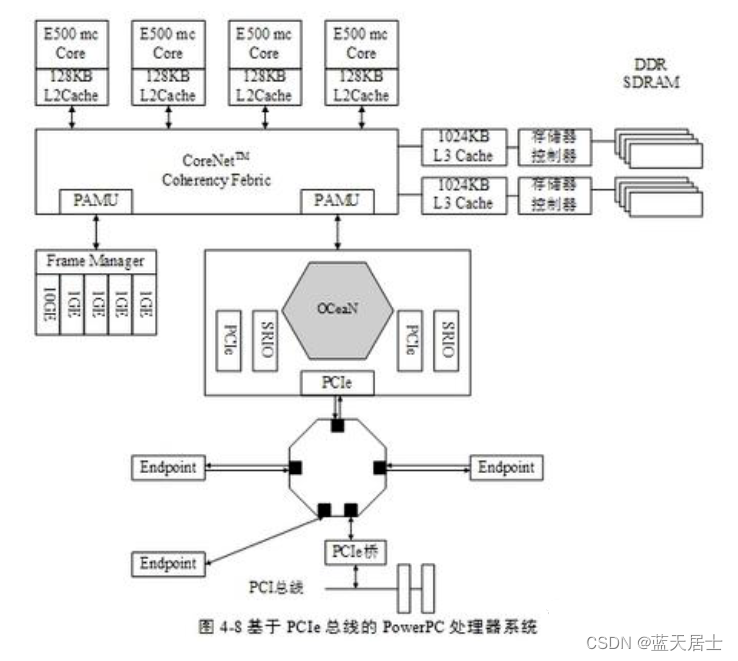

2. PowerPC处理器

PowerPC处理器挂接外部设备使用的拓扑结构与x86处理器不同。在PowerPC处理器中,虽然也含有PCI/PCIe总线,但是仍然有许多外部设备并不是连接在PCI总线上的。在PowerPC处理器中,PCI/PCIe总线并没有在x86处理器中的地位。在PowerPC处理器中,还含有许多内部设备,如TSEC(Three Speed Ethenet Controller)和一些内部集成的快速设备,与SoC平台总线直接相连,而不与PCI/PCIe总线相连。在PowerPC处理器中,PCI/PCIe总线控制器连接在SoC平台总线的下方。

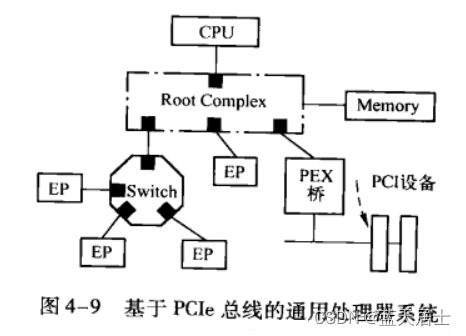

3. 基于PCIe总线的通用处理器结构

在不同的处理器系统中,RC的实现有较大差异。PCIe总线规范并没有规定RC的实现细则。在有些处理器系统中,RC相当于PCIe主桥,也有的处理器系统也将PCIe主桥称为PCIe总线控制器。而在x86处理器系统中,RC除了包含PCIe总线控制器之外,还包含一些其它组成部件,因此RC并不等同于PCIe总线控制器。

如果一个RC中可以提供多个PCIe端口,这种RC也被称为多端口RC。如MPC8572处理器的RC可以直接提供3条PCIe链路,因此可以直接连接3个EP。如果MPC8572处理器需要连接更多EP时,需要使用Switch进行链路扩展。

而在x86处理器系统中,RC并不是存在于一个芯片中,如在Montevina平台中,RC由MCH和ICH两个芯片组成。本节并不对x86和PowerPC处理器使用的PCIe总线结构做进一步讨论,而只介绍这两种结构的相同之处。一个通用的,基于PCIe总线的处理器系统如图4-9所示:

上图所示的结构将PCIe总线端口、存储器控制器等一系列与外部设备有关的接口都集成在一起,并统称为RC。RC具有一个或者多个PCIe端口,可以连接各类PCIe设备。PCIe设备包括EP(如网卡、显卡等设备)、Switch和PCIe桥。

PCIe总线采用端到端的连接方式,每一个PCIe端口只能连接一个EP,当然PCIe端口也可以连接Switch进行链路扩展。通过Switch扩展出的PCIe链路可以继续挂接EP或者其它Switch。

更多内容请看下回。