基于FPGA的图像锐化算法(USM)设计

免费获取源码请关注微信号《FPGA学习笔记册》!

1.图像锐化算法说明

图像锐化算法在实际的图像处理应用很广泛,例如:医学成像、工业检测和军事领域等;它的作用就是将模糊的图像变的更加清晰。常用的图像锐化算法有拉普拉斯算子、sobel算法,但是它们的效果不是很好,USM反锐化算法可以看做是拉普拉斯算子的加强版,算法具有相当的锐化能力与可控性。

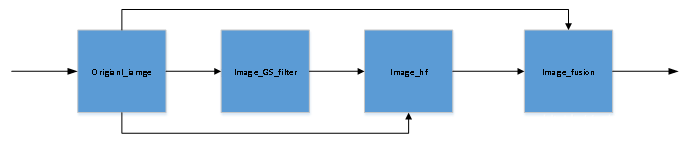

该算法的设计原理如下所示:

首先对原图做高斯模糊(半径可调),提取低频成分;然后把原始图像减去低频成分获得高频成分(间接提取高频);再对高频成分与阈值(阈值可调)比较,比阈值大的才进行增强(提高抗噪声性能);最后和原图进行叠加运算。

通过maltab对图像进行USM算法处理后的图像对比,左边图像为原始图像,右边图像为USM算法处理后的图像;可以发现画红框的地方通过算法处理后图像的边缘变的清晰了,图像轮廓细节更加明显。

2.FPGA系统框架设计

2.1图像高斯滤波程序设计

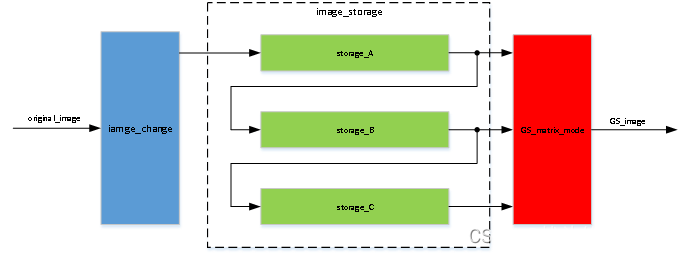

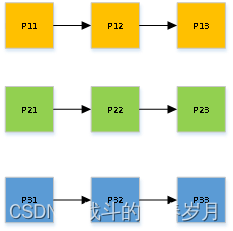

图像高斯滤波算法主要由三个模块组成:image_chage、image_storage和GS_matrix_mode;Image_chage的作用对输入的图像数据补充虚拟边缘数据;Image_storage的作用实现3*3模板数据缓存;GS_matrix_mode的作用是对输入对3*3模板内的数据进行运算。

2.1 .1image_change模块说明

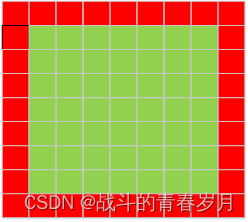

根据图像均滤波算法的原理介绍,我们可以发现一个问题就是一张图像的外围周边的像素是无法进行算法处理,通过算法处理后的图像的分辨率降低了。如下图所以,周边为红色的像素都是无法参与算法运算的,当3*3的模板在整幅图像进行算法处理后,获得的图像的大小就变成了绿色像素的范围了。在实际的图像处理中有两种办法可以解决这个问题:

第一个办法就是根据算法的模板大小,配置相机吧原始图像分辨率变大一些,保证算法处理后的图像分辨率为最终想要的分辨率;

第二种办法就是对原始图像进行修改,人工将分辨率变大,从而保证获得的分辨率为最终想要的分辨,我们这里主要讲第二种办法。

举例:原始图像的分辨率是7*3,也就是每行7个像素,一共三行数据;采用的均值滤波模板是3*3的。为了保证图像的边缘数据能够得到处理,我们需要对每行的左右两边各添加一个虚拟的像素(数值为0),这就能保证每行数据的原始像素都能得到算法运算,同时保证了算法运算后每行的数据的个数不变;同理对行数上我们也要添加两行虚拟行数保证算法运算后的行数不边;image_change模块就是按照这个思路设计的。

备注:对行数的处理,本模块在原始图像的结尾处添加一行,对于开头的添加的虚拟行通过后面的模块来实现。

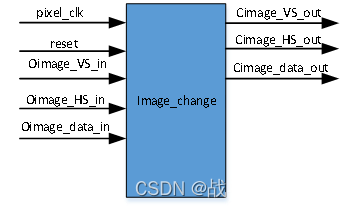

- 1. image_change程序接口

| 名称 | 方向 | 位宽 | 说明 |

| piexl_clk | Input | 1 | 工作时钟 |

| reset | Input | 1 | 复位信号(active high) |

| Oimage_VS_in | Input | 1 | 原始图像输入的场信号 |

| Oimage_HS_in | Input | 1 | 原始图像输入的行信号 |

| Oimage_data_in | Input | WIDTH | 原始图像数据信号 |

| Cimage_VS_out | Output | 1 | 算法处理后的场信号 |

| Cimage_HS_out | Output | 1 | 算法处理后的行信号 |

| Cimage_data_out | Output | WIDTH | 算法处理后的数据 |

测试用例:

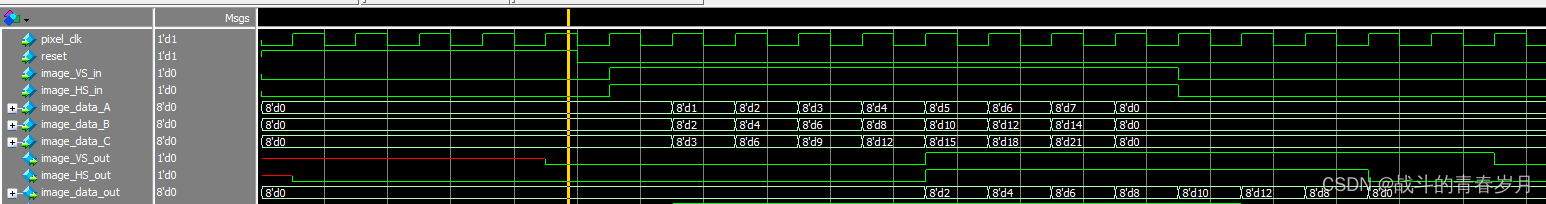

输入一行数据,该行数据共7个有效数(1~7)运算结果:每行数据的两边各添加一个像素数值为0,一行数据就变成了9个像素,同时行数变成两行,补充的一行填充的数据全部为0。

仿真结果:通过仿真结果证明了我们的程序设计是正确的!

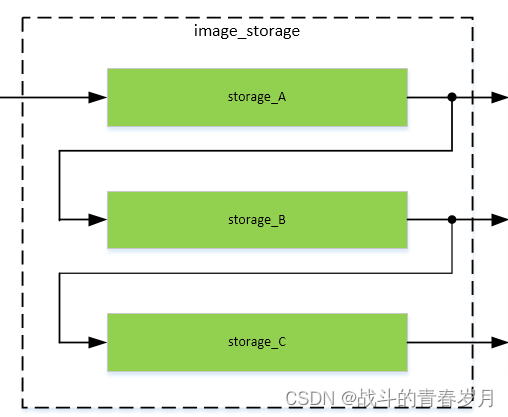

2.1.2 image_storage模块说明

在真实的视频图像数据中,数据都是一行行的输出,为了能够实现3*3模板的运算,需要对图像数据进行缓存,从而模拟出三行并行数据。

实现这个缓存常用的方法就是调用FPGA内部的缓存资源来实现,一般大家常用的就是shift_ram、fifo、双端口ram,其中shift_ram是最常用的(因为操作简单);这次设计没有调用上面的资源,我是自己设计了一个shift_ram的IP来实现,一个原因是block_ram缓存资源在FPGA中太宝贵了,一定要省着用;另一个原因是自己设计的IP可以在不同厂家的FPGA芯片中使用,移植起来比较方便(我了解的卖IP核的都是这样搞,大家可以尝试一下)。Shift_ram的IP设计,我采用了Verilog语法中的generate语句实现的,该语句操作简便灵活,我个人认为FPGA工程师必须掌握的,大家可以学习一下。

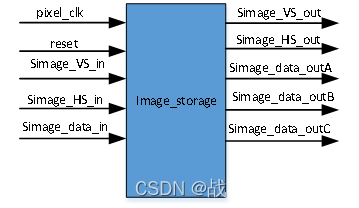

- 1. image_storage程序接口

| 名称 | 方向 | 位宽 | 说明 |

| piexl_clk | Input | 1 | 工作时钟 |

| reset | Input | 1 | 复位信号(active high) |

| Simage_VS_in | Input | 1 | 原始图像输入的场信号 |

| Simage_HS_in | Input | 1 | 原始图像输入的行信号 |

| Simage_data_in | Input | WIDTH | 原始图像数据信号 |

| Simage_VS_out | Output | 1 | 算法处理后的场信号 |

| Simage_HS_out | Output | 1 | 算法处理后的行信号 |

| Cimage_data_outA | Output | WIDTH | 算法处理后的数据 |

| Cimage_data_outB | Output | WIDTH | 算法处理后的数据 |

| Cimage_data_outC | Output | WIDTH | 算法处理后的数据 |

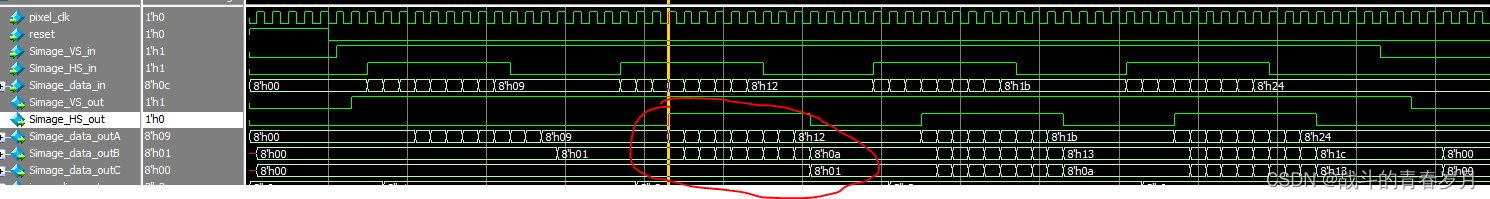

仿真结果:

如下图所示,红圈内的数据是输出的第一组3*3模板数据,Cimage_data_outC输出的数据全部为零,前面说过给原图添加的第一行虚拟数据在本模块实现。通过仿真验证了本模块设计是正确的。

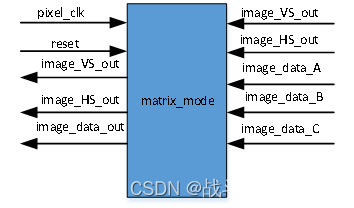

2.1.3 matrix_mode模块说明

该模块的作用就是设计一个3*3的模板,当iamge_storage模块输出9个数据时,该模块就开始计算出结果。设计思路如下图所示,就是在要设计9个缓存寄存器通过打拍实现计算功能。

- 1. Matrix_mode程序接口

| 名称 | 方向 | 位宽 | 说明 |

| piexl_clk | Input | 1 | 工作时钟 |

| reset | Input | 1 | 复位信号(active high) |

| image_VS_in | Input | 1 | 原始图像输入的场信号 |

| image_HS_in | Input | 1 | 原始图像输入的行信号 |

| image_data_out | Output | WIDTH | 原始图像数据信号 |

| image_VS_out | Output | 1 | 算法处理后的场信号 |

| image_HS_out | Output | 1 | 算法处理后的行信号 |

| image_data_A | Input | WIDTH | 算法处理后的数据 |

| image_data_B | Input | WIDTH | 算法处理后的数据 |

| image_data_C | Input | WIDTH | 算法处理后的数据 |

仿真结果:如下图所示,仿真结果和均值滤波算法原理是一致的,就是把目标周边的8个像素进行加法运算后求其平均值。

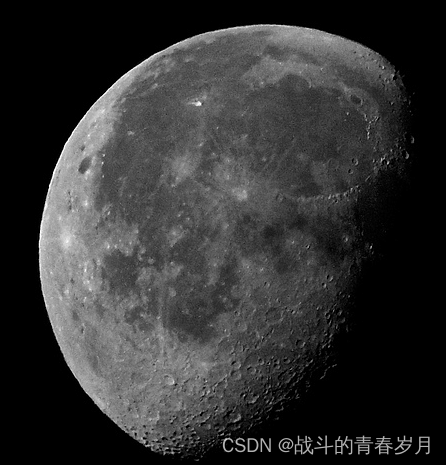

FPGA程序处理的数据在maltab中恢复为图像后,效果与maltab处理的结果一样,图像达到了锐化的效果。

上图右边为锐化算法处理后的结果,月球坑的边界更加清晰。