光纤接口简介

光纤接口简介

学习自正点原子FPGA教程

光纤接口是用来连接光纤线缆的物理接口,简称为光口。其原理是利用了光从光密介质进入光疏介质从而发生了全反射。通常有 FC、 SC、 ST、 LC、 D4、 DIN、 MU、 MT 等等各种形式接口,下面介绍下常用的几种连接器接口。

1、SC 型光纤接口:

这是一种由日本NTT 公司开发的光纤连接器。其外壳呈矩形,采用的插针与耦合套筒的结构尺寸和FC型完全相同。其中插针的端面多采用 PC或 APC型研磨方式;紧固方式是采用插拔销闩式,不需旋转。此类连接器价格低廉,插拔操作方便,介入损耗波动小, 抗压强度较高,安装密度高。 ST和 SC接口是光纤连接器的两种类型,对于 10Base-F连接来说,连接器通常是 ST类型的,对于 100Base-FX来说,连接器大部分情况下为 SC类型的。 ST连接器的芯外露,SC连接器的芯在接头里面。

2、FC型 光纤接口

这种连接器最早是由日本NTT研制。 FC是 Ferrule Connector的缩写,表明其外部加强方式是采用金属套,紧固方式为螺丝扣。最早, FC类型的连接器采用的陶瓷插针的对接。此类连接器结构简单,操作方便,制作容易,但光纤端面对微尘较为敏感,且容易产生菲涅尔反射,提高回波损耗性能较为困难。后来,对该类型连接器做了改进,采用对接端面呈球面的插针 (PC),而外部结构没有改变,使 得插入损耗和回波损耗性能有了较大幅度的提高。

3、LC型 光纤接口

LC型连接器是著名 Bell (贝尔 )研究所研究开发出来的,采用操作方便的模块化插孔 (RJ) 闩锁机理制成。其所采用的插针和套筒的尺寸是普通 SC、 FC等所用尺寸的一半,为 1.25mm。这样可以提高光纤配线架中光纤连接器的密度。目前,在单模 SFF方面, LC类型的连接器实际已经占据了主导地位,在多模

方面的应用也增长迅速。

4、ST型连接器:

ST连接器,是一种快速连接头,由中国广东深圳市科腾光电技术有限公司开发研制。广泛应用于光配线架 (ODF)、 光纤通信设备等。光纤适配器用于光纤活动连接器之间的接续、耦合。根据光纤活动连接器的连接头选择型号。利用良好烧结技术确保质量优异和高强度、高稳定度。

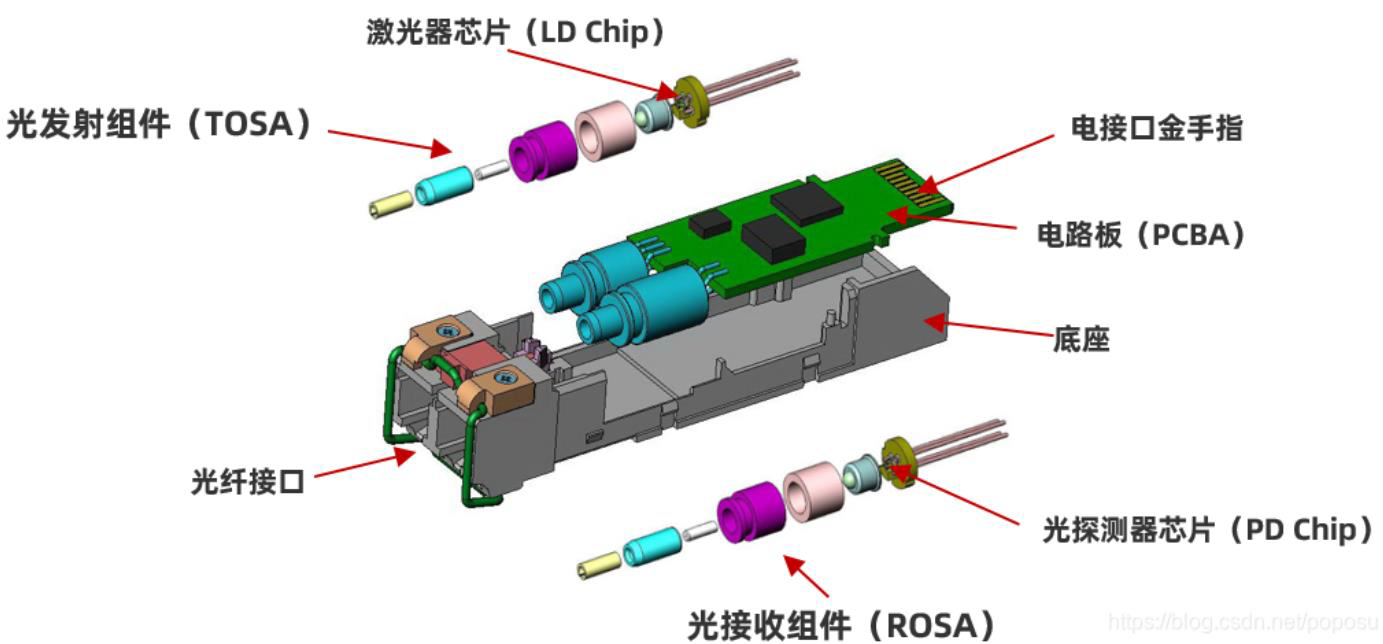

光模块组件

从上图中可以看到:一个光模块,通常由光发射器件(TOSA,含激光器)、光接收器件 (ROSA,含光探测器)、功能电路和光(电)接口等部分组成。其中在发射端,驱动芯片对原始电信号进行处理,然后驱动半导体激光器( LD)或发光二极管 LED)发射出调制光信号;在接收端,光信号进来之后,由光探测二极管转换为电信号,经前置放大器后输出电信号。

常见光模块的类型:

| 分类方式 | 类别 |

|---|---|

| 封装类型 | 1×9、GBIC、X2、XENPAK、XFP、SFP、SFP+、SFP28、QSFP、QSFP28、CFP、CFP2、QSFP-DD、OSFP等 |

| 速率 | 10Mbps、100Mbps、155Mbps、622Mbps、1.25Gbps、2.125Gbps、4.25Gbps、10Gbps、25Gbps、50Gbps、100Gbps、400Gbps等 |

| 波长 | 850nm、1310nm、1490nm、1550nm、CWDM、DWDM等 |

| 模式 | 单模(黄色)、多模(橙黄色、蓝绿色) |

| 距离 | 100m、300m、550m、10km、20km、40km、80km、120km、160km |

| 调制格式 | NRZ、PAM4、DP-QPSK/n-QAM等 |

| 是否支持WDM | 灰光模块(不支持WDM)、彩光模块(支持WDM) |

| 光接口工作模式 | 双纤双向(Duplex)、单纤双向(BiDi) |

| 激光器类型 | 垂直腔面发射激光器(VCSEL)、法布里-珀罗激光器(FP)、分布式反馈激光器(DFB)、电吸收调制激光器(EML)等 |

| 光探测器类型 | PIN结二极管(PIN)、雪崩光电二极管(APD) |

| 连接器接头 | FC、SC、ST、LC、MU、MTRJ |

| 使用性 | 热插拔(GBIC、SFP、XFP、XENPAK)和非热插拔(1*9、SFF) |

| 工作温度 | 商业级(0~70°C)、延展温度(-20~85°C)、工业级(-40~85°C) |

建议使用光模块SFP类型, SFP是 SMALL FORM PLUGGABLE的缩写,可以简单的理解为 GBIC的升级版本。 SFP模块体积比 GBIC模块减少一半,可以在相同的面板上配置多出一倍以上的端口数量。 SFP模块的其他功能基本和 GBIC一致。未来的光模块必须支持热插拔,即无需切断电源,模块即可以与设备连接或断开,由于光模块是热插拔式的,网络管理人员无需关闭网络就可升级和扩展系统,对在线用户不会造成什么影响。热插拔性也简化了总的维护工作,并使得最终用户能够更好地管理他们的收发模块。同时,由于这种热交换性能,该模块可使网络管理人员能够根据网络升级要求,对收发成本、链路距离以及所有的网络拓扑进行总体规划,而无需对系统板进行全部替换。支持这热插拔的光模块目前有 GBIC和 SFP,由于 SFP与 SFF的外型

大小差不多,它可以直接插在电路板上, 在封装上较省空间与时间,且应用面相当广,因此,其未来发展很值得期待,甚至有可能威胁到 SFF的市场。

高速收发器 GTH

xilinx公司不同系列的高速串行收发器的类型和速率的对比:

| 器件系列 | GTP | GTR | GTX | GTH | GTY | GTZ | GTM | 最大收发器(个) | 峰值带宽(Gb/s) |

|---|---|---|---|---|---|---|---|---|---|

| Spartan 6 | 3.20 | / | / | / | / | / | / | 8 | 51 |

| Zynq 7000 | / | / | / | / | / | / | / | 16 | 400 |

| Zynq™ UltraScale+ | / | 6.00 | 12.50 | 16.30 | 32.75 | / | / | 4/44/28 | 3268 |

| Artix™ 7 | 6.60 | / | 12.50 | / | / | / | / | 16 | 211 |

| Kintex 7 | / | / | 12.50 | / | / | / | 28.05 | 32 | 800 |

| Virtex 7 | / | / | 12.50 | 13.10 | / | / | / | 59/96/16 | 2784 |

| Kintex UltraScale | / | / | / | 16.30 | / | / | / | 64 | 2086 |

| Virtex UltraScale | / | / | / | 16.30 | 30.50 | / | / | 60/60 | 5616 |

| Kintex™ UltraScale+ | / | / | / | 16.30 | 32.75 | / | / | 44/32 | 3268 |

| Virtex™ UltraScale+ | / | / | / | / | 32.75 | / | / | 128/48 | 8384 |

| Versal Premium 系列 | / | / | / | / | 32.75 | 112.00 | / | 28/70 | 9040 |

| Versal ACAP | / | / | / | / | / | 58.00 | 58.00 | 44/52 | 6032 |

UltraScale 架构中的GTH 收发器是节能型收发器,支持从500mb /s 到16.375 Gb/s 的线路速率。一般应用于PCIE、SFF、SFP+、XAUI、SATA 等高速接口设计。

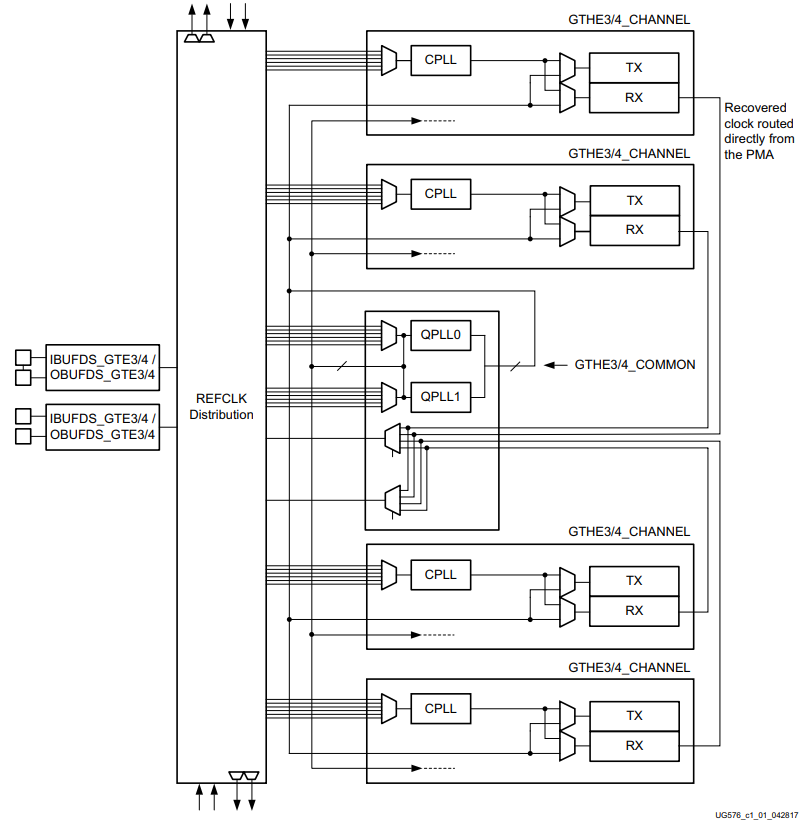

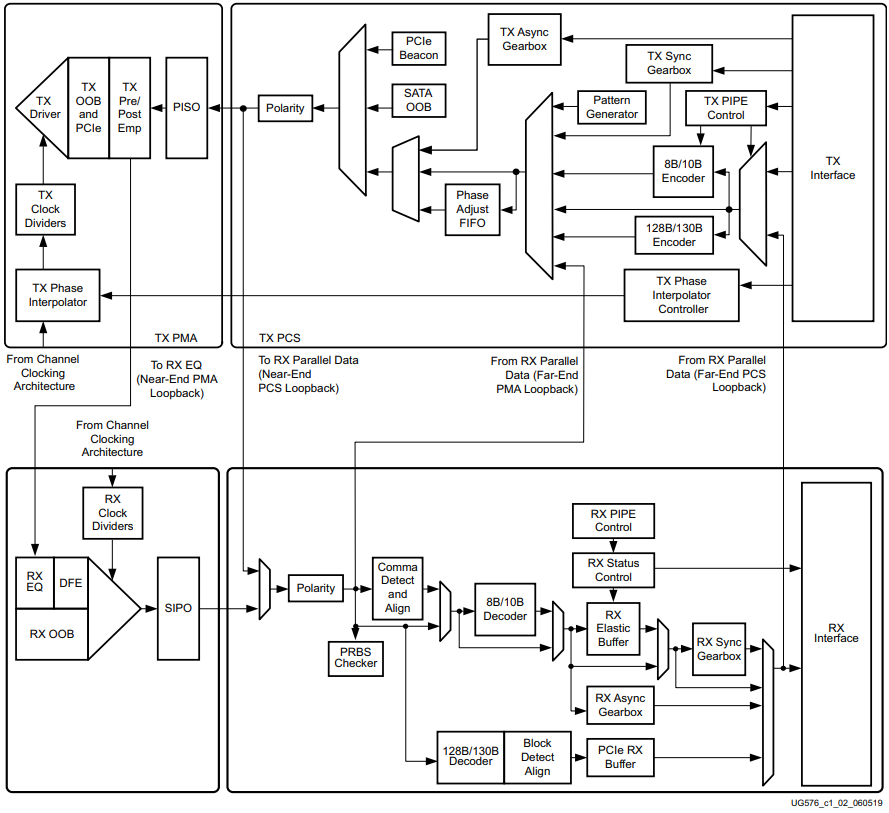

FPGA 开发板板载的FPGA 器件提供了一组高速收发器GTH。GTH 接口的结构图如下所示:

从上图中可以看到,GTH 接口每4 对组成一个Quad(一个BANK),在这个Quad 当中每一对高速收发器称之为Channel,每个Channel 都拥有一个自己私有的时钟锁相环CPLL,用来给GTH 接口提供参考时钟。除了CPLL 之外,在这个Quad 当中还有两个共享时钟锁相环QPLL0 和QPLL1。QPLL 相比较于CPLL最大的区别就是支持的时钟速率不相同,一般 10Gbit/s以上的通信速率选择 QPLL。在这个 Quad外围还有了 IBUFDS和 OBUFDS,在 GTH通信过程中,外围物理引脚 PIN都是差分信号,所以需要经过 BUFDS对信号进行差分和单端的相互转换。在 GTH中对 CPLL来说,支持的线速率位 2.0GHz到6.25GHZ之间,而对于 QPLL来说, QPLL0支持的线速率为 9.8GHz-16.375GHz,QPLL1支持的线速率为8.0GHz~13.1GHz。

要想正确的使用GTH首先就要了解它整个时钟的拓扑结构。对于一个 Quad来说每个 CPLL都属于单独的 Channel模块,它只能给自己的私有通道提供参考时钟。而 QPLL是共享时钟锁相环属于 Common模块,可以给整个 Quad的所有通道提供参考时钟。那么 CPLL和 QPLL它们自己的源时钟又来自哪里呢?

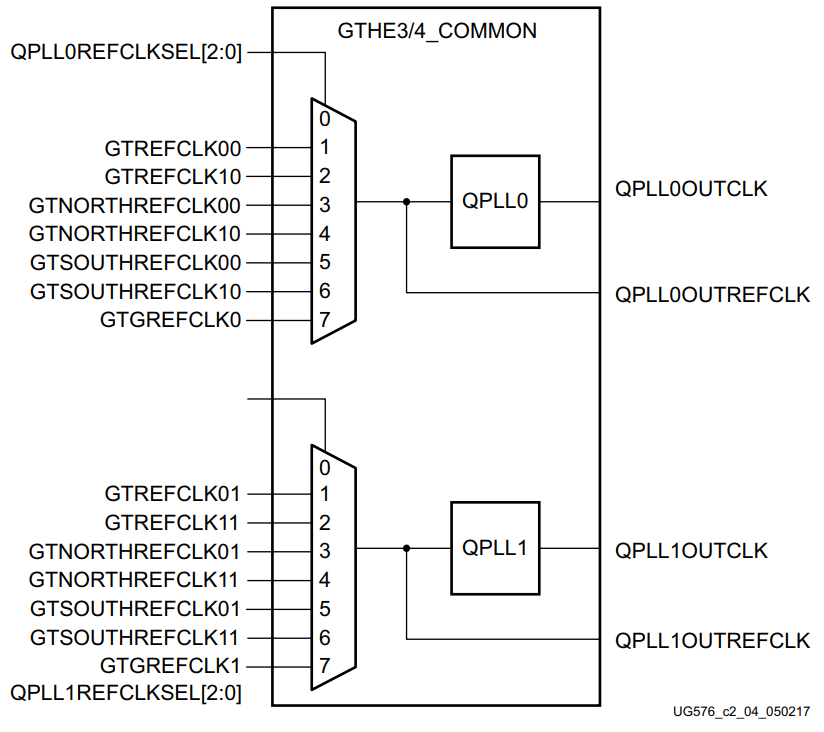

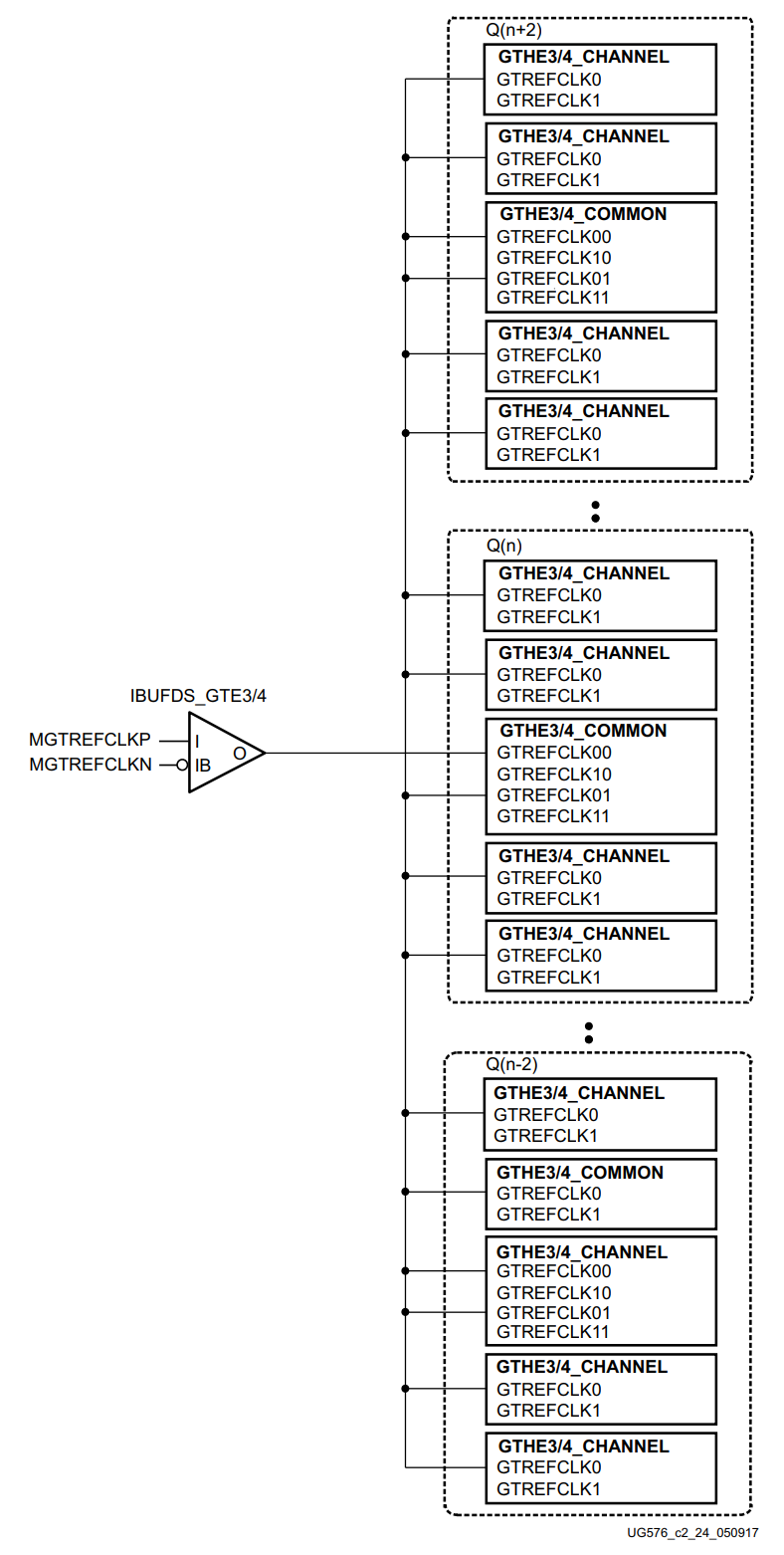

如下图所示:

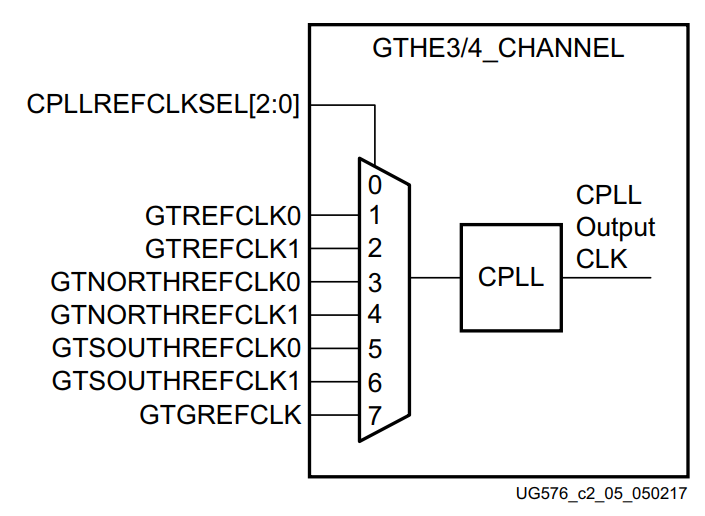

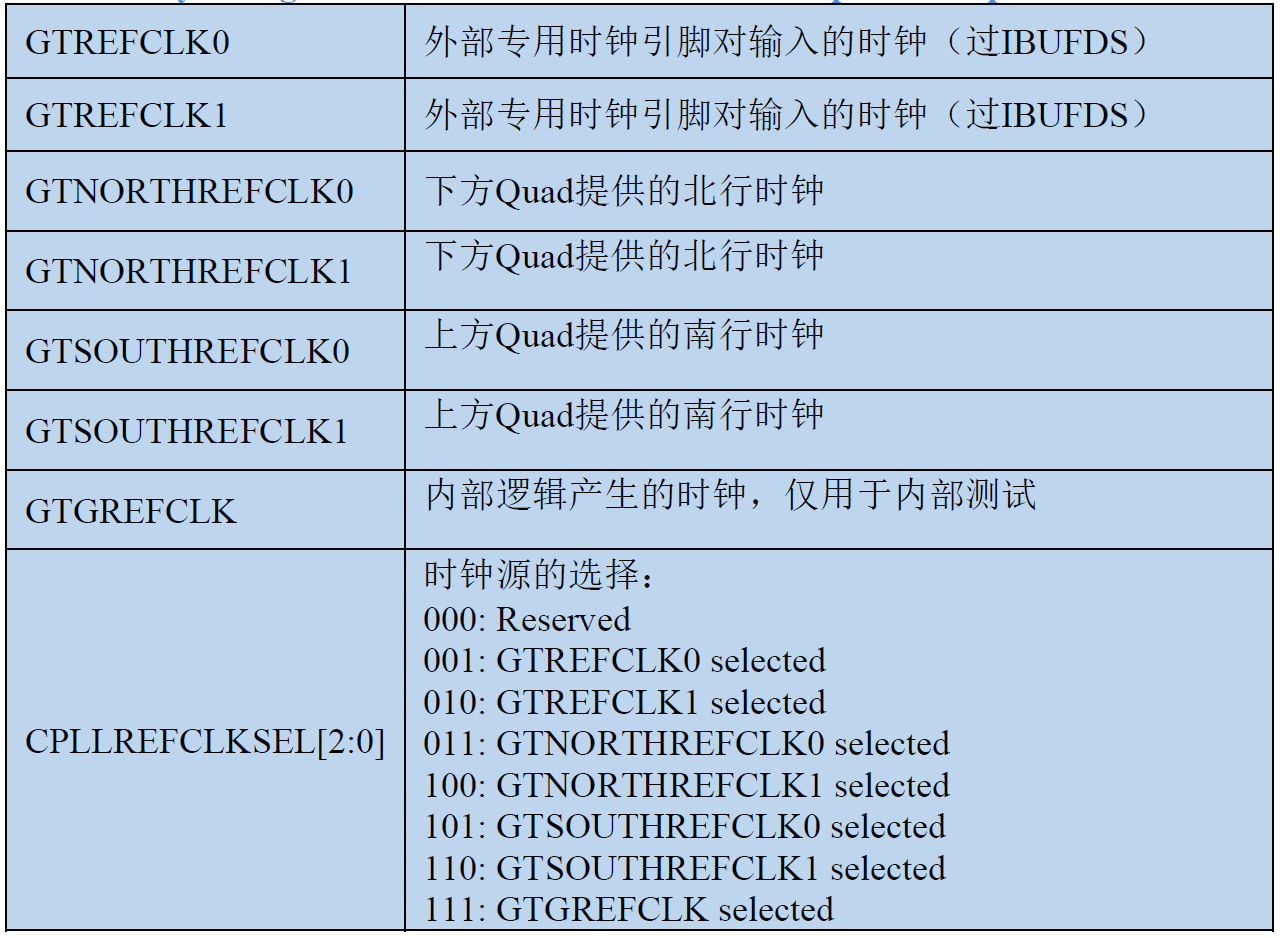

从上图中可以看到无论是QPLL还是 CPLL它的源时钟都有 7路来源,具体说明如下表所示(这里以CPLL举例):

从上表中可以看到对于CPLL来说总共七路时钟来源,两路来自外部时钟引脚对,经过 IBUFDS后转换成单端时钟信号就可以接入 CPLL;还有四路来自上下 Quad,当 FPGA中不止一个 Quad的时候当前Quad中的 GTH参考时钟可以来自上面的两个 Quad也可以来自下面的两个 Quad,注意最多只能跨两个Quad,最后一路时钟来源是内部逻辑产生的时钟,只能用作内部测试。

从上表中可以看到对于CPLL来说总共七路时钟来源,两路来自外部时钟引脚对,经过 IBUFDS后转换成单端时钟信号就可以接入 CPLL;还有四路来自上下 Quad,当 FPGA中不止一个 Quad的时候当前Quad中的 GTH参考时钟可以来自上面的两个 Quad也可以来自下面的两个 Quad,注意最多只能跨两个Quad,最后一路时钟来源是内部逻辑产生的时钟,只能用作内部测试。

QPLL与 CPLL时钟来源图

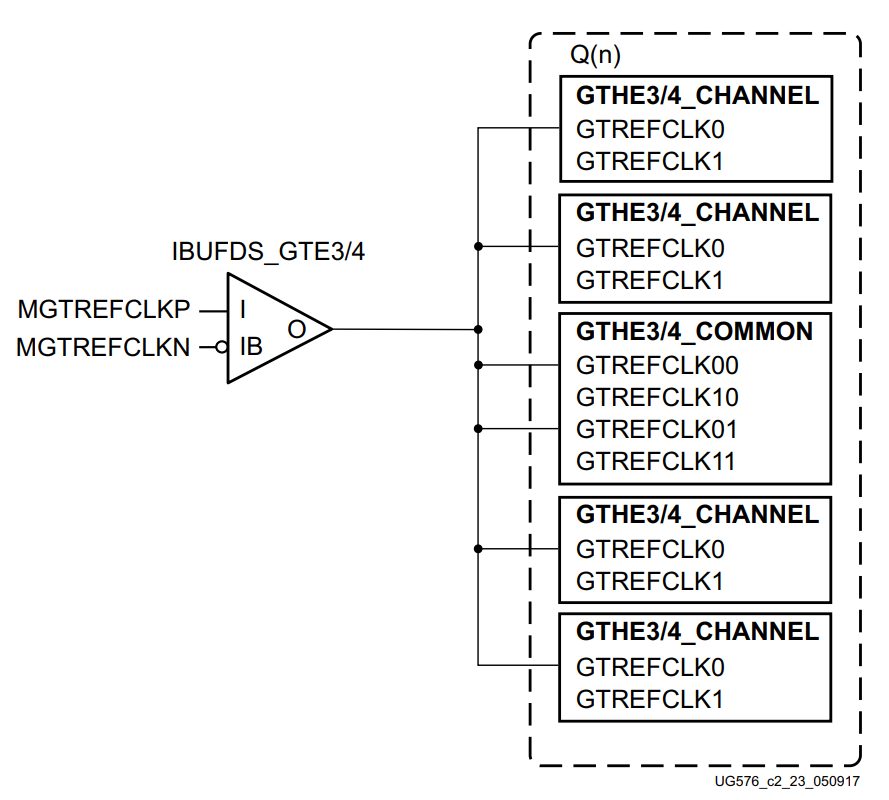

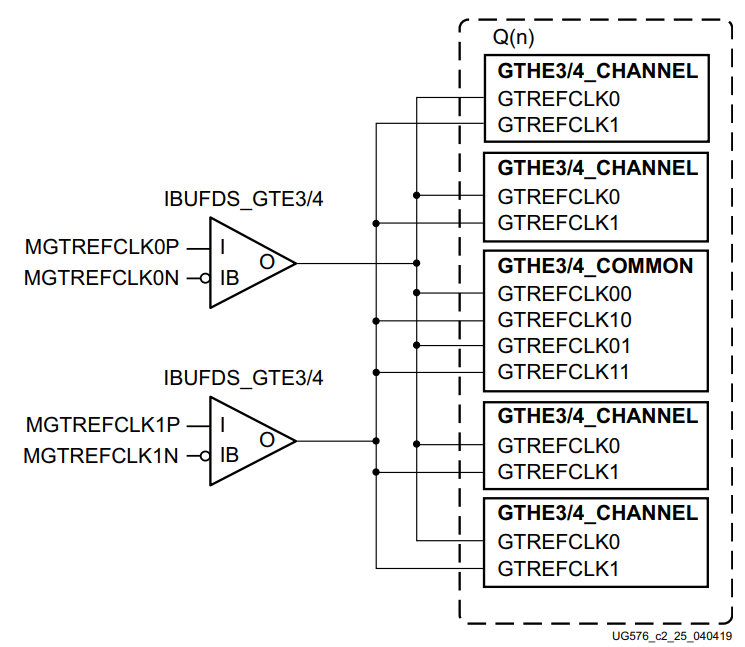

了解完整个Quad的时钟拓扑结构后我们再来了解一下时钟的使用模式,主要分为两种使用模式,一种是 Single外部输入模式,另一种是 Multiple外部输入模式,如下图所示:

Single外部输入模式

Multiple外部输入模式

从上图中很容易就能理解Single和 Multiple这两种模式的区别,主要就是外部输入时钟的数量区别。

了解完时钟拓扑结构后我们再来看一下每个Channel的结构,单个 Channel的结构图如下所示:

GTH Channel结构图

从上图中可以看到单个Channel由发送接口和接收接口组成,每个接口又分为两部分结构,这两部分结构分别是 PMA和 PCS。 PMA和 PCS内部又由许多功能模块构成,如下表所示:

PCS和PMA组的结构和功能

| Group | Structure | Feature |

|---|---|---|

| PCS | TX Interface | GTH收发器的发送数据通道(属性可配置) |

| TX 8B/10B Encoder | 8B/10B编码器 | |

| TX Synchronous Gearbox | TX同步变速箱,用于高速通信协议支持64B/66B编码 | |

| TX Phase | 相位插补器主要是对PMA数据进行微调 | |

| Phase Adjust FIFO | 相位调整的缓冲FIFO,主要用来处理数据跨时钟域的相位调整 | |

| TX Pattern Generator | 测试数据生成器,用于产生伪随机比特序列。伪随机比特序列(PRBS)是一种常用的高速链路信号完整性测试方法。 这些序列看起来是随机的,但是具有特定的属性,可以用来衡量链路的质量。 | |

| TX Polarity Control | TX数据极性控制,如果TXP和TXN差分走线在PCB上意外交换,则GTH收发器会相应调整以正确发送数据。 | |

| RX Polarity Control | RX数据极性控制,如果RXP和RXN差分走线在PCB上意外交换,则GTH收发器会相应调整以正确接收数据。 | |

| RX PRBS Checker | PRBS校验器,对RX端接收的PRBS序列进行校验。 | |

| RX 8B/10B Decoder | 8B/10B解码器 | |

| RX Elastic Buffer | GTH收发器包含一个RX弹性缓冲器,用来解决RXCLK和RXUSRCLK两个时钟域之间的数据跨域问题。 | |

| RX Synchronous Gearbox | RX同步变速箱,用于高速通信协议支持64B/66B、64B/67B编码。 | |

| RX Interface | GTH收发器的接收数据通道(属性可配置)。 | |

| PMA | RX DFE | 离散自适应高速滤波器 |

| PISO/SIPO | 串并转换 | |

| TX/RX OOB | 每个GTH收发器都支持生成串行ATA (SATA)、串行附加小型计算机系统接口(SCSI, SAS)规范中描述的带外 (OOB) 序列,以及PCI Express规范中描述的信标。 | |

| TX Driver | TX驱动器是一个高速差分输出缓冲器。 |

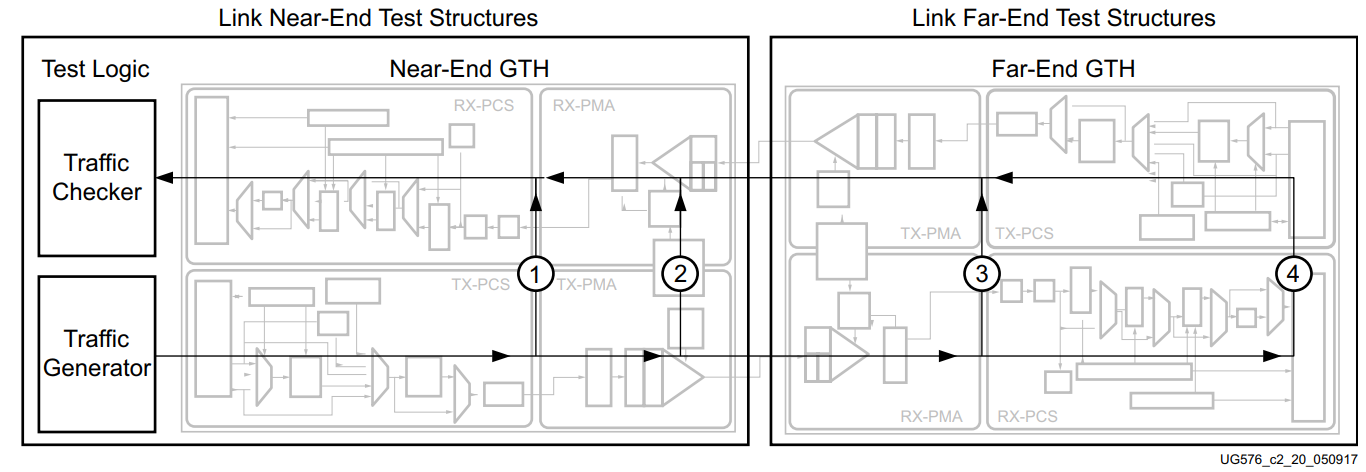

了解完他的内部结构之后我们再来看一下收发器接收和发送之间的数据回环。GTH的数据回环可以分为近端回环和远端回环,近端回环中又分为近端 PCS回环和近端 PMA回环,远端回环也一样分为远端PCS回环和远端 PMA回环。回环的数据一般是使用内部的模式生成器产生 PRBS数据然后经过回环路径

后到达模式检查器去检查接收到的数据是否和生成的数据一致,从而判断通信路径的通信性能 。 回环路径如下图所示:

回环路径图

从上图中可以看到路径1就是近端 PCS回环,也就是单个收发器内部的 PCS之间回环,这种回环几乎不使用,因为单纯在单个收发器的内部逻辑功能块之间回环并不能说明通道的性能;路径 2近端 PMA回环是单个通道之间 TX和 RX的数据回环可以验证单个通道接收和发送的通信性能;路径 3和 4是远端的 PMA与 PCS回环,可以验证对向的 GTH性能。本节实验使用了两个 GTH收发器,所以在进行光口眼图验证的时候跑的就是远端 PCS回环。

关于GTH收发器总结一下就是 GTH的接收和发送通道都由 PMA和 PCS两部分组成,其中 PMA的主要功能就是进行串并转换和模拟电路的处理,而 PCS由诸多逻辑功能块组成,可以对并行数字电路的数据进行各种编码处理,相位偏移处理,跨时钟域数据缓冲处理等等。