|

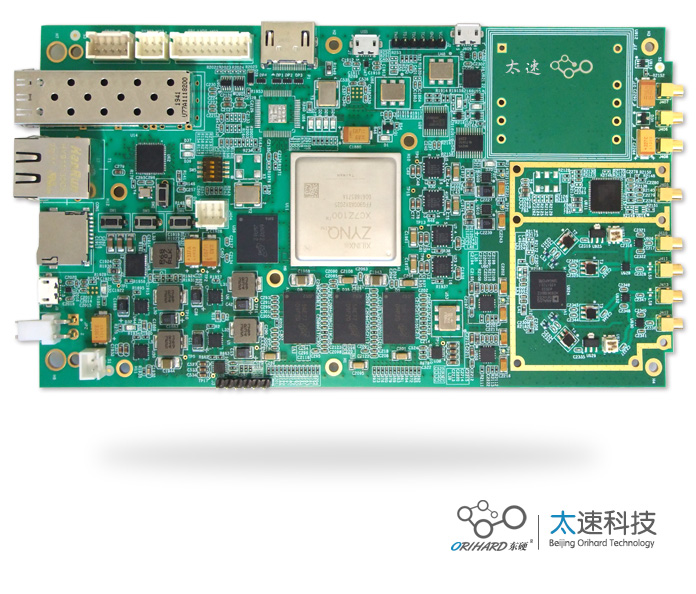

一、板卡概述 基于XC7Z100+AD9361的双收双发无线电射频板卡是基于Xilinx ZYNQ FPGA和ADI的无线收发芯片AD9361开发的专用功能板卡,用于4G小基站,无线图传,数据收发等领域。

二、板卡原理及功能 板卡使用XC7Z100 作为主处理器,包含Dual ARM Cortex-A9核处理器的嵌入式处理,PS端32bit 1GB容量DDR3存储,1路RS232接口,1路USB接口1路10-100-1000网络接口,PS端QSPI flash存储,PS端SD卡,Emmc存储;PL端64bit 2GB容量DDR3存储,PL端扩展HDMI 输出实现视频显示应用,PL端扩展9路I/O,4个LED指示灯。

PL端外扩AD9361芯片,AD9361是一款高集成度射频(RF)、捷变收发器,提供双通道发射器和接收器、集成式频率合成器以及数字信号处理功能。这款IC具备多样化的高性能和低功耗组合,FMC子卡为2路输入,2路输出的射频收发卡,配合FPGA工作满足3G、4G宏蜂窝时分双工(TDD)和频分双工(FDD)基站应用要求。 板卡数字接口:

| | No. | Items | Specifications | Remark | | Tx | 1 | Frequency | 70~6000MHz | | | 2 | Bandwidth | Up to 56 MHz | real-time bandwidth, tunable | | 3 | Transmission | >5dBm | CW | | 4 | EVM | <1.5% | Typical:5dBm @20MHz bandwidth | | 5 | Gain Control Range | >80dB | | | 6 | Gain Step | 0.25 dB | | | 7 | ACLR | < -45dBc | @ 0dBm LTE output | | 8 | Spurious | TBD | | | 9 | SSB Suppression | 35dBc | | | 10 | LO Suppression | 50dBc | | | 11 | DAC Sample Rate (max) | 61.44MS/s | | | 12 | DAC Resolution | 12bits | | | | | Rx | 1 | Frequency | 70~6000MHz | | | 2 | Bandwidth | Up to 56 MHz | real-time bandwidth, tunable | | 3 | Sensitivity: | -90dBm@20MHz | Noise Figure < 8dB | | 4 | EVM | <1.5% | @ -30dBm input | | 5 | Gain Control Range | >60dB | | | 6 | Gain Step | 1dB | | | 7 | Blocking | TBD | | | 8 | Noise Figure | <8db | Maximum RX gain | | 9 | IIP3 (@ typ NF) | -25dBm | | | 10 | ADC Sample Rate (max) | 61.44MS/s | | | 11 | ADC Resolution | 12bits | | | 12 | ADC Wideband SFDR | 78dBc | | | | 1 | Voltage | 3.3V | | | 2 | ON/OFF TIME | <6us | For TDD model | | 3 | Duplexing Model | TDD or FDD | | | | 4 | W/ GPSDO Reference | 0.01ppb | |

三、软件系统

参考ADI开发板官网全套软件,固件程序芯片XC7Z100。

ARM linux 软件和客户端软件一模一样。

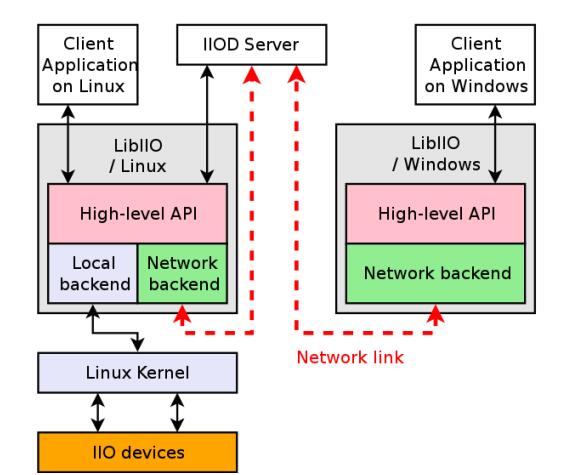

客户开发主要考虑LibIIO API应用,客户端应用,或者固件程序里面修改PL端的逻辑代码,插入个性化算法应用。其中LibIIO API功能架构如下图图6所示。

|