一种用于常开型智能视觉感算系统的极速高精度模拟减法器

源自:电子与信息学报

作者:刘博, 王想军, 麦麦提·那扎买提, 郑辞晏, 向菲, 魏琦, 杨兴华, 乔飞

注:若出现显示不完全的情况,可 V 搜索“人工智能技术与咨询”查看完整文章

人工智能、大数据、多模态大模型、计算机视觉、自然语言处理、数字孪生、深度强化学习······ 课程也可加V“人工智能技术与咨询”报名参加学习

摘 要

常开型智能视觉感算系统对图像边缘特征提取的精度和实时性要求更高,其硬件能耗也随之暴增。采用模拟减法器代替传统数字处理在模拟域同步实现感知和边缘特征提取,可有效降低感存算一体系统的整体能耗,但与此同时,突破10–7 s数量级的长计算时间也成为了模拟减法器设计的瓶颈。该文提出一种新型的模拟减法运算电路结构,由模拟域的信号采样和减法运算两个功能电路组成。信号采样电路进一步由经改进的自举采样开关和采样电容组成;减法运算则由所提出的一种新型开关电容式模拟减法电路执行,可在2次采样时间内实现3次减法运算的高速并行处理。基于TSMC 180 nm/1.8 V CMOS工艺,完成整体模拟减法运算电路的设计。仿真实验结果表明,该减法器能够实现在模拟域中信号采样与计算的同步并行处理,一次并行处理的周期仅为20 ns,具备高速计算能力;减法器的计算取值范围宽至–900~900 mV,相对误差小于1.65%,最低仅为0.1%左右,处理精度高;电路能耗为25~27.8 pJ,处于中等可接受水平。综上,所提模拟减法器具备良好的速度、精度和能耗的性能平衡,可有效适用于高性能常开型智能视觉感知系统。

关键词

模拟减法器 / 自举采样开关 / 电荷守恒定律 / 极速 / 高精度

1. 引言

日益增长的应用需求极大推动了物联网(Internet of Things, IoT)和人工智能(Artificial Intelligence, AI)融合科技AI+IoT(AIoT)的发展[1]。人类通过视觉获取的信息约占触、嗅、味、听、视全部五觉感知的83%[2],因此,图像作为人类感知世界的视觉对象,是获取、传递和表达信息的重要手段[3],视觉感知计算系统自然成为AIoT领域的热门研究方向之一。高性能视觉感算系统需要实时地感知物理世界以快速精准地获取信息,这就要求传感器硬件系统是高速常开型。然而,电池等供电设备的体积和储能效率大大限制了常开型智能视觉感算系统的持续工作时间。低功耗CMOS图像传感器(CMOS Image Sensor, CIS)[4,5]与其节能存算系统[6–9]是热门的研究领域,但是两部分间缺乏协同优化导致无法实现最佳的系统能耗,因为大量的能量消耗在大数据量吞吐和模数转换器(Analog-to-Digital Converter, ADC)上。为进一步降低常开型感算系统的能耗,有研究者提出在模拟域中直接进行原始图像信息的感知和存算预处理,通过节约数据交互和ADC带来的额外能耗以达到最佳的整机系统能耗水平[10]。

差分运算是图像信息处理中最常见的运算之一,模拟减法器,是在模拟域中通过差分运算处理以实现图像边缘特征提取的一种典型算子电路[11–14]。文献[11,12]提出了一种由运放构建的开关电容式模拟减法器,减算过程遵循电荷守恒定律,通过电容的开关切换实现两像素电压值相减并求解平均值,以ms级计算时间完成相对低速率的图像边缘信息提取。文献[13]提出直接在模拟域使用电阻模拟减法器实现特定图像如边缘、背景细节、前景纹理等特征的预判别,但由于减法器采用4个运放构成,功耗高、面积大。文献[14]提出一种基于基尔霍夫电流定律的电流模减法器,每一帧图像的减法计算时间仍然是ms级别,适用于低速像素差分处理。文献[15–20]是近5年应用于图像边缘特征提取的典型模拟减法器。文献[15]使用6T1C电路和曝光补偿技术实现面向帧差分的单像素减法运算,同样基于电荷守恒定律,但得到单像素结果值需经6个信号处理步骤,且实现两像素值相减需额外设计减法器,电路结构复杂。文献[16,17]创新采用两个列比较器,通过比较每像素输出的信号值与比较器阈值以判别运动物体,但比较器输出的二值仅能标识有无物体运动,无法得到更多像素边缘信息,功能具有局限性。文献[18]使用可编程电容组、减法器单元、模拟存储器和相关双采样模块组成的运算电路实现高动态范围的像素值计算,差分运算均遵循电荷守恒定律,但电路构成较为复杂,伴随较大功耗和电路尺寸。文献[19]提出一种采用忆阻器实现的新型像素值计算电路,将忆阻器用于差分运算或纯背景信息提取的模式控制开关。该电路缺点为伴随两运放并行工作的功耗增加,以及基于专用特殊材料和工艺的忆阻器成本高企。最近的文献[20]采用一种开关电容式模拟减法器实现了两像素值的差分运算和边缘识别,但一次计算总耗时达2 μs,计算速度仍有大幅提升的空间。

针对常开型智能视觉感知系统中核心的边缘特征计算处理对实时性即速度的追求,为突破图像信息处理中10–7 s数量级的像素值采样-计算的时间瓶颈,本文提出一种在处理速度、精度和能耗3方面均具有明显性能优势的新型模拟减法运算电路。基于TSMC 180 nm/1.8 V CMOS工艺完成整体减法器电路设计和性能验证,仿真测试结果显示在维持高精度和良好能耗的同时,可实现两像素值的差分运算(采样-计算)时间小于100 ns,有效实现图像边缘特征信息的高速实时处理。

2. 基于减法运算的图像边缘特征信息提取

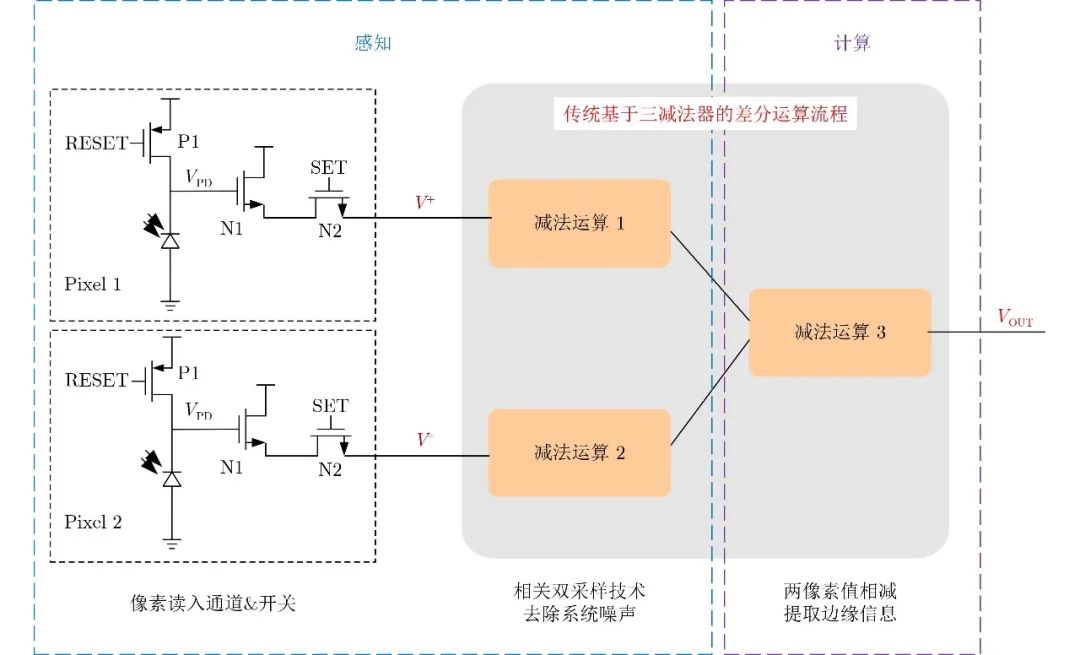

图1是智能视觉感知系统中CIS信号接收处理流程图,总体可分为感知和计算两部分。为方便描述,将“感知”部分进一步分解为像素读取和减法运算读出电路两部分。原始像素被光电转换为电信号后,采用相关双采样技术抑制系统噪声,以提升后续边缘信号的差分处理精度。“计算”部分将前端感知读入的两像素值进行减法运算,提取得到图像中的边缘特征信息。由图可知,整体系统中共需要3次减法运算,分别对应CIS信号读取过程中的降噪和差分信息提取的作用。

图 1 视觉感知系统最前端 CIS信号接收过程抽象图

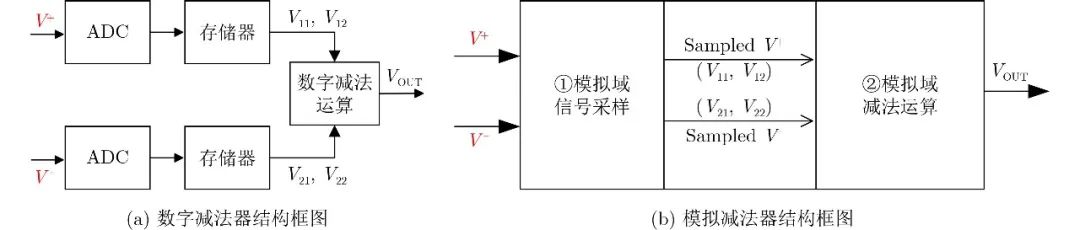

图2(a)展示了传统数字减法器实现图像像素差分运算的实现方式。使用ADC将模拟域的阵列图像信息量化离散为二值的数字信号保存至存储器,之后同步读取数据在处理器进行减法运算并输出结果。该数字化传统架构中,两个高性能ADC将消耗运算流程中的大部分功耗。同时,模拟域的每个采样电压信号AD转换后将对应多比特数据流,这需要大量的动态随机存储器进行数据的存储和读写交互,这也将引起额外的功耗和信号延迟。因此,考虑到硬件复杂度、尺寸、功耗和运算处理速度,传统基于数字减法器的像素差分提取策略已不再很好的适配高能效常开型智能视觉感知系统的应用。

图 2 两种常用减法运算电路架构

与之相对,如图2(b)所示,模拟减法器由信号采样和减法运算两部分组成,在感知前端的模拟域即可对原始图像信息进行粗分类采样,通过预筛选可减少冗余信息进入下一级处理单元,有效达到降低整体系统能耗、提升速度、节省硬件开销的目的。

3. 模拟域减法运算电路

3.1 常规电阻式模拟减法器

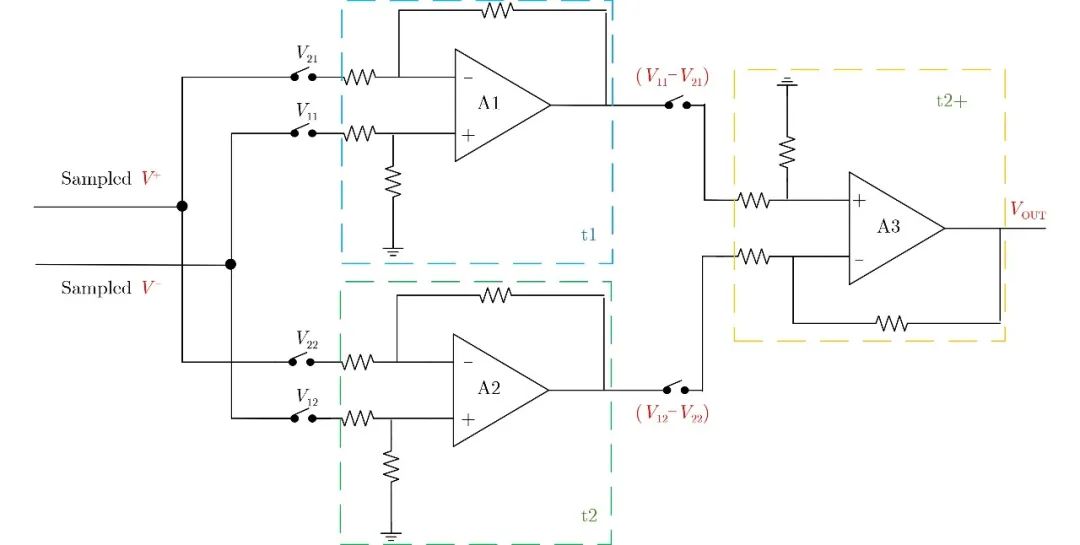

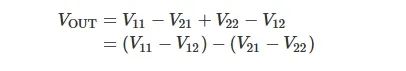

为适配图1中常开型智能视觉感知系统的高速高精度像素特征提取的应用需求,一般考虑使用图3所示的电阻式模拟减法运算电路。该减法器将来自正负两个读入通道、先后经过两次采样、每次一组的4个电压值分别在t1和t2时刻完成2次减法运算并输出差值到减法器A3,此时,在t2时刻即可完成总减法运算,最终的差值即为想要提取的两图像像素边缘特征信息。需要注意的是,t1和t2也分别是对像素电压值的采样时刻,采样瞬间即在减法器中完成一次减法运算。

图 3 2次采样完成3次减法运算的电阻式模拟减法器

由图3和图4可知,先由模拟域信号采样电路对像素读入的V+, V–信号进行采样,如在t1时刻分别在两通道采样,即V+=V11, V–=V21,采样完成瞬间即在减法器A1中完成减法运算并输出差值(V11–V21)。与之同理,t2时刻也进行一次采样,并在减法器A2输出该时刻的减算差值(V12–V22)。最终,需要注意的是,如不考虑减法器本身延迟的理想情况下,在t2时刻求取(V12–V22)差值的瞬间即可在减法器A3完成第3次减法运算,得到最终的减法器输出VOUT=(V11–V21)–(V12–V22),即为所求的两像素差值。尽管该电阻式模拟减法器可实现在两个采样周期内高速完成3次减法运算,但该方案需用到3个运算放大器,整体功耗、面积以及大量电阻引起的精度恶化和热能耗等问题不容忽视。为此,本文提出一种新型的高速高精度开关电容式模拟减法运算电路,将运放的使用缩减到仅1个,同时只需要4个无源电容取代12个电阻,降低功耗和面积的同时也避免了大量无源器件引起的电路误差,有效提升了整体减法运算系统的处理精度。

图 4 电阻式模拟减法器的运算时序图

3.2 本文提出的开关电容式模拟减法器

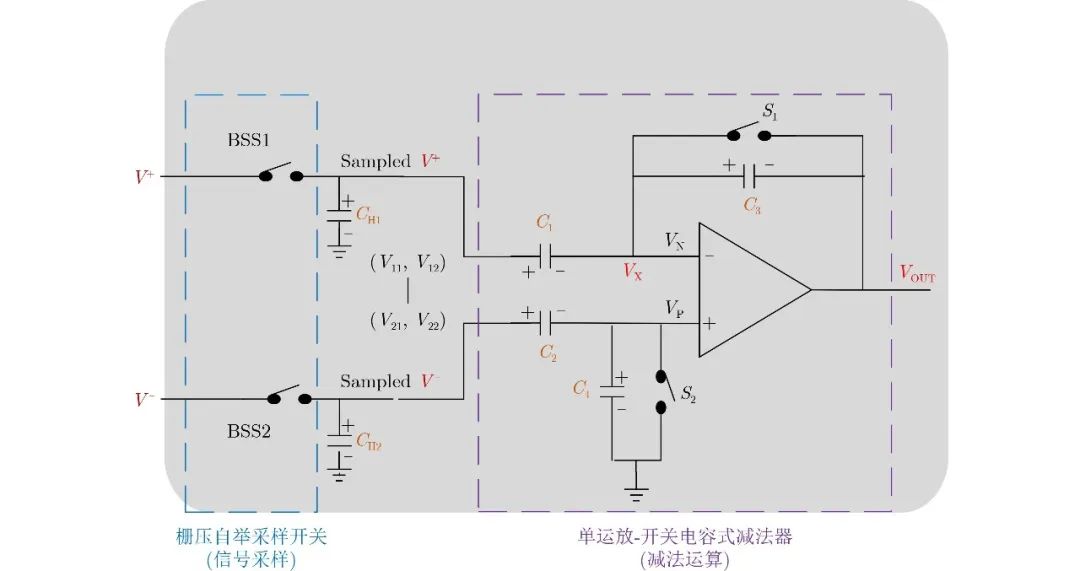

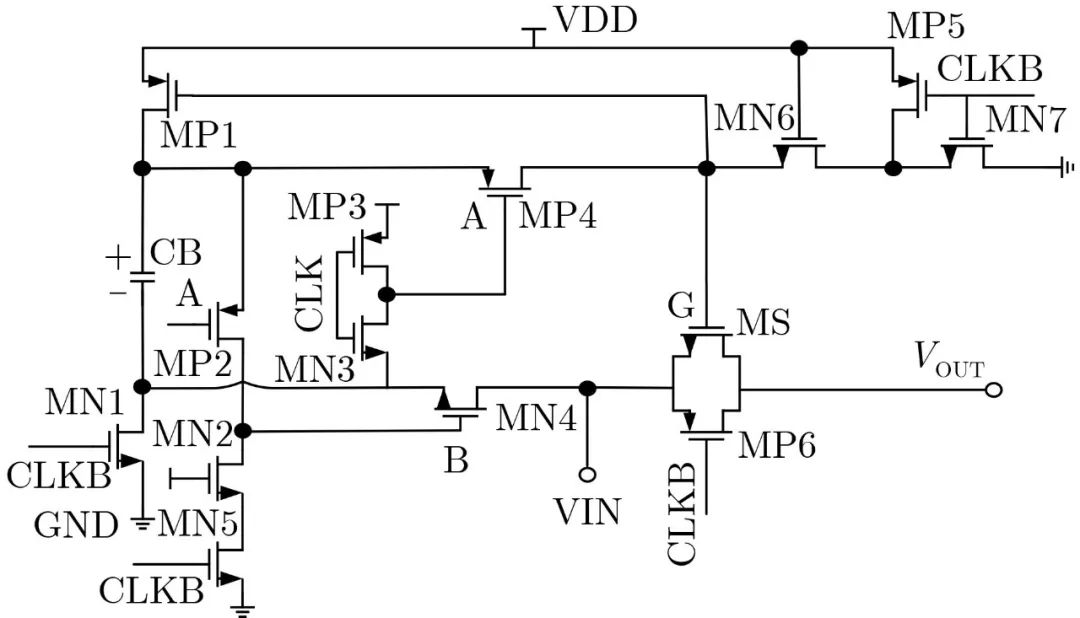

图5为本文所提模拟减法器电路的完整结构图,包含模拟域信号采样和减法运算两部分。整体电路由一对高精度自举采样开关(Booststrapped Sampling Switch, BSS)、采样保持电容CH1–CH2以及核心的开关电容式模拟减法运算电路3部分构成。这3部分又分别对应3个重要的电路功能,采样、保持、运算。自举采样开关首先对读入的两路像素值对应的电信号V ±采样,并在该时刻将其临时存储至采样电容CH1–CH2;下一时刻将采样后的信号Sampled V±输入下一级模拟减法运算电路进行减法运算,并输出最终的计算差值,即两像素值之差。

图 5 结合采样保持功能的基于单运放实现3次减法运算的开关电容式模拟减法运算电路

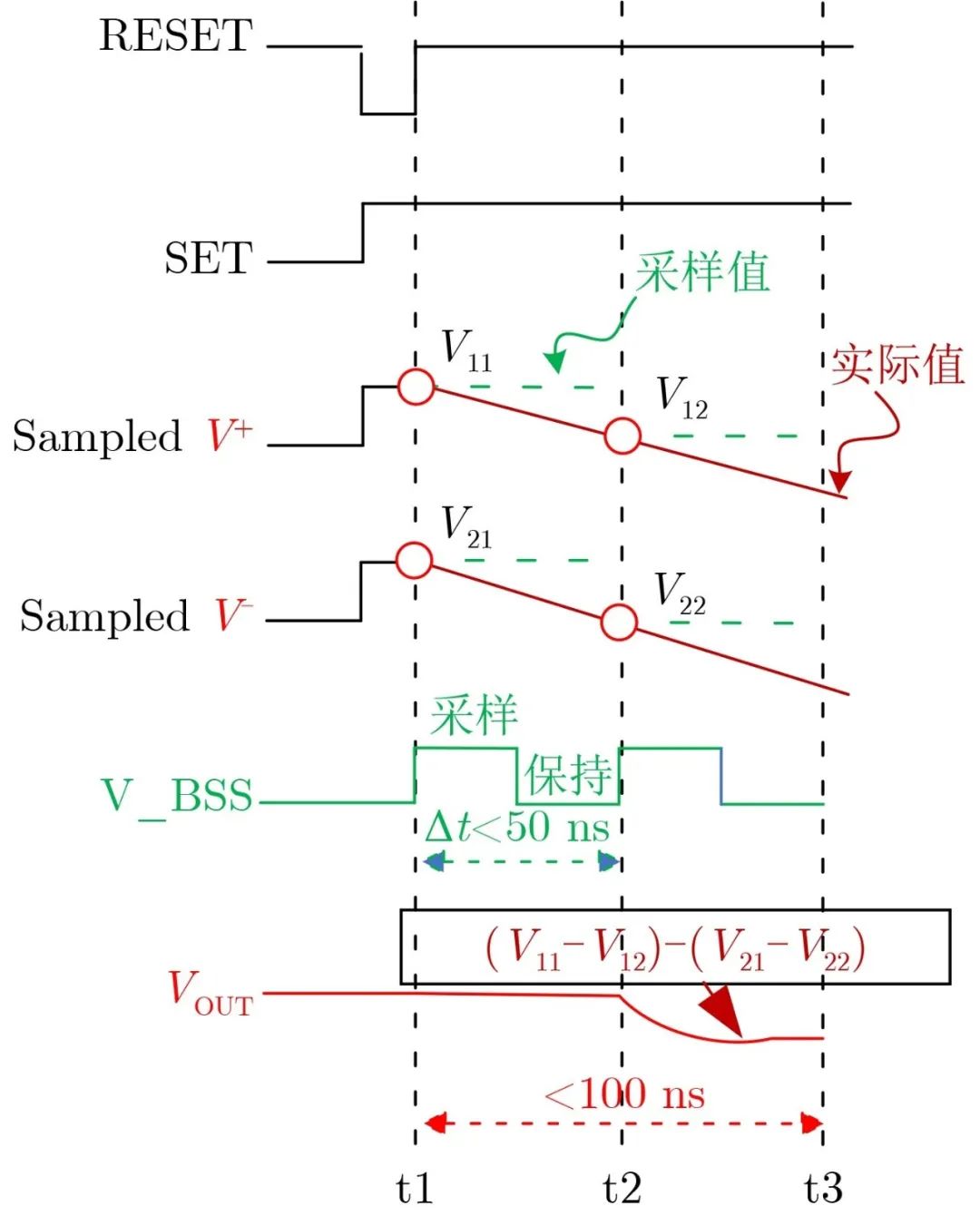

根据图1和图5对整体图像读入感知系统及后续模拟减法运算电路的描述,结合图6的时序示意图可知:在初始感知模式下,两路像素读入通道的开关P1和N2均导通(即RESET=0, SET=1),此刻VPD=VDD并通过源极跟随器N1输出至采样开关BSS。首先,经t1时刻采样后,电容式减法器前端的两个采样电容C1, C2将记录并一直保持Sampled V ±(采样信号)均为高电平,即在t1时刻,有V11=V21=VDD;之后随着画像移动,用于像素读入的光电二极管产生与外部光强成正比的光电流导致VPD值减小,稳定后在t2时刻被分别采样、传输至采样电容C1, C2。与此同时,开关电容式减法器的内部对t1时刻采样并保持在C1, C2的电荷进行再分配,该过程可看做在t2时刻对4个采样电压分别进行了(V11–V12), (V21–V22)的两次减法运算。随着t2时刻的采样(也对应采样电容中的电荷再分配过程)结束,最后的减法器输出VOUT即可得到(V11–V12)–(V21–V22),即以3次减法运算(2次减法为相关双采样的去噪功能、1次减法为两像素电压的差值计算)完成对目标图像的边缘特征信息的提取。需要注意的是,图6是仅展示3次减法运算的示意图,实际自举采样开关只需10 ns的持续导通即可完成一次完整采样,即本设计可有效达成两次采样间隔Δt<50 ns的目标。

图 6 减法器3次减法运算功能示意图

3.3 基于电荷再分配原理的减算功能实现

图5中“减法运算”部分即由本文所提电容开关式模拟减法器实现,由1个轨到轨运算放大器、4个等容值电容和2个控制开关构成。值得注意的是,图3的电阻式减法器在t1, t2先后两个采样时刻、按序读入4个像素电压值、通过3次减法运算直接实现像素的差值求解VOUT=(V11–V21)–(V12–V22)。与其运算顺序不同,图5的电容开关式减法器则是基于电荷守恒原则,通过切换自举采样和电容开关,完成在t1,t2两个采样时刻对电荷的再分配,最终实现了与图3算序不同、但结果相同的减法运算,即VOUT=(V11–V12)–(V21–V22)。

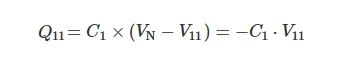

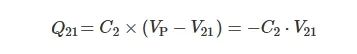

基于电荷再分配的详细减算原理如下:初始状态下,开关S1和S2均闭合,电容C3和C4被短路,采样电容C1和C2的下极板复位到接地电位(此时假设理想运放的VN=VP=0)。首先,在t1时刻开始采样。自举开关BSS1和BSS2闭合导通,采样进来的Sampled V ±电压持续对C1, C2进行充电。一段时间稳定后,采样电容C1, C2上极板的电压值分别升至V11, V21,此刻的储存电荷量为Q11, Q21,表达式记为

(1)

(2)

t1采样结束直至2次采样t2时刻到来之前,整体减法器进入保持模式,两自举开关BSS断开,采样信号V11和V12以电荷形式存储在电容C1和C2之中,减法器输出VOUT一直为0。

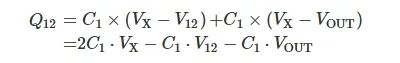

接下来,在t2时刻进行第2次采样。S1, S2断开,则电容C3, C4分别与C1, C2开始电容耦合。与此同时,自举开关BSS1和BSS2再次闭合,完成读入像素电压值的2次采样,此刻采样电容C1, C2上极板的电压值(由t1时刻的V11, V21)变为V12, V22。另一边,根据理想运放的输入虚短原则,经过一段时间的电容耦合后,C1, C2下极板的电压值相等,即VN=VP=VX;由于理想运放输入端无电荷损失,则2次采样结束时刻,电容C1, C2上的存储电荷量Q12, Q22的表达式记为式(3)、式(4)

(3)

(4)

根据电荷守恒定律,可知Q11=Q12, Q21=Q22,将式(1)–式(4)整理即可得到式(5)、式(6)

![]()

(5)

![]()

(6)

进一步,将式(5)与式(6)相减即可整理推导出式(7)的3次减法运算的综合表达式,即本设计要实现的在2次采样时刻、对4个读入电压值、完成3次减法运算的电路功能

(7)

4. 自举采样开关电路

如图5所示,本文提出并设计了一组高线性度的栅压自举采样开关(BSS1和BSS2)实现对读入的像素电信号的采样和保持,并进一步配合后续的减法运算实现高速、高精度运行。

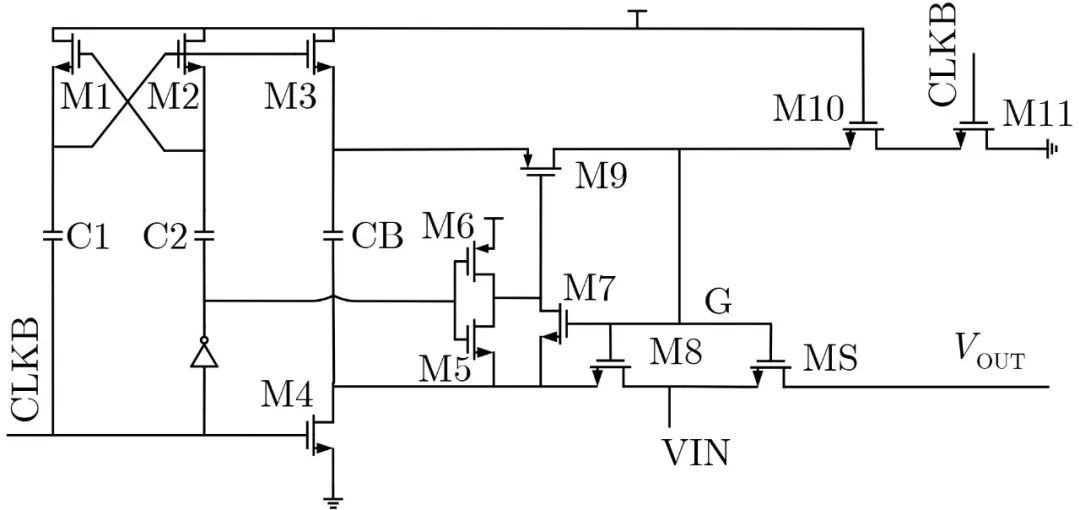

将两次采样间隔时间10 ns(Δt<50 ns)作为自举采样开关的设计约束,可算出开关的采样速率为100 MS/s,则输入信号的频率最高可达25 MHz。因此,由于器件本身的非线性及高频采样引起的谐波失真等原因,MOS单管或N/P互补CMOS采样开关无法满足本研究高速、高精度采样的要求。为解决这一问题,如图7所示,Abo和Gray提出一种常用的高精度自举采样开关[21]。该自举结构能使采样管MS的VGS恒定保持在接近VDD的水平,可有效降低导通电阻以提升输出线性度。但与此同时,该自举采样开关在高速采样时,采样管开启/关闭时间将受到限制,无法满足设计约束100 MS/s高速采样率的要求。为此,本文提出一种高速、高精度的自举采样开关电路,结构如图8所示。相较于常规采样开关,所提出的自举采样开关通过降低导通电阻和减小关键路径节点的寄生电容来加速开关开启/关闭过程,最终实现了采样速率和高频信号采样线性度的提升。

图 7 常规的栅压自举采样开关

图 8 所提自举采样开关

5. 仿真分析和性能讨论

本研究采用TSMC 180 nm/1.8 V 标准CMOS工艺,在Cadence Virtuoso和Spectre平台完成整体减法运算电路的设计和性能仿真分析。

5.1 栅压自举采样开关

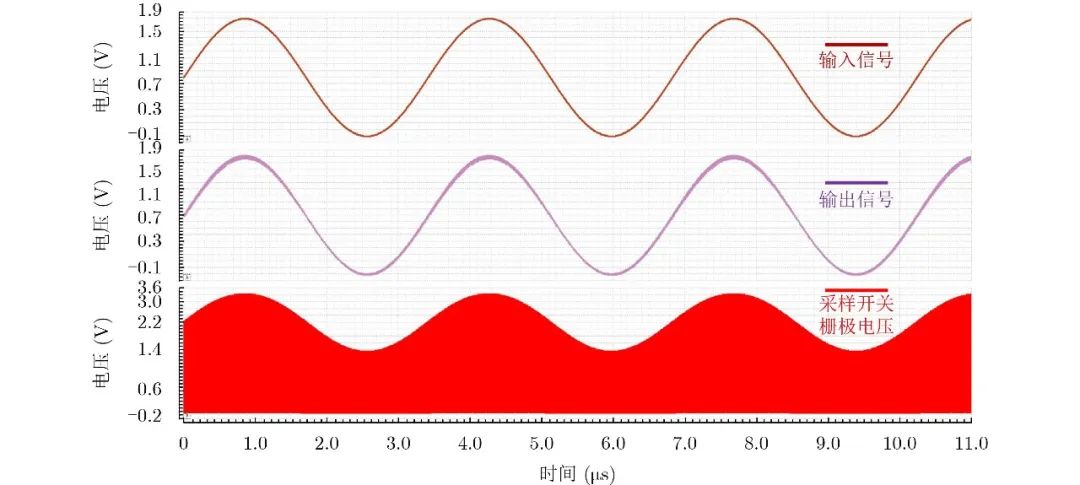

首先仿真验证本研究提出的自举采样开关(图8)的性能。输入频率为293 kHz、峰峰值为1.8 V的理想正弦波,输出端接2.5 pF的负载电容,以100 MS/s的采样率对输入信号进行采样。图9为瞬态仿真波形图,输出信号能够精确地跟随输入信号变化,线性度良好。同时,可观测采样开关(采样管MS)的栅压在1.75~3.5 V范围波动,处于正确的栅压自举工作范围,证明所提出的自举采样开关设计良好。

图 9 自举采样开关的瞬态仿真结果

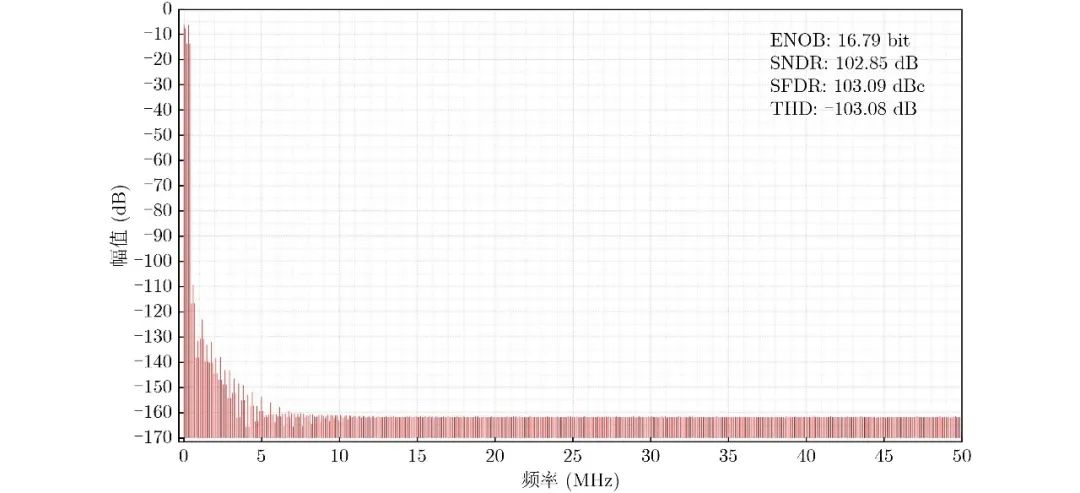

为进一步验证采样开关的动态性能是否符合高频应用要求,选择1 024个采样点,对输出信号进行离散傅里叶变换(Discrete Fourier Transform, DFT)。采样频谱结果及相应的动态特性参数如图10所示。从DFT频谱结果可以看出,所设计的自举采样开关的有效位数(Effective Number Of Bits, ENOB)为16.79 bit,信噪失真比(Signal to Noise and Distortion Ratio, SNDR)为102.85 dB,无杂散动态范围(Spurious Free Dynamic Range, SFDR)为103.09 dBc,总谐波失真(Total Harmonic Distortion, THD)为–103.08 dB,各项动态性能指标均满足视觉感知系统对高速、高分辨率像素电信号采样的应用需求。

图 10 自举采样开关基于DFT的频谱及动态性能

最后,表1展示了2020年–2023年近3年,采用同种工艺尺寸实现的自举采样开关设计案例的指标对比结果。可以看到,在本文提出自举采样开关以最高的100 MS/s采样速率条件下,仍然实现了 ENOB,SNDR,SFDR和THD全部4项动态性能指标的胜出,证明所提采样开关具有明显优势。

表 1 本文设计与他参考文献各指标对比

5.2 开关电容式模拟减法器

根据4.1节所述,根据采样时间10 ns,可设定整体减法运算电路从采样到最终差值输出(2次采样时间)20 ns为极限约束条件,针对图5中的“减法运算”部分,即开关电容式模拟减法器进行仿真验证。将图5中的两路Sampled V +, Sampled V – 输入信号设为周期20 ns的理想方波,电压幅度设为1.8 V电源电压下的任意组合,因此可知减法器输出的差值计算范围可从–900~900 mV。使用不同的电平信号对进行减法运算的仿真,将理想的减法计算值(Calculated value,不考虑任何误差的理想减法计算)、和减法器电路的差值仿真结果(Simulated value,包含电路误差)进行对比,用以确认所设计的减法器功能正常并分析其计算精度。

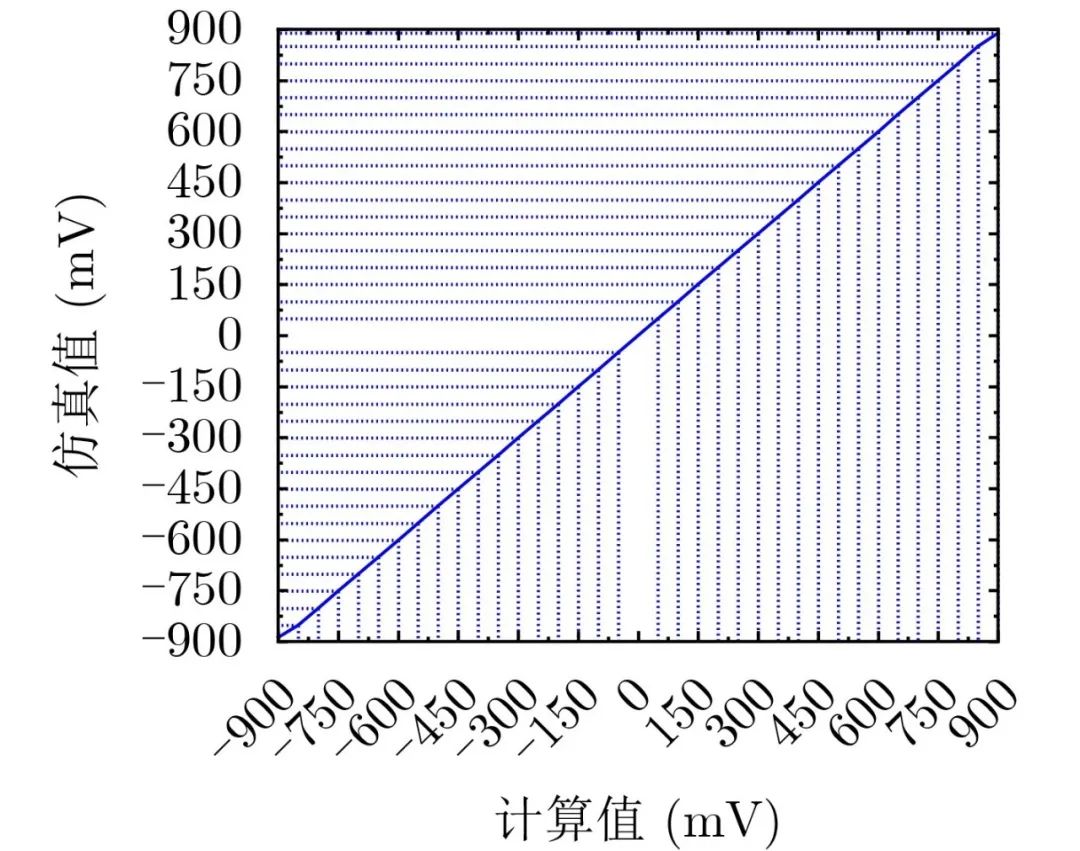

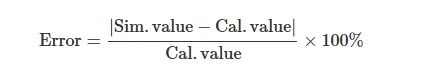

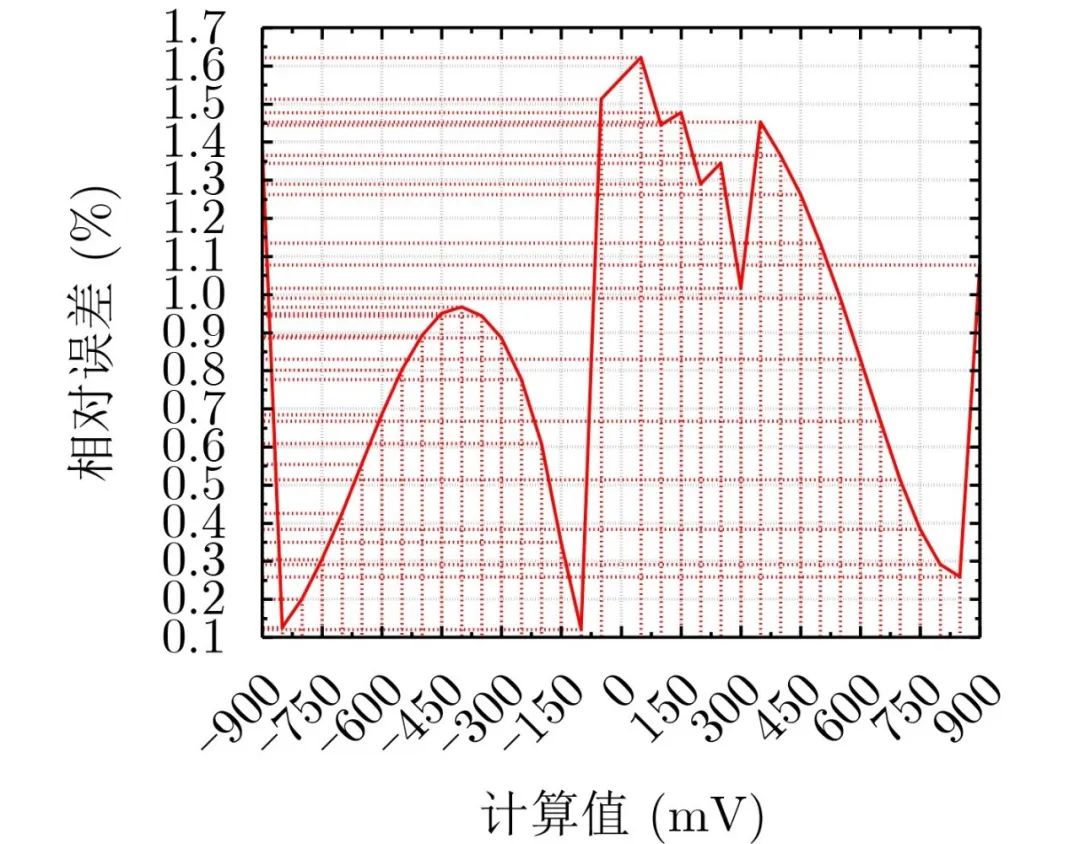

图11展示了基于36组减数-被减数输入电平对的理想计算值与减法器仿真输出值的对比曲线图。可看到图中采样曲线的斜率近似为1,说明减法电路的仿真值与计算值近似相等,所设计的开关电容式减法器的减法运算功能良好。

图 11 理想的减法计算差值与减法电路的仿真输出结果对比

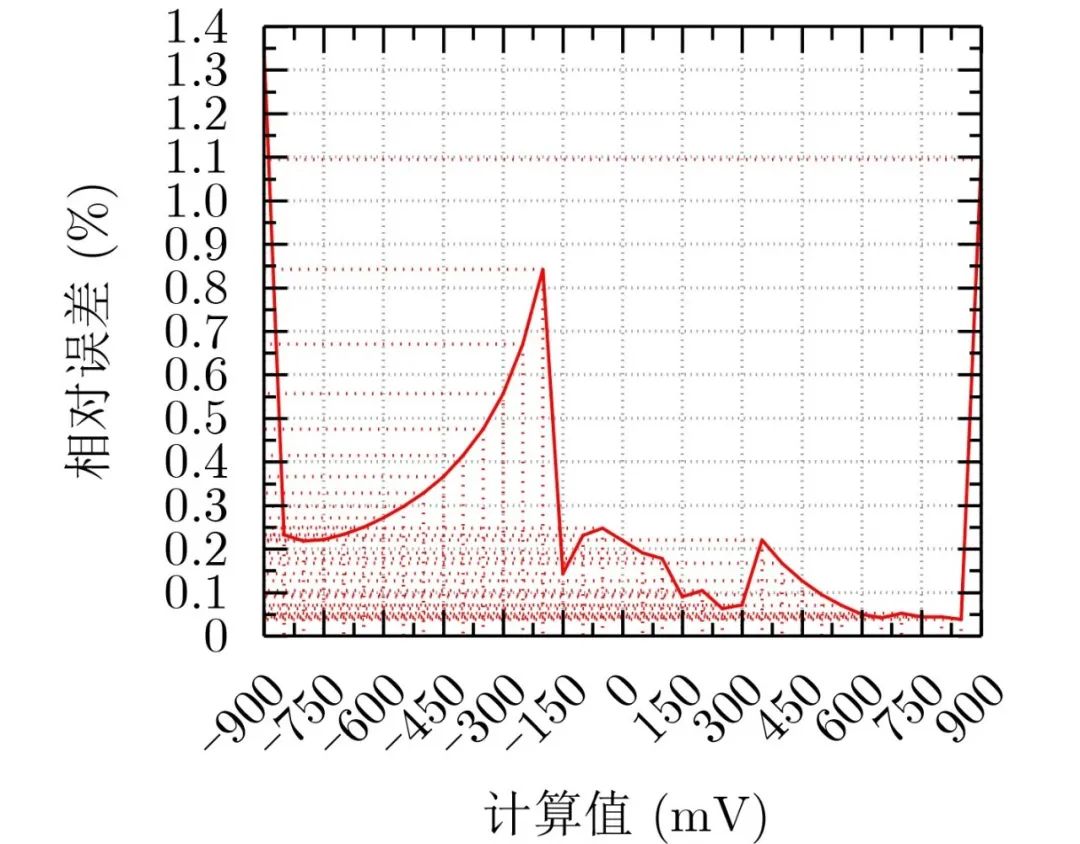

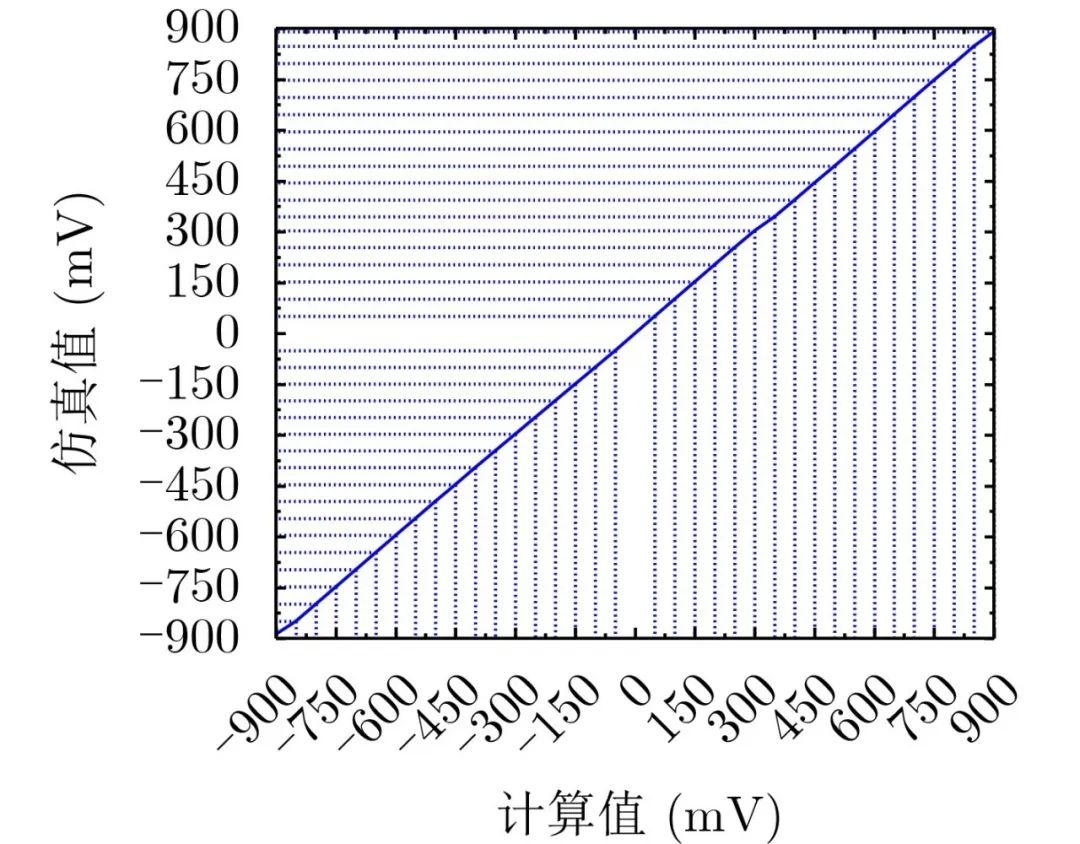

此外,针对36组输入中的每一组都进行了对比理想值的误差计算,并以此分析减法器电路的整体运算精度。式(8)为使用的误差计算公式,图12是相应的误差采样曲线图

图 12 不同的减法器差值输出对应的误差采样曲线

(8)

由此可知,所设计开关电容式减法器最大的输出误差仅为1.35%,且除了最大值900 mV、最小值–900 mV和–200 mV的3点之外,其余91.67%的计算值误差均在0.3%以下。该结果显示,本文设计的开关电容式减法器具有优越的运算精度,在实际应用中,源自电路的计算误差几乎可忽略不计。

5.3 整体模拟域减法运算电路

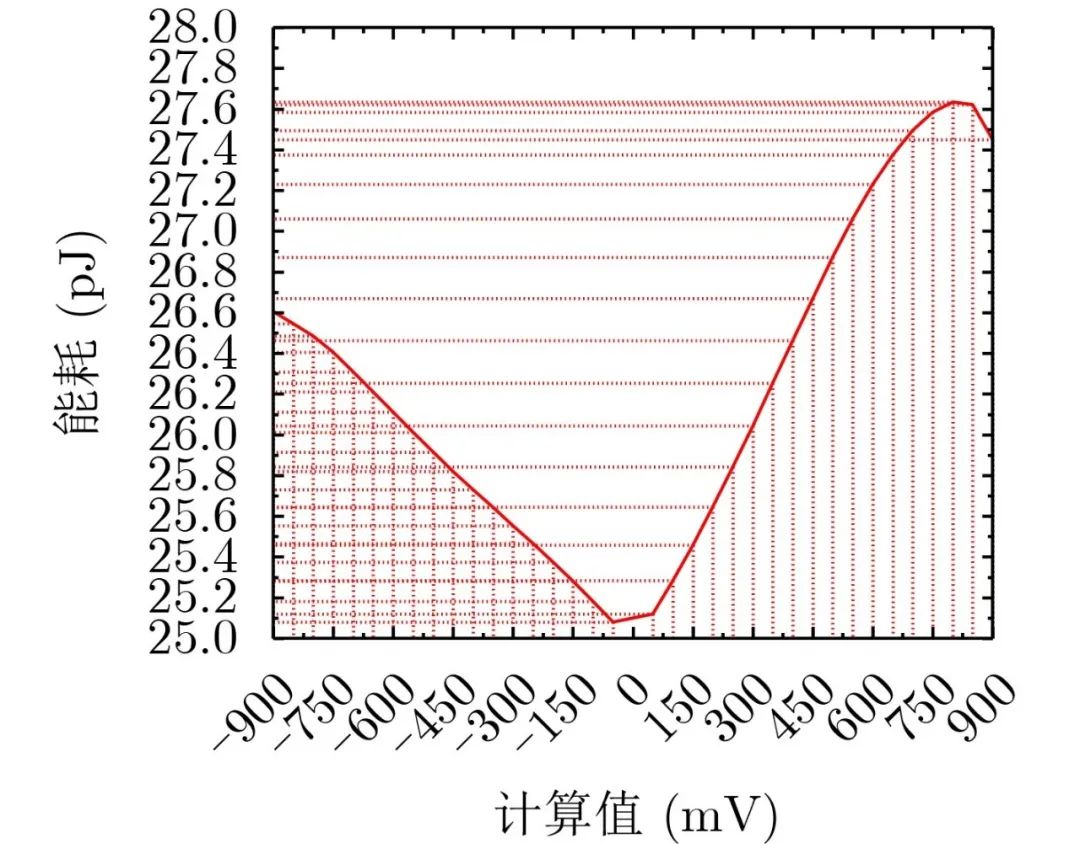

与前节的开关电容式减法器的分析验证类似,结合栅压自举采样开关后的整体模拟域减法运算电路的仿真结果如下所示。图13同样展示了斜率近似为1的曲线,说明整体减法运算电路的仿真值与理想计算值近似相等,显示减算功能良好。图14仍是误差曲线图,可看到,减法运算的最大误差小于1.65%,最小误差仅为0.1%,可证明整体模拟域减法运算电路仍然具有较高的计算精度。此外,图15是计算值与电路能耗的采样曲线图,由此可知,所设计的整体减法运算电路完成两次采样、3次减法运算的能耗在25 ~27.8 pJ之间,显示出了良好的低能耗特性。

图 13 整体模拟域减法运算电路的计算值与仿真值的对比

图 14 不同的减法器差值输出对应的误差采样曲线

图 15 模拟减法器计算值与能耗的曲线

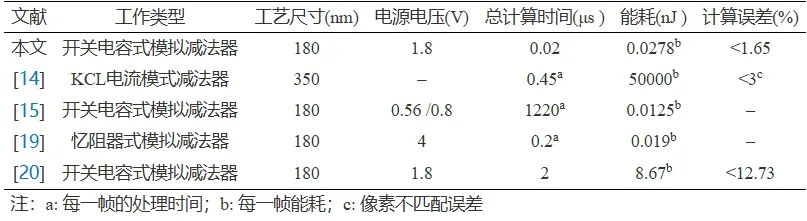

表2列举了多篇应用于边缘特征提取或运动检测技术领域的有关模拟减法器的设计案例文献,本文针对4种不同电路架构实现的模拟减法器,在总计算时间、能耗、误差3个性能维度进行了指标对比。观察表2可知,相较于几个参考设计案例,本文提出的完整(包含同步信号采样操作)模拟减法运算电路,虽在能耗方面不具明显优势,但总计算时间和计算误差排序均位列第一,显示出在运算速度和高精度计算能力方面占据绝对优势,符合设计预期并可有效地应用于高速高精度智能视觉感知系统前端对图像特征信息的识别与提取。

表 2 本文提出的模拟减法运算电路与其他设计案例的对比

6. 结束语

采用TSMC 180 nm/1.8 V 标准CMOS工艺设计实现了一种应用于常开型智能视觉感知系统的高速、高精度模拟减法运算电路。所提减法器直接在模拟域对原始图像像素电信号进行特征信息的差分提取,实现在20 ns极短周期内就可完成2次信号采样和3次减法运算,具有高速计算能力。在Cadence平台完成电路设计和性能仿真,结果显示,在1.8 V电源电压和27℃的标准环境温度下,所设计的模拟域减法运算电路具有–900~900 mV的宽计算值范围;减法器仿真输出结果与理想计算值基本一致,整体相对误差小于1.65%,最小误差仅为0.1%,具有完成高精度差值计算能力;完成1次完整的采样-计算并行处理的所需能耗在25~27.8 pJ之间,耗电性能适中。经与同类设计案例对比显示,本文提出的模拟域减法运算电路在计算速度和精度上具备显著优势,可有效服务于目标对象的高速常开型智能视觉感知系统对图像边缘特征提取的应用需求。

声明:公众号转载的文章及图片出于非商业性的教育和科研目的供大家参考和探讨,并不意味着支持其观点或证实其内容的真实性。版权归原作者所有,如转载稿涉及版权等问题,请立即联系我们删除。

注:若出现显示不完全的情况,可 V 搜索“人工智能技术与咨询”查看完整文章

人工智能、大数据、多模态大模型、计算机视觉、自然语言处理、数字孪生、深度强化学习······ 课程也可加V“人工智能技术与咨询”报名参加学习