项目二:m序列的设计与实现(FPGA)

本文以Altera公司生产的Cyclone IV系列的EP4CE15F17C8为主芯片的CRD500开发板作为项目的硬件实现平台,并以Quarter 18.1和ModelSim为开发工具和仿真工具。

实验目的:产生m序列(长度为2^(15)-1,码元速率为 1 Mb/s)

目录

一、项目原理

二、实现步骤

(1)新建文件夹m_sequence

(2)创建工程

(3)编译

(4)仿真测试

基于Quartus 自身工具模块的仿真

三、板载测试准备工作

1、引脚配置

2、下载.sof格式文件

3、转为为.jic文件下载到FPGA

四、板载测试

一、项目原理

伪随机噪声既具有类似于随机噪声的一些统计特性,又便于重复产生与处理,它具有随机噪声的优点又避免了随机噪声不可复制的缺点,得到了广泛的应用。目前,伪随机噪声由数字电路产生的周期序列得到,这种序列称为伪随机序列。

伪随机序列的应用包括误码测试、时延测量、扩频通信、保密通信、卫星通信、北斗定位系统、数字信号源设计等,伪随机序列通常用反馈移位寄存器产生,分为线性反馈移位寄存器和非线性反馈移位寄存器两类。由线性反馈移位寄存器产生的周期最长的二进制数字序列称为最大长度线性反馈移位寄存器序列,简称为m序列。

m序列具有以下特性:

(1)均衡性。

在m序列的一个周期中,0与1的数目基本相等,准确讲1的个数比0的个数多 1。

(2)游程特性。

一个序列中取值相同的、连在一起的元素称为一个“游程”。游程中元素的个数称为游程长度。m序列中,长度为1的游程占游程总数的12,长度为2的游程占游程总数的 1/4,…,长度为k的游程占游程总数的2^(-k),其中1≤k≤n-1。

(3)移位相加特性。

一个m序列 m1,与其经任意次延时移位产生的另一个不同序列m2模二加,得到的序列仍然是这个m序列的某个移位序列。

(4)相关特性。

(5)随机特性。

m序列可通过本原多项式产生。

本项目要求产生长度为2^(15)-1,码元速率为 1 Mb/s 的m序列,由上表图知其本原多项式为![]()

得其实现原理图:

二、实现步骤

(1)新建文件夹m_sequence

路径:D:\Verilog\txhFPGA\m_sequence

注:文件夹名不能包含中文

(2)创建工程

输入程序,将其保存为m_sequence.v文件

//伪随机序列m_sequence.v

//m_out为m序列输出,速率为1MHz,长度为2^(15)-1,frame_out为帧同步信号,clk2为1MHz时钟,rst为复位信号,高电平复位,gclk为50MHz时钟

module m_sequence(input rst,gclk,output m_out,frame_out,clk2);

clk_1M U1(.rst(rst), .gclk(gclk), .clk(clk2));

m_sequence1 U2(.clr(rst), .clk2(clk2), .m_out(m_out), .frame_out(frame_out));

endmodule

创建工程:

将该代码存为clk_1M.v

//clk_1M.v 程序

//功能:将系统时钟gclk进行50分频,产生1MHz时钟

module clk_1M(rst,gclk,clk);

input rst;

input gclk;

output clk;

wire rst,gclk;

reg clk=1'b0;

reg[4:0] count=5'b00000;

always @(posedge gclk)

begin

count = count + 5'd1;

if(count == 5'd25)

begin

clk = ~clk;

count = 5'd0;

end

end

endmodule 将该代码存为m_sequence1.v

//m_sequence1.v程序

//m_out为m序列,frame_out为帧同步信号,clk2为1MHz时钟

module m_sequence1(input clr,clk2,output reg m_out, frame_out);

reg[14:0] shift_reg;

always @(posedge clk2)

begin

if(clr)

begin

shift_reg <= 15'b1;

end

else

begin

shift_reg[0] <= shift_reg[13]^shift_reg[14];

shift_reg[14:1] <= shift_reg[13:0];

m_out <= shift_reg[14];

frame_out <= (shift_reg[0] & shift_reg[1] & shift_reg[2] & shift_reg[3] & shift_reg[4] & shift_reg[5] & shift_reg[6] & shift_reg[7] & shift_reg[8] & shift_reg[9] & shift_reg[10] & shift_reg[11] & shift_reg[12] & shift_reg[13] & shift_reg[14]);

end

end

endmodule

再将这两个代码文件加入到工程中

(3)编译

添加后,对 m_sequence.v 文件进行编译

(4)仿真测试

基于Quartus 自身工具模块的仿真

第一行为复位信号,第二行为50MHz时钟信号(由晶体振荡器产生)

第三行为1MHz时钟,第四行为m序列,第五行为同步信号(周期为2^(-15) -1 个码元)

设置rst前5us为高电平,gclk为50MHz的时钟频率,clk2为1MHz的时钟频率。

运行仿真

结果显示

三、板载测试准备工作

1、引脚配置

对CRD500开发板进行引脚配置时,rst与复位键(P14位置)相连,晶体振荡器1提供50MHz时钟(M1位置),1MHz时钟信号、m序列以及同步信号由40针扩展接口输出(本项目分别配置为P3、P2、P1位置)。

注:引脚锁定后,需再次编译程序将引脚信息编译进下载文件中!

2、下载.sof格式文件

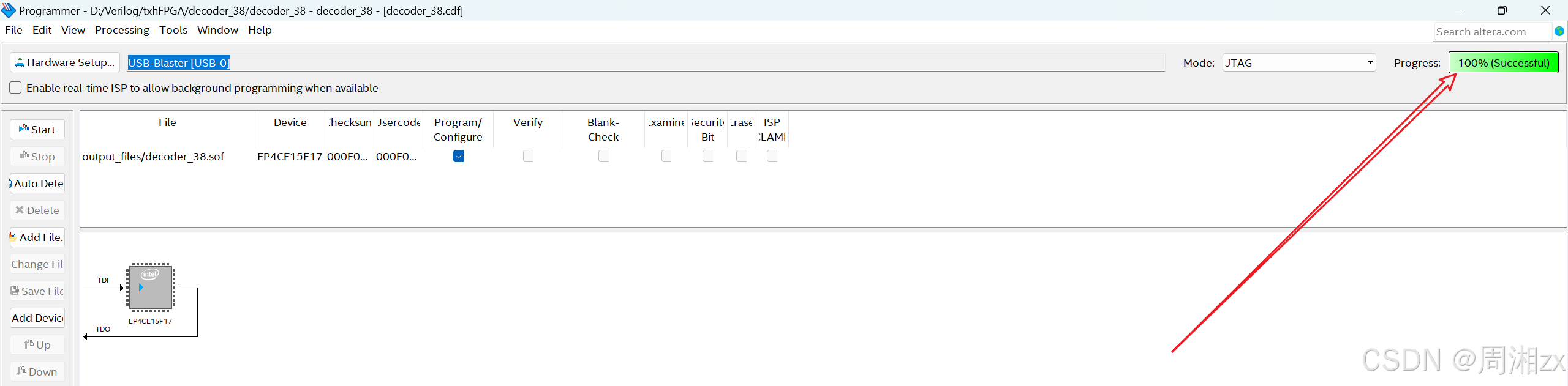

在“Tool”菜单中选择“Programmer”,进入Hardware Setup,查看是否检查到接口设备。

按下“start”开始下载,当右侧的“Process”栏显示为100%,则表示下载成功。

3、转为为.jic文件下载到FPGA

编译生成的.sof文件尽管可直接下载到FPGA中运行并进行性能测试,但断电后,由于FPGA的存储器为SRAM,而使得FPGA中的程序不复存在。要实现程序的脱机运行,还必须将程序下载到CRD500的FLASH芯片M25P16(与EPCS16兼容)中。

由于.sof格式的文件还不能直接下载到FPGA,因此,需先进行格式转换,转化成适合下载到FPGA中的格式文件,即.jic文件。

进入”Convert Programming Files“,选择文件格式、设备以及输出的文件名

选中”Flash Loader“,再点击”Add Device“添加目标器件EP4CE15

选中”SOF Data“,单击”Add File“,在对话框中选择生成好的.sof文件

完成以上操作后,单击”Generate“可生成.jic文件

然后就是下载,与.sof文件的下载方式一样

四、板载测试

示波器测试输出信号 1MHz时钟信号、同步信号、m序列的波形依次如下: