硬件知识积累 PCIE 接口

1. PCIE 是什么

中文名称:高速串行计算机扩展总线标准

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。

PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(QOS)等功能。

PCIe交由PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”,简称“PCI-e”。它的主要优势就是数据传输速率高,而且还有相当大的发展潜力。

PCI Express也有多种规格,从PCI Express x1到PCI Express x32,能满足将来一定时间内出现的低速设备和高速设备的需求。PCI-Express的接口是PCIe 3.0接口,其比特率为8Gbps,约为上一代产品带宽的两倍,并且包含发射器和接收器均衡、PLL改善以及时钟数据恢复等一系列重要的新功能,用以改善数据传输和数据保护性能。

参考资源:PCIE_百度百科 (baidu.com)

2.PCIe总线和 PCIe通道

PCIe总线是连接外部设备的线路。(就是通用的总线规格)

PCIe通道是PCIe总线的组成部分,PCIe总线包含一条或者多条PCIe通道,比如一条PCIe通道就是X1,两条PCIe通道就是X2,逐步以此类推。(其实 PCIE X2 可以理解为 PCIE X4 的有两个PCIe通道没有连接)

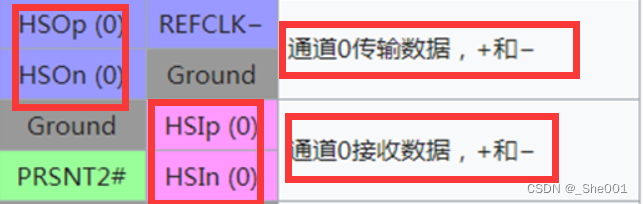

如下图所示, HSOp(0) , HSOn(0), HSIp(0),HSIn(0), 就是一组 PCIe 通道 (简单的来说)。

推荐视频:PCIe硬件电路设计01_哔哩哔哩_bilibili

参考资源:PCIE总线_、、Joker的博客-CSDN博客

3.PCIE 引脚定义

3.1 引脚解释

PRSNT1/2#: 热插拔信号引脚

SMCLK+SMDAT:SMBUS信号接口,用于管理pcie设备。

TCK+TDI+TDO+TMS+TRST#:jtag接口,用于调试pcie设备。

WAKE#:唤醒引脚。

PERST#:复位引脚。

CLKREQ#:时钟请求引脚。

REFCLK+/-:差分时钟引脚。

HS O/I p/n (0):差分IO引脚。

PCI 和PCIE 传输速度推荐文章:PCIE总线_、、Joker的博客-CSDN博客每个引脚的含义详细解释推荐文章:PCIe总线的基础知识-CSDN博客

PCIE X2 硬件推荐文章:PCIE总线硬件设计篇_pcie硬件设计-CSDN博客

3.2图列图片

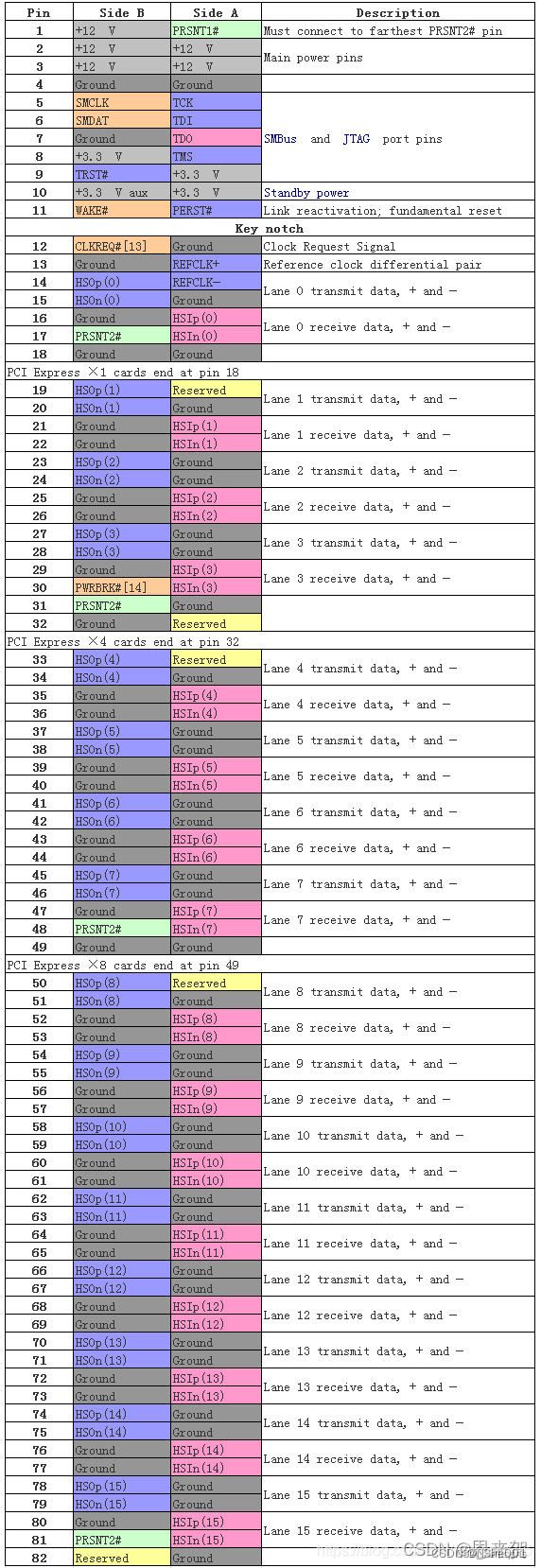

3.3 PCIE X1,X4,X8,X16 的引脚定义

参考文章:PCIe总线引脚定义_pcie引脚-CSDN博客

参考文章:PCI-E 1x, 4x, 8x, 16x 接口定义_pcie接口定义-CSDN博客

推荐文章:pcie接口引脚定义 pcie接口都可以插什么-爱你网 (ini5.com)