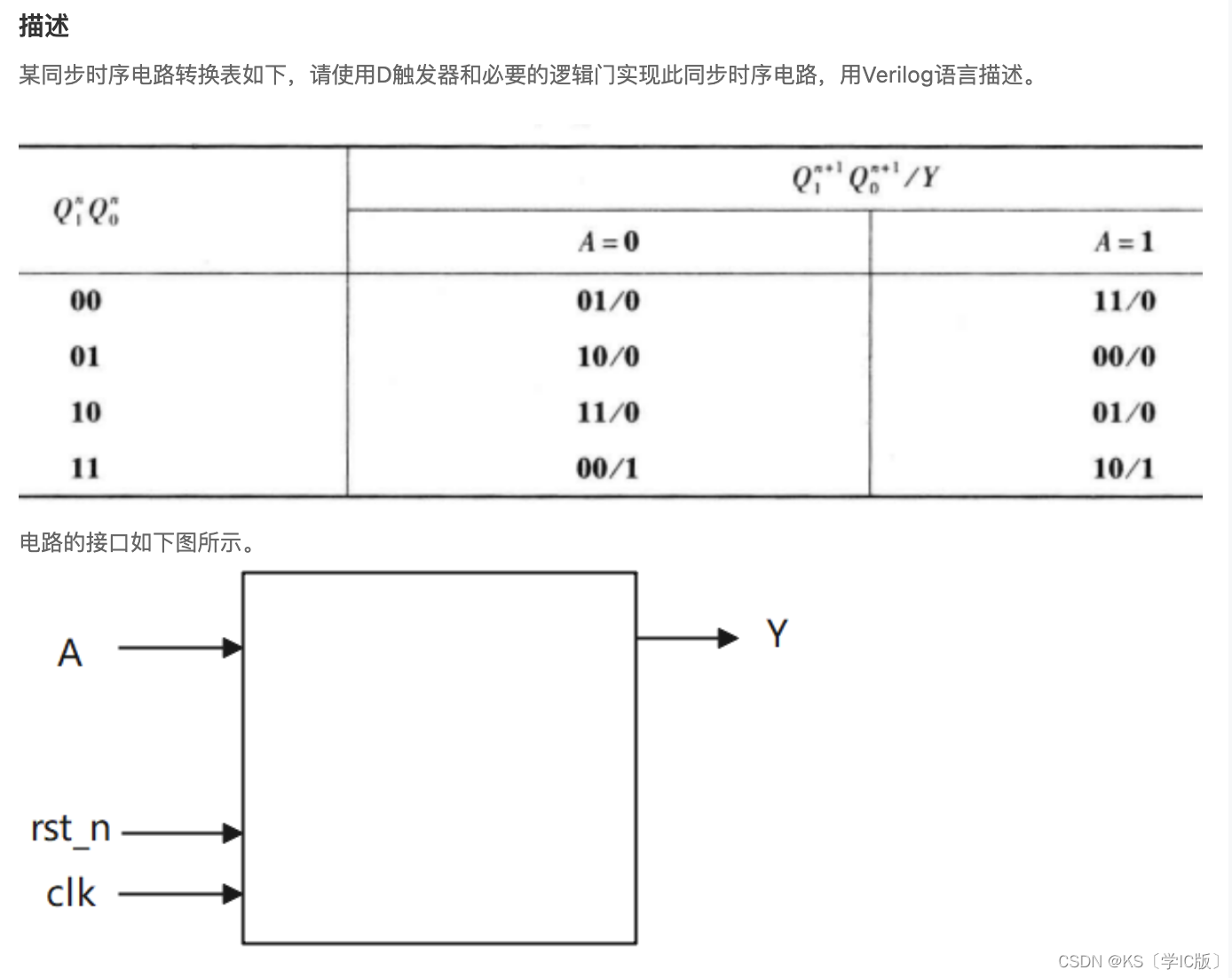

「Verilog学习笔记」根据状态转移表实现时序电路

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

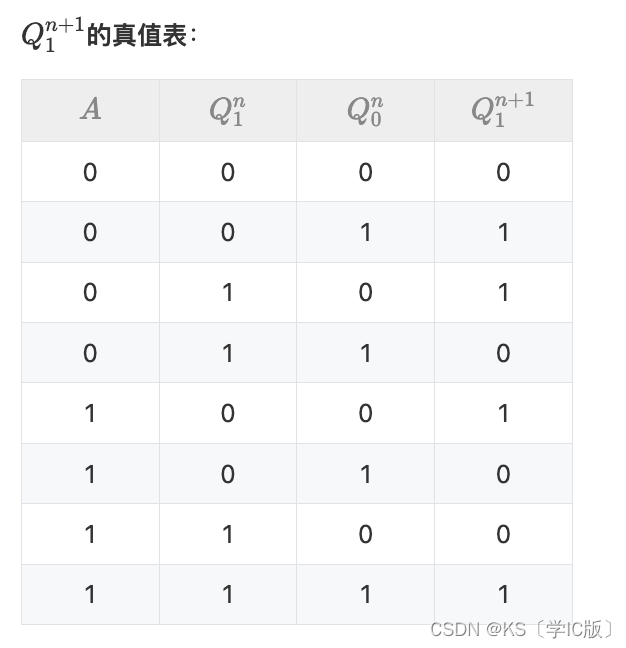

分析

可得逻辑表达式为

可得逻辑表达式为

`timescale 1ns/1ns

module seq_circuit(

input A ,

input clk ,

input rst_n,

output wire Y

);

reg q0, q1 ;

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) begin

q1 <= 0 ;

end

else begin

q1 <= A ^ q0 ^ q1 ;

end

end

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) begin

q0 <= 0 ;

end

else begin

q0 <= ~q0 ;

end

end

assign Y = q0 & q1 ;

endmodule