电路的基本原理

文章目录

- 一、算数逻辑单元(ALU)

- 1、功能

- 2、组成

- 二、电路基本知识

- 1、逻辑运算

- 2、复合逻辑

- 三、加法器实现

- 1、一位加法器

- 2、串行加法器

- 3、并行加法器

一、算数逻辑单元(ALU)

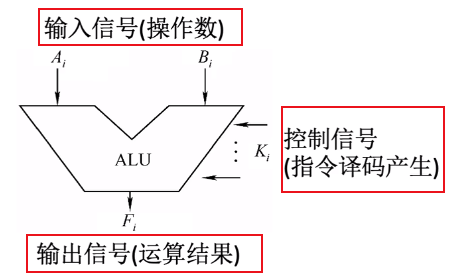

1、功能

算术运算:加、减、乘、除等

逻辑运算:与、或、非、异或等

辅助功能:移位、求补等

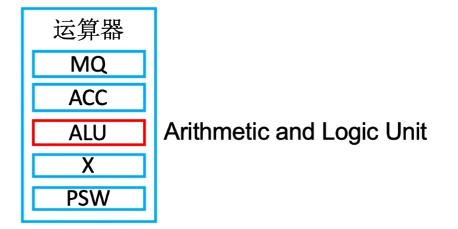

2、组成

二、电路基本知识

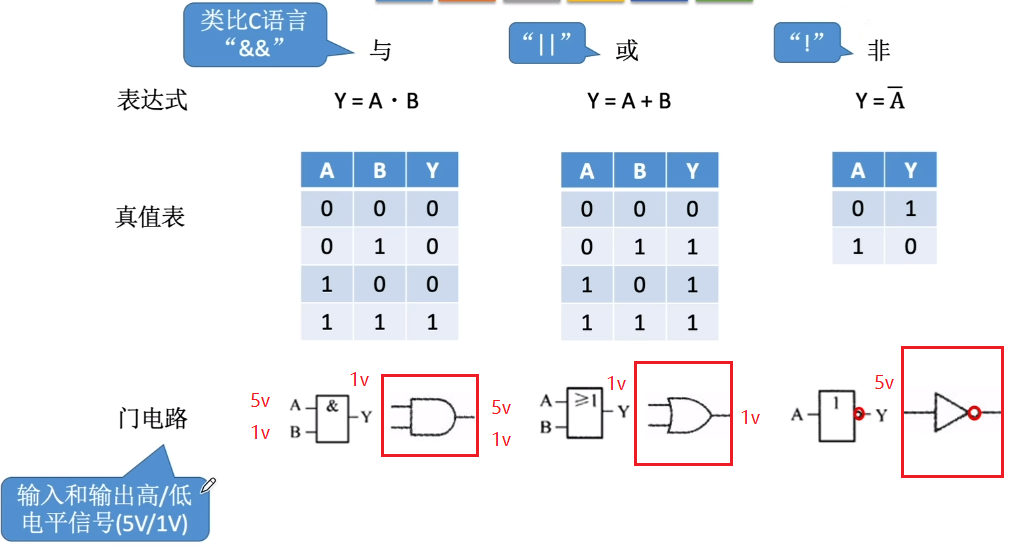

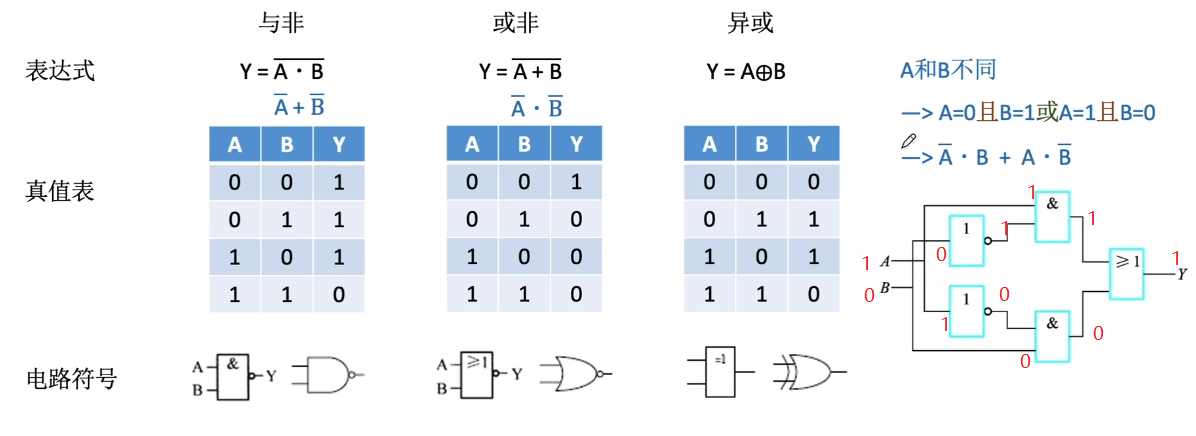

1、逻辑运算

优先级:与>或,先算与,再算或

Eg:AB+CD先算与再算或

A(C+D)=AC+AD——分配律

ABC=A(BC)——结合律

A+B+C=A+(B+C)——结合律

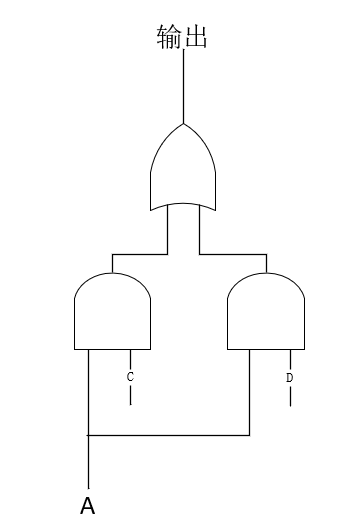

Eg:实现AC+AD

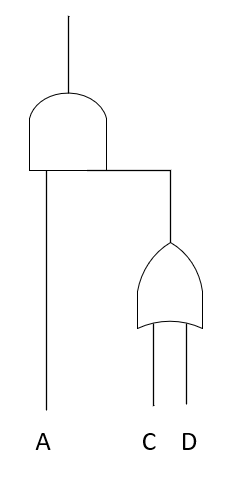

2、复合逻辑

异或门可用与、或、非组合实现

三、加法器实现

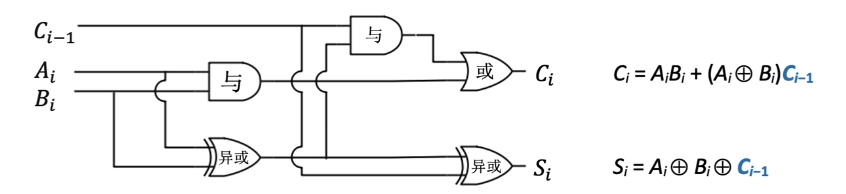

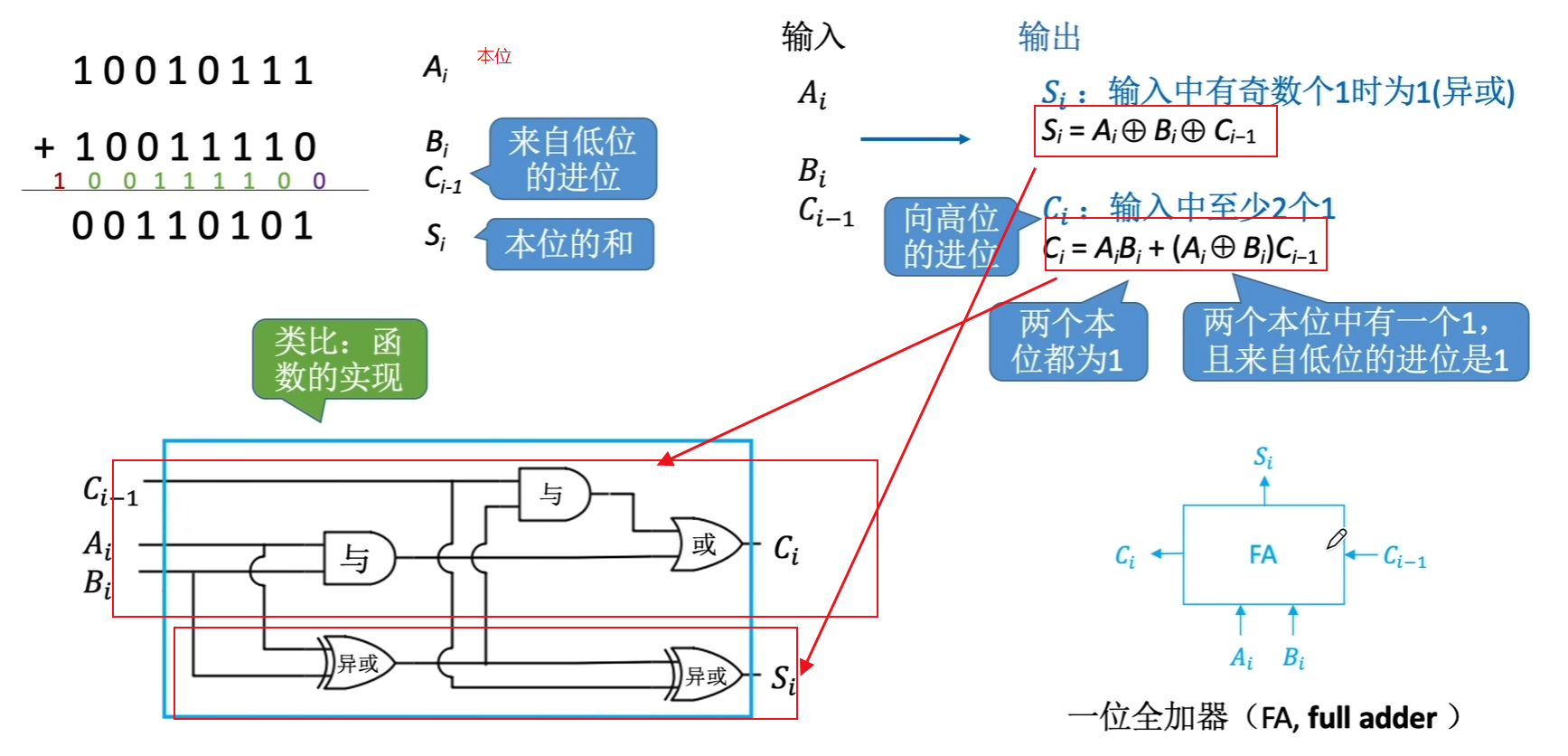

1、一位加法器

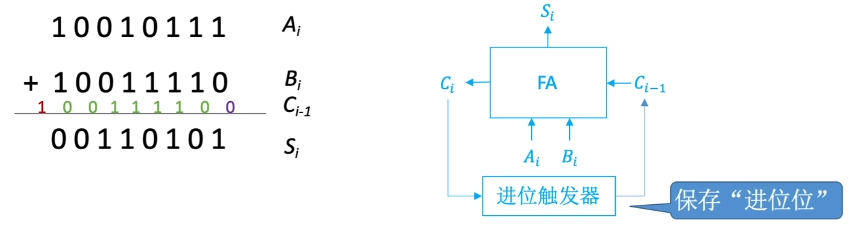

2、串行加法器

串行加法器:只有一个全加器,数据逐位串行送入加法器中进行运算。进位触发器用来寄存进位信号,以便参与下一次运算。

如果操作数长n位逐位地送回寄存器。加法就要分n次进行,每次产生一位和,并且串行

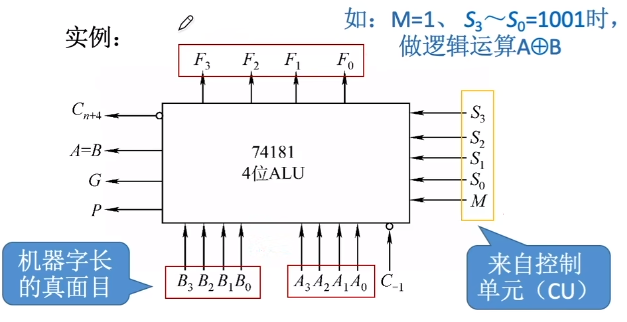

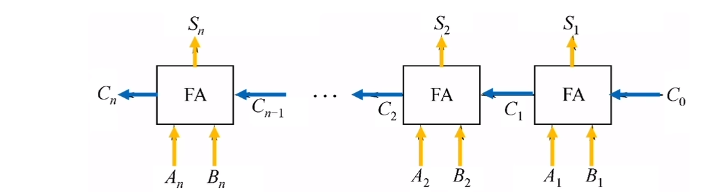

3、并行加法器

串行进位的并行加法器:把n个全加器串接起来,就可进行两个n位数的相加。

串行进位又称为行波进位。每一级进位直接依赖于前一级的进位,即进位信号是逐级形成的