单片机学习4——中断的概念

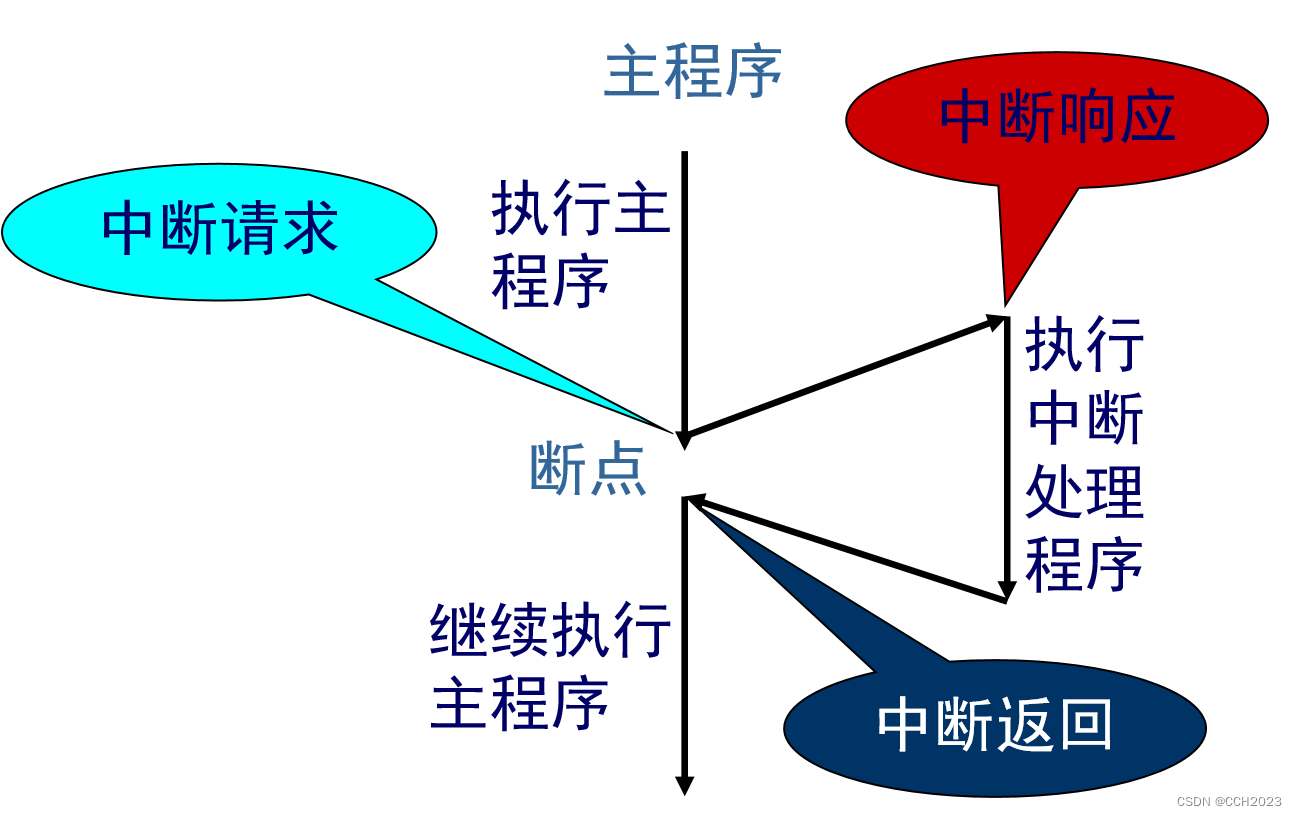

中断的概念:

CPU在处理A事件的时候,发生了B事件,请求CPU迅速去处理。(中断产生)

CPU暂时中断当前的工作,转去处理B事件。(中断响应和中断服务)

待CPU将B事件处理完毕后,再回到原来A事件中断的地方继续处理A事件。(中断返回)

这个过程,就叫做中断。

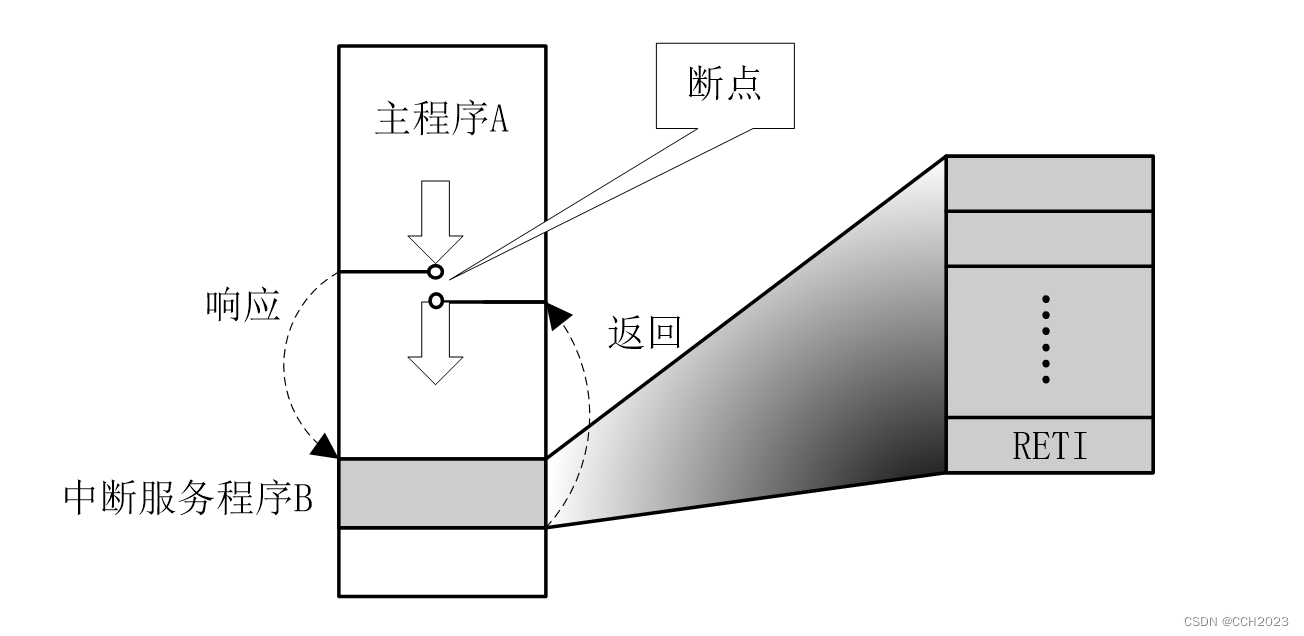

引起CPU中断的根源叫作中断源,中断源向CPU的请求,叫作中断请求。CPU暂时中断原来的A事件,转去处理B事件。对B事件处理完毕后,再回到原来被中断的地方(即断点)。称为中断返回。实现上述中断功能的部件叫作中断系统(中断机构)。

随着计算机技术的应用,人们发现中断技术不仅解决了快速主机与慢速I/O设备的数据传送问题,而且还具有如下的特点:

1)分时操作:CPU可以分时为多个I/O设备服务。

2)实时响应:CPU能够及时处理应用系统的随机事件,系统的实时性大大增强。

3)可靠性高:CPU具有处理设备故障和掉电等突发性事件的能力。从而使系统的可靠性提高。

8051中断系统的结构:

8051中断系统有5个中断源,2个优先级,可实现二级中断嵌套。

第二个中断请求的优先级比第一个中断请求要高。

中断嵌套,也叫抢占。

抢占优先级的概念,优先级高的中断可以打断优先级低的中断执行,从而形成嵌套。

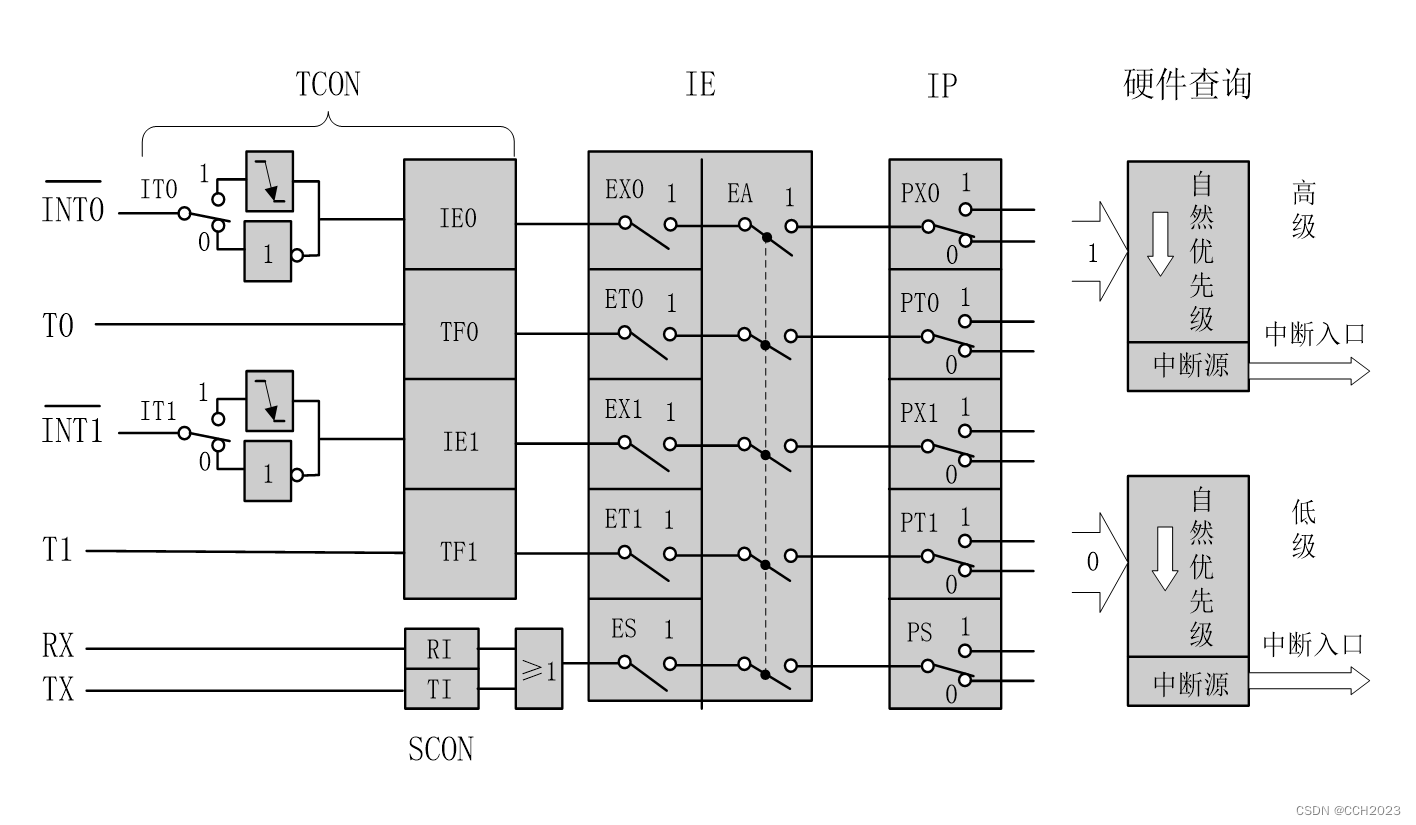

INT0、T0、INT1、T1、RXTX,一共是五个中断源。

外部中断源INT0和INT1;

T0和T1:片内定时器计数器;

RX和TX:数据传输中断请求。串行口。

当中断源满足条件产生中断请求的时候,中断请求标志位会置1,向CPU申请中断。

CPU响应中断的时候,TCON的中断请求标志位由硬件自动清除,则须为软件清零。

IT0外部中断0(INT0)触发方式选择位,由软件设置。

1、低电平触发方式,INT0(P3.2)引脚上低电平可引起中断。

2、下降沿触发方式,INT0(P3.2)引脚上电平由高低负跳变可引起中断。

IT0 IT1

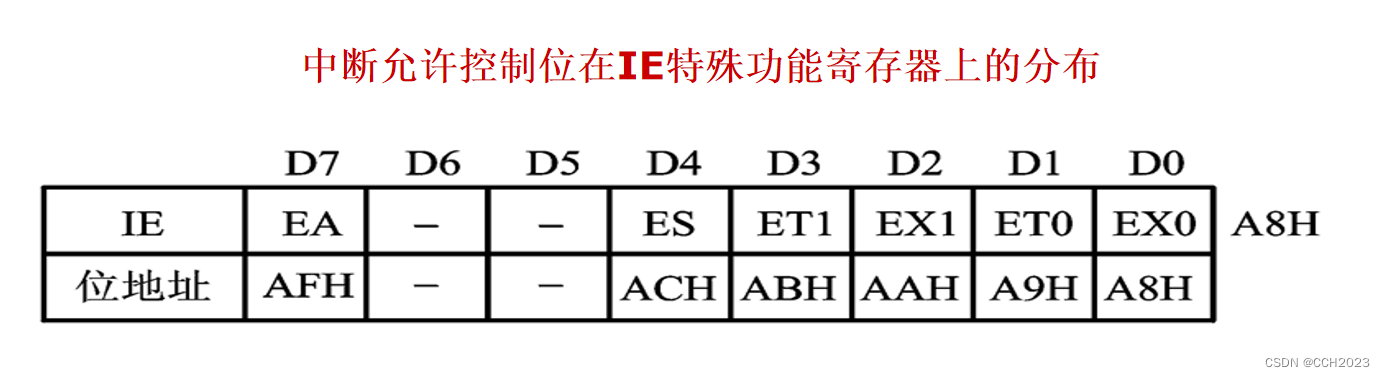

IE: 中断使能寄存器

EX0

ET0

EX1

ET1

ES

这是5个中断使能。

EA

中断总开关。

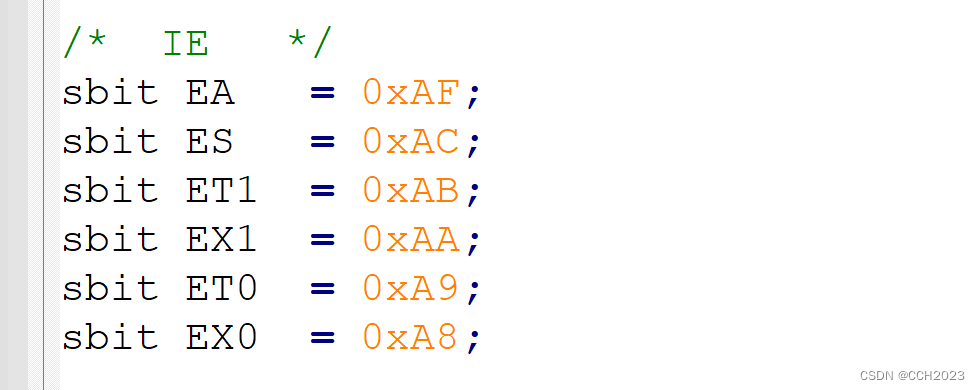

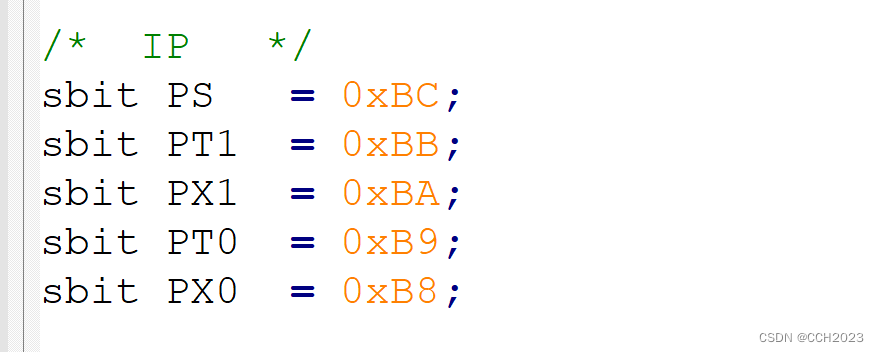

reg51.h文件:

IP:中断优先级寄存器:

当把某一位设置为1的时候,这一位的优先级就比其他位的优先级高了。

设置为1的时候,表示高优先级;

设置为0的时候,表示低优先级。

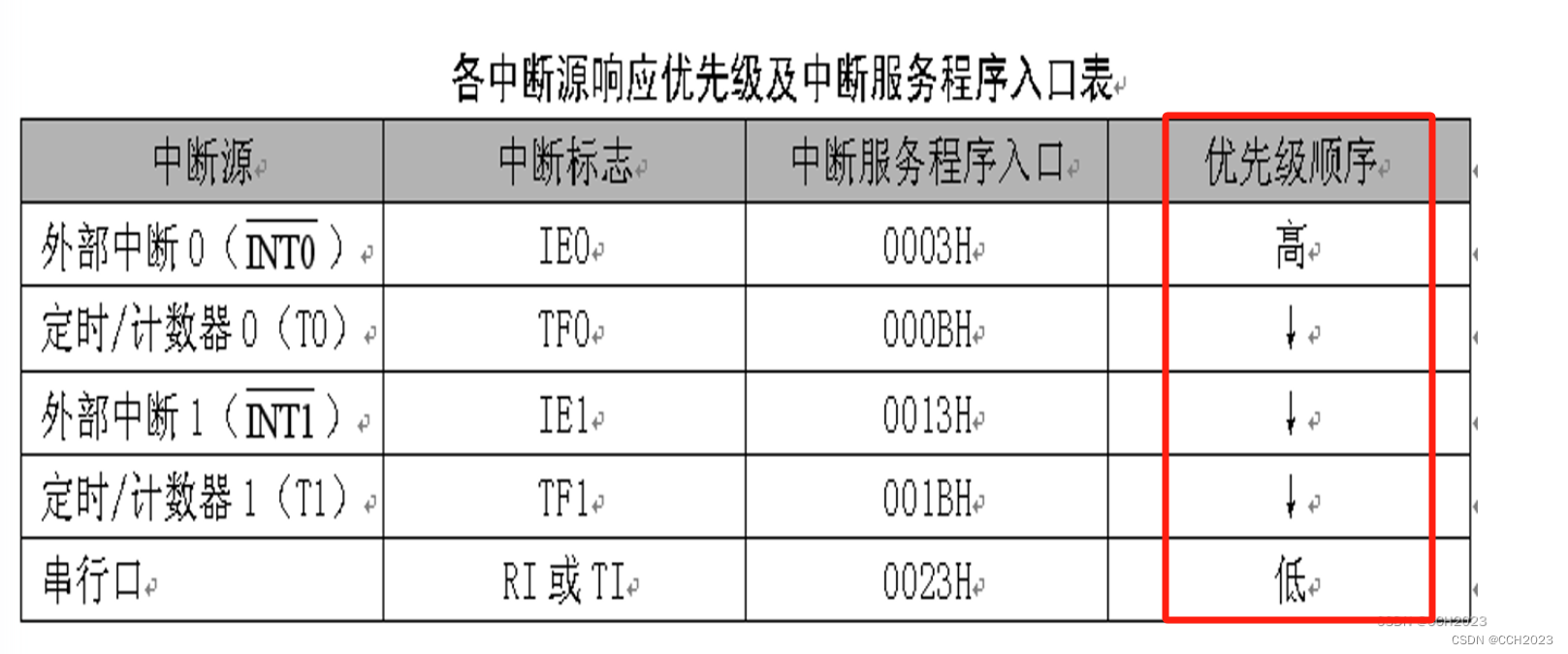

下图中表示的是固有优先级(自然优先级),上面的优先级高于下面的优先级。这里的优先级不具有抢占性。

当多个中断同时存在的时候,就进行判断比较,或者叫仲裁。就是当中断使能的情况之后,突然同时多个中断请求响应,这个时候必须有先后的顺序,这就是非抢占式的作用。

抢占优先级和非抢占优先级的协同,可以使得单片机有条不紊地工作,既不会无休止地嵌套,又可以保证必要时紧急任务得到优先处理。在后面会大量地使用到中断系统。