【【ZYNQ-自定义IP核-IP核封装于接口定义实验】】

ZYNQ-自定义IP核-IP核封装于接口定义实验

我们 应该怎么封装

用一个示例

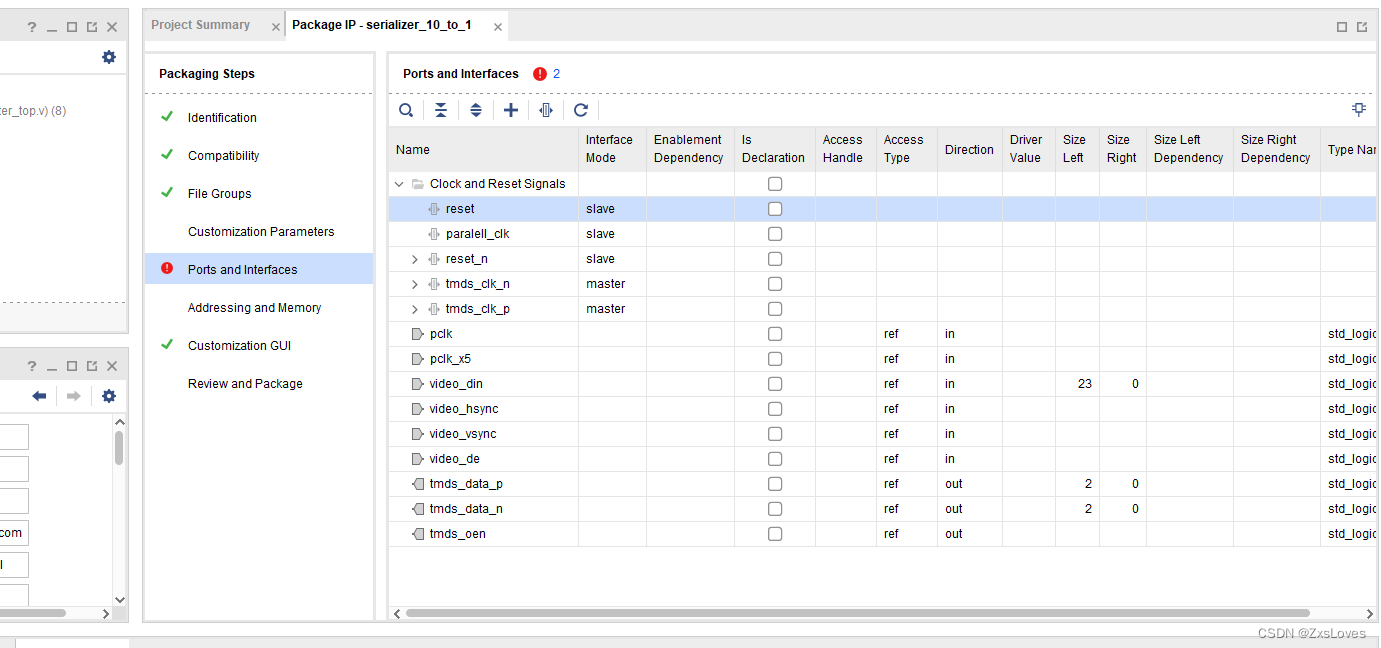

我们自动生成的是这个样子的

对比一下 真实 的 顶层文件

module dvi_transmitter_top(

2 input pclk, // pixel clock

3 input pclk_x5, // pixel clock x5

4 input reset_n, // reset

5

6 input [23:0] video_din, // RGB888 video in

7 input video_hsync, // hsync data

8 input video_vsync, // vsync data

9 input video_de, // data enable

10

11 output tmds_clk_p, // TMDS 时钟通道

12 output tmds_clk_n,

13 output [2:0] tmds_data_p, // TMDS 数据通道

14 output [2:0] tmds_data_n,

15 output tmds_oen // TMDS 输出使能

16 )

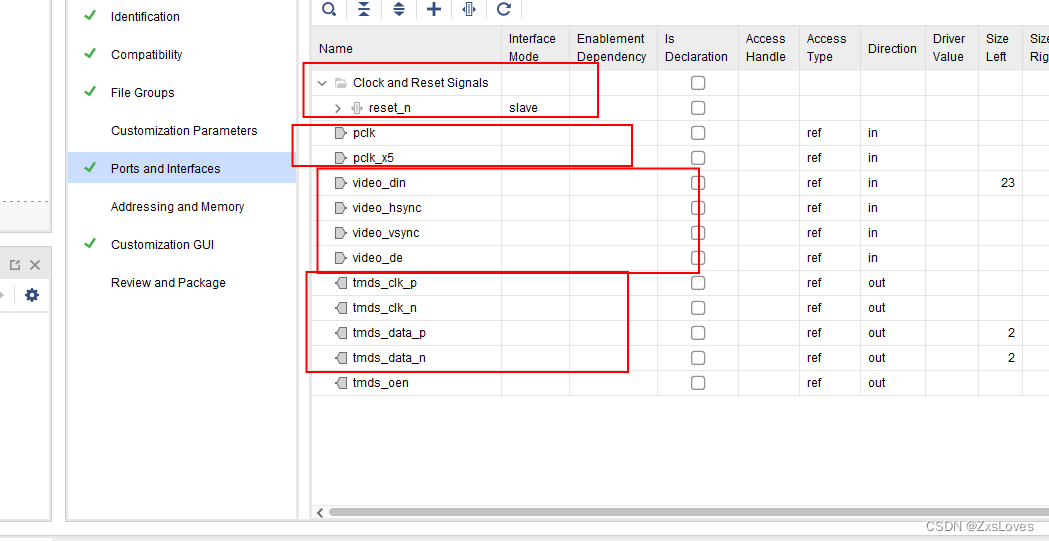

我们删除 不存在的端口

发现还是存在了一些错误

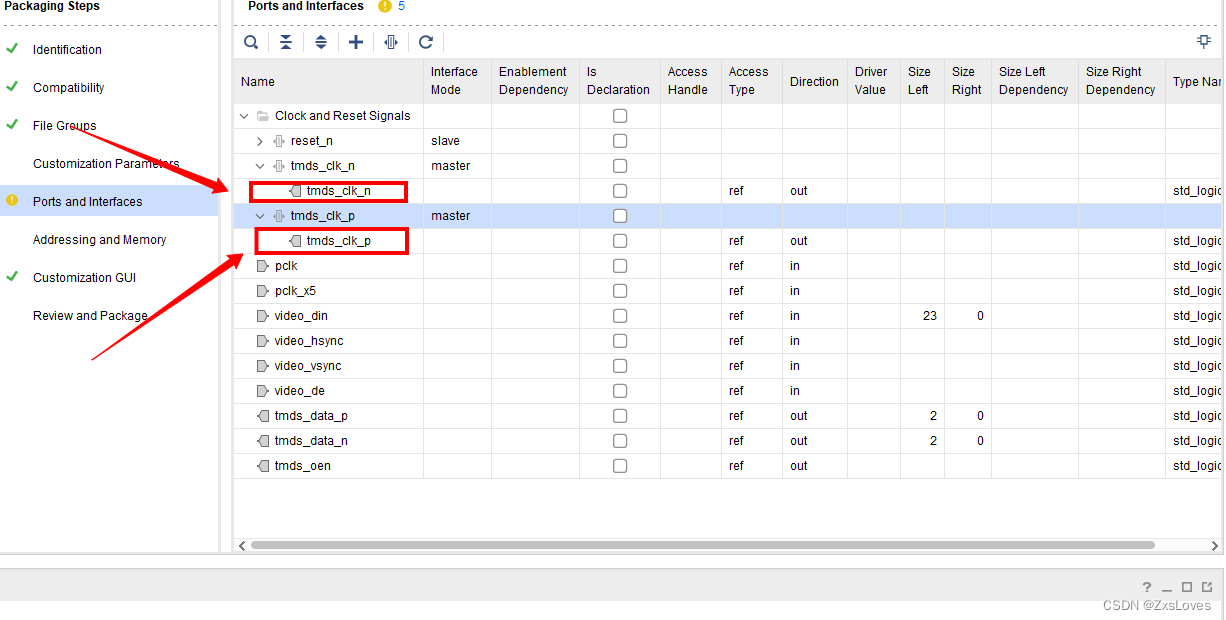

不是时间端口 被错误识别成了 时间端口

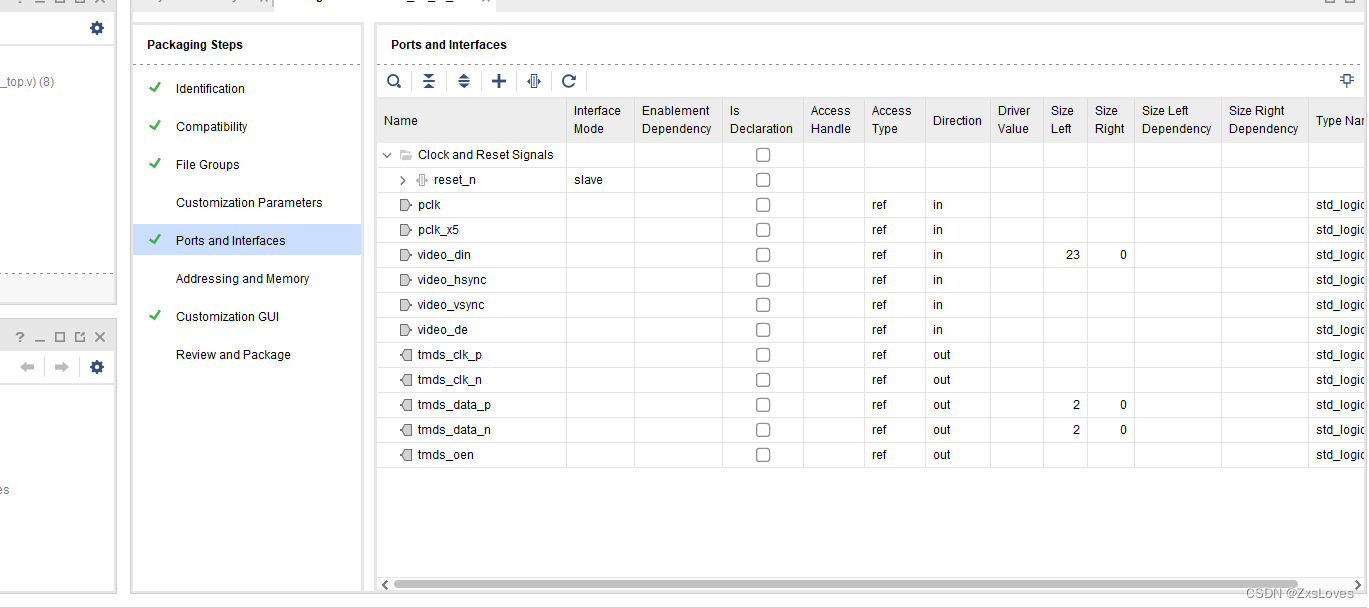

移除之后 就会形成新的端口展示

信号就这么多 我们接下来 需要 做的是

把这这些信号 归类 划分想要使用的 封装在一起的信号

时钟信号 有两个 由于 时钟接口 每个时钟接口 只包含一路时钟信号 因此我们需要为pclk 和 pclk_x5 各添加一个时钟接口

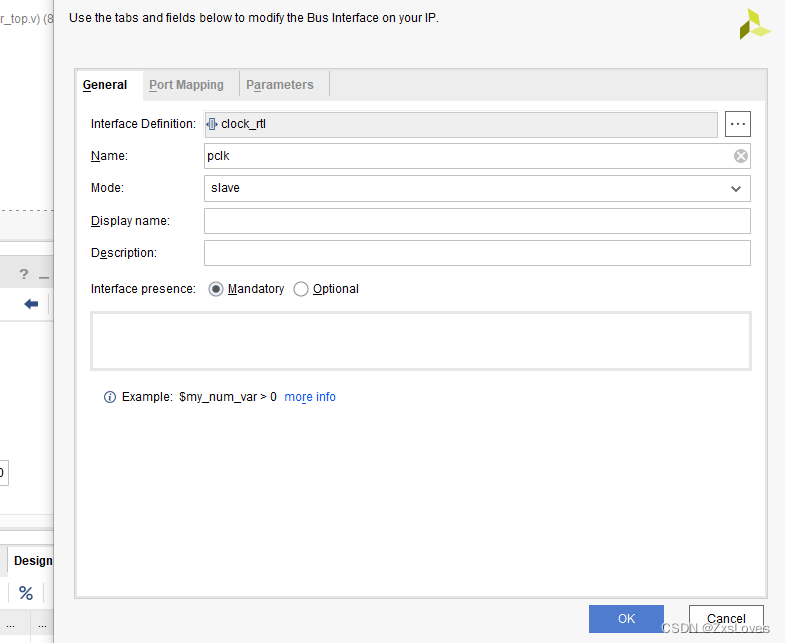

我们选中点击 add BUS interface

我们可以看到 默认的接口类型是 默认的接口类型是 aximm_rtl 这是不对的 需要换成别的模块

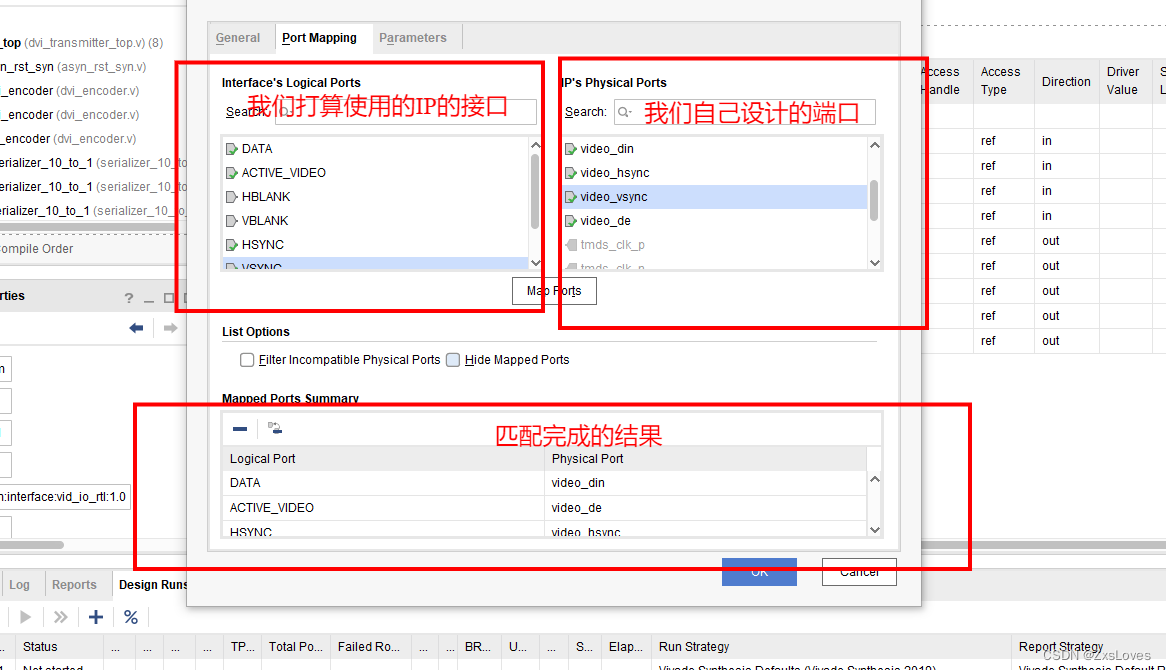

再修改成clk之后 我们还需要进行 端口匹配 Port Mapping

当我们如法炮制 配置完 PCLK 和 PCLK_x5

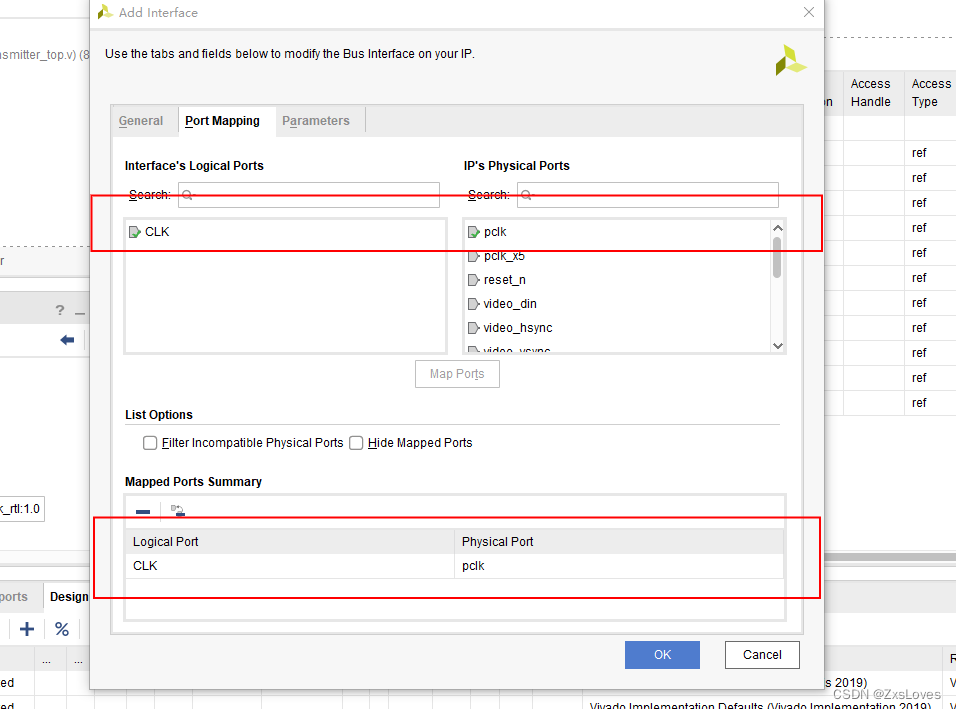

接下来我们配置大的 视频接口

我们点击想要配置的视频接口的任意一个

然后再 general中搜索 想要配置成的 接口 在本处我们选择的是 vid_io_rtl

因为这个端口 包含的不单单是一个

虽然上面只有一个的也要点端口印射

我们就点一下吧

DATA是视频像素数据,ACTIVE_VIDEO 是视频有效信号,HSYNC 和 VSYNC 分别是视频的行同步和场同步信号。

插入一个题外话 在 做 VDMA的时候 别人告诉我 以后在公司的标准 其实只要几个关键信号就完全可以表示信号传输 了

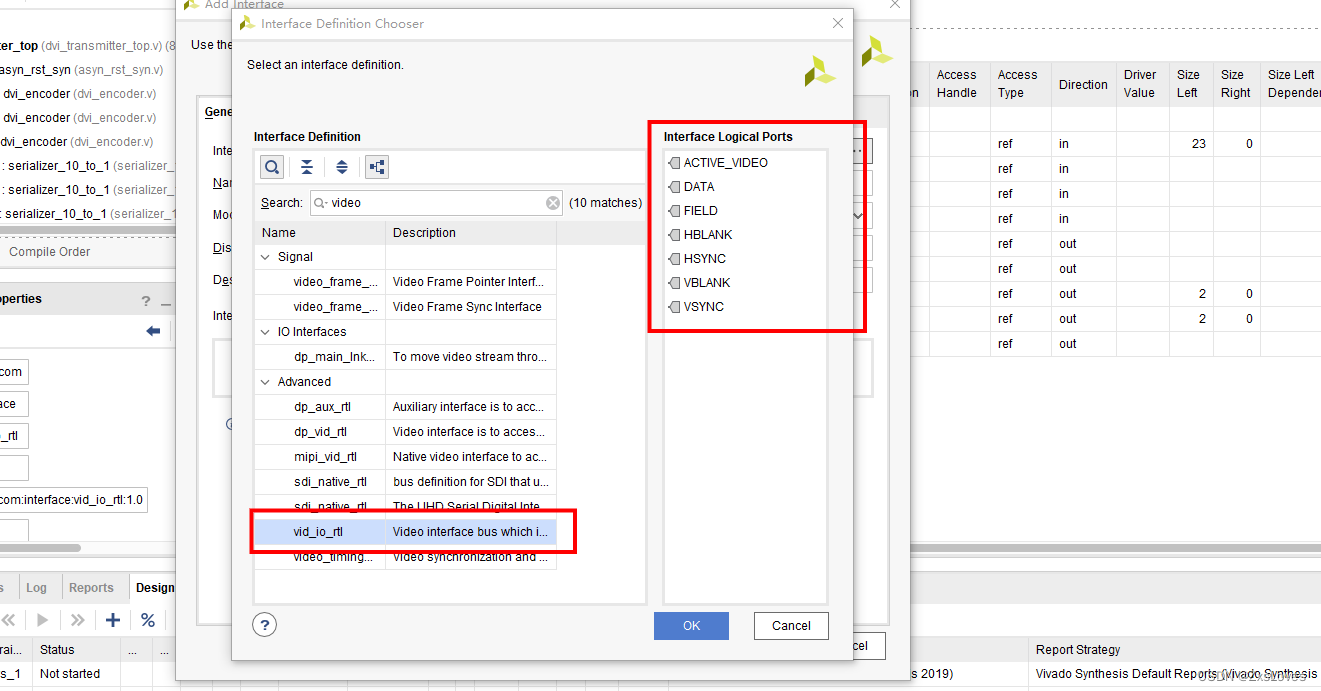

上面是标准的简单的 但是还会遇到一种情况就是我们想要形成自定义的接口 并不是 官方提供的示例的那几种 接下来我们该怎么办

点击Tools “Create new interface definition”

创建自己想要的接口

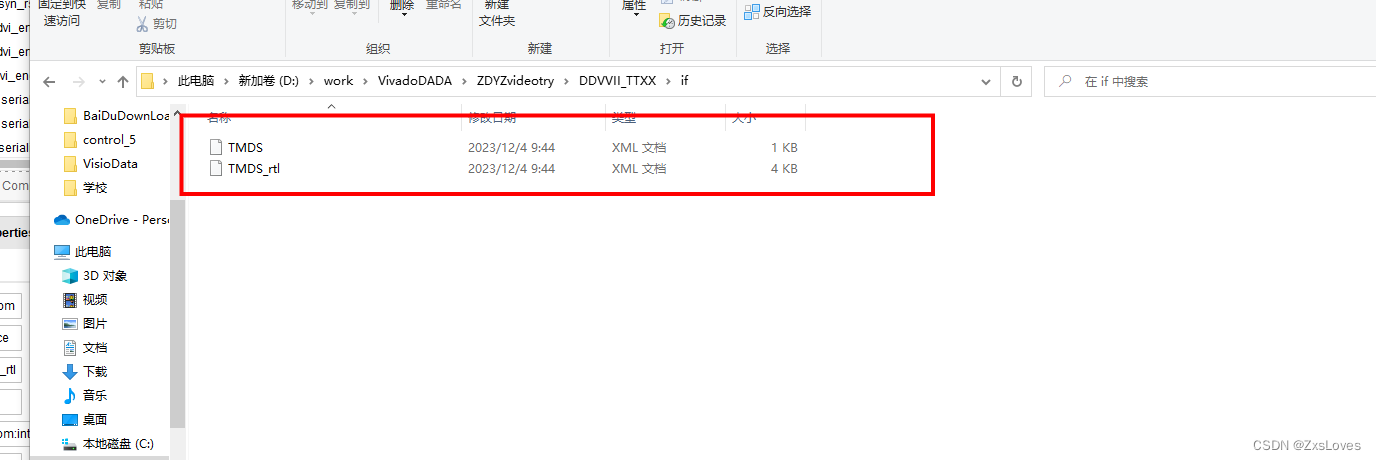

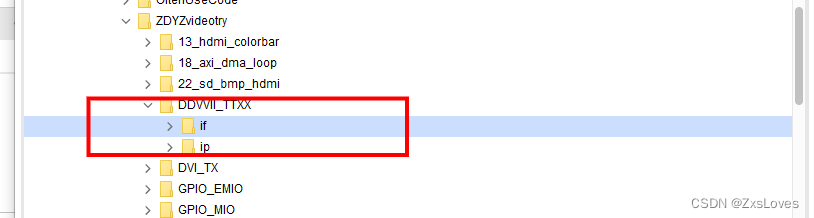

if 是 interface 接口的意思

ip 是 IP 的 意思

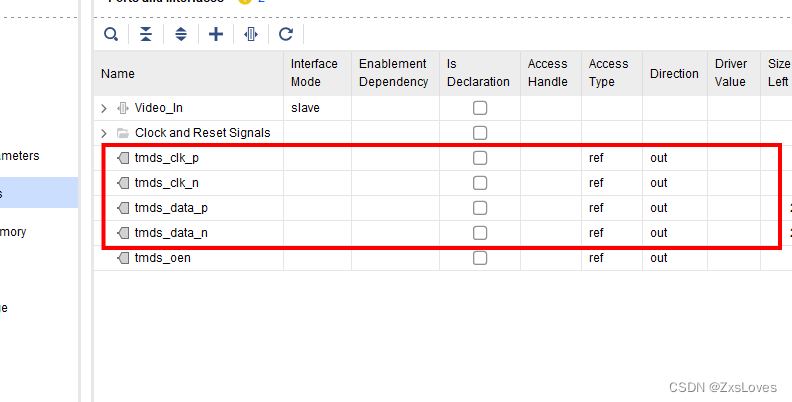

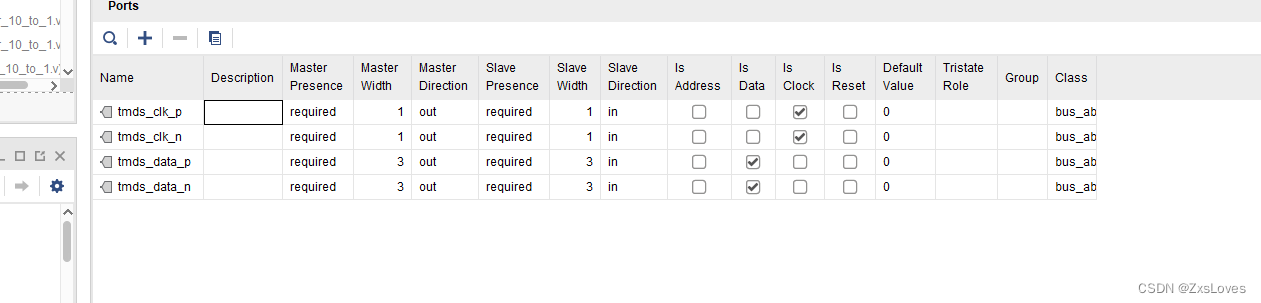

我们需要把接下来的四个封装在一起

先注意我们要添加的端口

(其中 tmds_data_p 和 tmds_data_n 的位宽为 3 位)

tmds_clk_p (时钟端口)

tmds_clk_n ( 时钟端口 )

tmds_data_p (3 位)

tmds_data_n (3位)

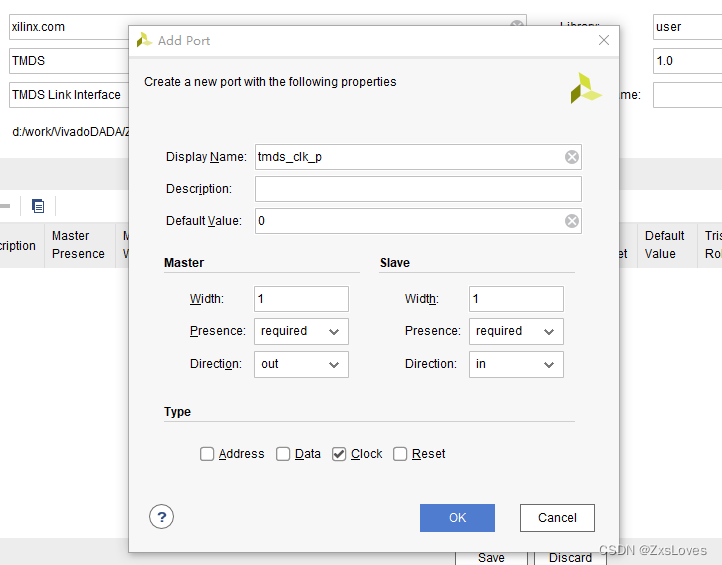

对于第一个 我们采用如下的设置

tmds_clk_p 时钟端口

tmds_clk_n照旧

接下来 我们完成data的配置

这时候我们点开if 就会发现这个文件的出现了