FPGA实现串口升级及MultiBoot(四)MultiBoot简介

缩略词索引:

K7:Kintex 7

V7:Vertex 7

A7:Artix 7

我们在正常升级的过程(只使用一个位流文件),假如:(1)因为干扰通信模块收到了一个错误位;(2)或者烧写进FLASH时突然断电,导致位流文件不完整;(3)再或者使用软核升级应用程序时,突然断电或者接收文件错误,导致应用程序启动不了;(4)再再或者外场人员烧写了不适配本FPGA的升级程序。以上这些都是我们升级时候常见的问题,以上问题可以总结为以下几点:

位流错误 -- 对应情况(1)、(2)

启动超时 -- 对应情况(3)

位流ID不匹配 -- 对应情况(4)

所以我们使用单一的文件进行远程升级的时候,很有可能因为各种情况导致FPGA不能启动,就需要现场使用JTAG进行处理。所以为了避免这些情况的发生,我们需要两个固件,其中一个在一般情况下不动,只升级另一个程序,两个程序在以上情况发生时,就启动第一个程序,就可以重新升级了。

以上这种应对方式对于AMD-Xilinx FPGA来说,官方也想到了针对以上情况的解决方式-即MultiBoot。

MultiBoot介绍

其实这个理念不难理解,你从实际使用出发去理解会比直接理解要容易多,实际使用就从上面的各种情况出发,就很容易理解官方为啥使用MultiBoot进行问题的规避和解决。

但是,因为每个人接受的理念不同,所以我们还是要从正面“突进”,去解释MultiBoot。

MultiBoot 是一个FPGA实现的一种解决方案,支持不同位流之间切换以规避在远程更新中出现的问题。

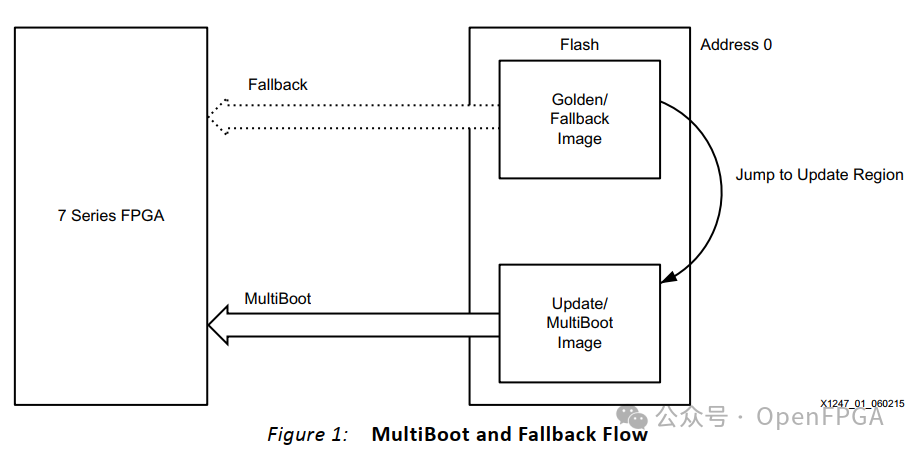

当在 MultiBoot 启动配置过程中检测到错误时,FPGA 会触发回退(外国名:Fallback),这样就可以确保已知好的设计可以加载到设备中。这种解决方案主要是在一个FLASH中烧写两个位流文件。其中:

Fallback, 别称 “golden bitstream”

MultiBoot, 别称 “update bitstream”

以上两个文件,习惯叫Golden位流,烧写在Golden区;MultiBoot位流,烧写在MultiBoot区。以上依个人习惯自己匹配,对应好相关的名称和位置就可以。

MultiBoot原理

Golden位流是从Flash中的0地址开始运行;其帧头会包括WBSTAR(next_config_addr)寄存器里面指定的下一个启动地址等信息。FPGA器件上电后会从0地址开始加载Golden位流后,会根据里面的设定来决定加载Golden位流还是直接跳转到MultiBoot位流存储地址去执行MultiBoot位流;当MultiBoot位流加载时候遇到错误,Fallback电路会触发去重新从0地址去加载Golden 位流。MultiBoot 和 Fallback 流程如图1所示:

图1:MultiBoot 和 Fallback 流程 - 参考:XAPP1247

图1:MultiBoot 和 Fallback 流程 - 参考:XAPP1247

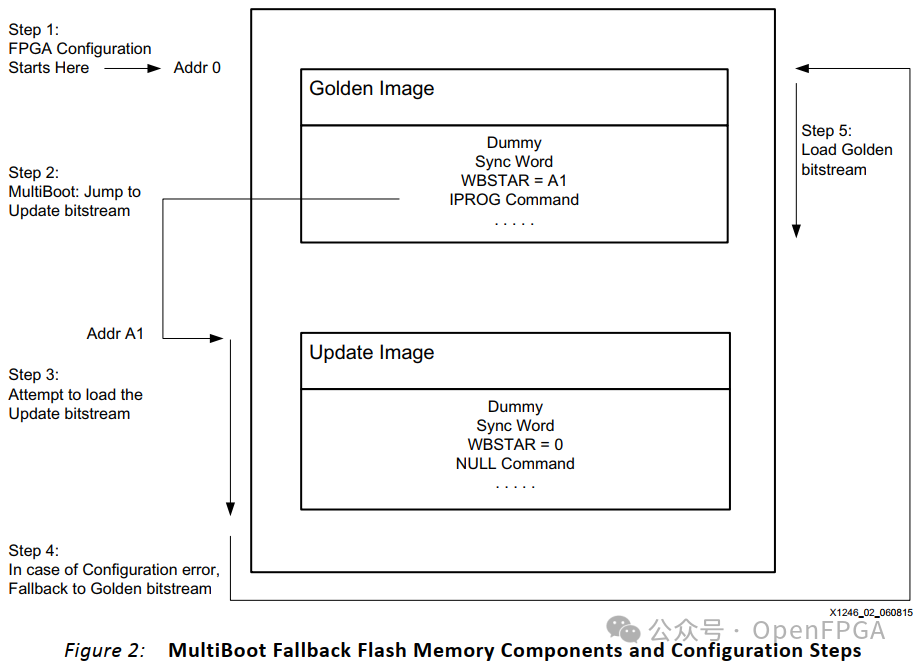

Golden位流从FLASH地址 0 开始执行后。按照启动流程,一旦遇到 IPROG 命令,就会跳转到Golden位流中 WBSTAR 寄存器中指定的FLASH地址位置,配置逻辑会尝试加载更新比特流。如果配置逻辑由于错误无法加载更新位流,则会发生Fallback,配置逻辑会将 INIT_B 和 DONE 拉低,清除配置内存,并重新从地址0处加载Golden位流重新启动配置过程,在 Fallback 期间,为了防止不断的重新,FPGA 会忽略 WBSTAR 和 IPROG 命令,详细流程见图2.

图2:MultiBoot Fallback 流程和配置步骤 - 参考:XAPP1247

图2:MultiBoot Fallback 流程和配置步骤 - 参考:XAPP1247

MultiBoot 关键技术

MultiBoot 关键技术主要主要分为以下几种:一个指令、二种位流、三种方式、四样错误。针对以上四句话我们接下来详细分析。

一个指令

这个指令大家应该都知道,在上一篇文章中也详细介绍了就是IPROG 指令。这个就是MultiBoot的核心命令(实现MultiBoot基本),后续的内容基本离不开这个指令,上一篇文章中《配置文件框架》介绍了这个指令的位置及在启动流程中位于第几步。

二种位流

这里没有说是二“个”位流,因为在复杂架构种不止一个位流,但是按照功能划分就是位于Golden区的Golden位流及位于MultiBoot区的MultiBoot位流。

三种方式

这里指的是 IPROG 指令嵌入位流种的三种方式,分别为:1)通过约束脚本添加;2)通过ICAPE2原语添加;3)通过AXI HWICAP写入IPROG指令。

这几种方式后面的文章会在实例解析。

四样错误

四样错误指触发FallBack的四种错误,分别为:

ID Code错误 - 指配置文件中的器件型号和当前器件不匹配。

CRC错误 - 指配置数据送入FPGA之后会进行校验,如果数据不一样则会提示CRC错误。

Watchdog超时 - 指在规定的时间内如果无法配置成功,则触发Watchdog超时

BPI地址越界 - BPI是只针对BPI模式的,和Watchdog有一点类似,都是在一段时间内如果没有加载成功,地址会逐步增加,计时器会逐步增加,超过范围后就触发Fallback。

ID Code错误指的是ID Code不对,这在器件启动第五步种出现错误,这种情况大概率是烧写错误镜像了,所以没什么好解释的。

当存在Multiboot镜像的时候,如M镜像的内容出现问题,则会触发CRC校验错误,这样可以保证镜像加载成功之后,数据是没有问题的。但是如果没有Multiboot镜像,则CRC校验无法进行,或者加载到一半就挂死了。这个时候就需要Watchdog来触发Fallback。只要一定时间内加载没有完成,就一定会触发Watchdog超时。所以CRC是用来保证加载正确的,Watchdog是用来保证一定会提示加载失败的。注意,Watchdogd的计时设置,请设置好然后实际测试一下,而不要仅仅凭经验/文档来推断一个合适的值。当发生了Fallback之后,工程会反跳回0地址开始加载,从新加载G镜像。这里,FPGA内部的配置寄存器会做记录,当发生Fallback之后,会自动忽略IPROG命令,直接加载G镜像后续的部分,来保证G镜像有机会被完整的加载。

BPI地址越界就和上面解释的一样,没什么多说的了。

总结

MultiBoot的实现总结起来就:一个指令、二种位流、三种方式、四样错误。接下来就是按照上面的顺序实际操作,加深理解。

PS:这类文章阅读量比较低,希望大家能多多点赞转发。同时大家有问题可以在相应文章下方留言讨论~