操作系统——操作系统逻辑结构

0.关注博主有更多知识

操作系统入门知识合集

目录

2.1操作系统的逻辑结构

思考题:

2.2CPU的态

思考题:

2.3中断机制

2.1操作系统的逻辑结构

操作系统的结构指的是操作系统的设计和实现思路,按照什么样的结构设计、实现。

操作系统的逻辑结构分为三种:

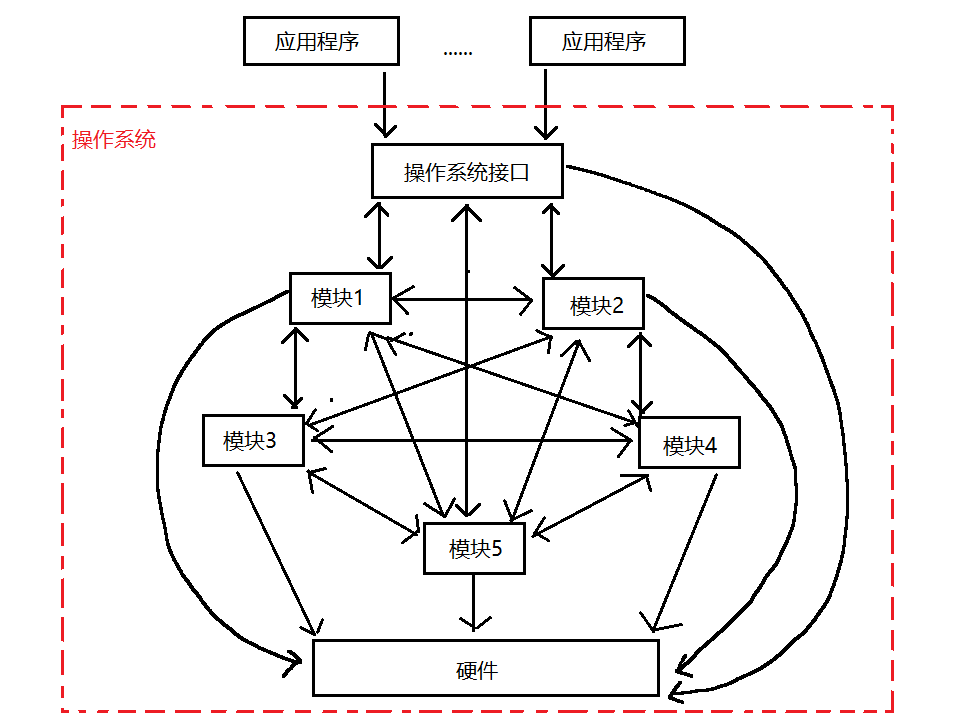

1.整体式结构:整体式以模块为基本单位构建。操作系统的实现(实现操作系统的代码),其每一个功能对应一个函数,一个函数就相当于一个模块。

public:

CVechileSampleLabelDlg(CWnd* pParent = NULL);//标准构造函数

//操作系统的每一个功能对应一个函数

void InitMyBrandTree() :

void readPath(Cstring src_path, std: :vector<CString> &vectorImageList);

void ShowMatlmageInControl(cv : :Mat& matImage,UINT nControlID);

void ToIamgeInnerPoint(int Xo,int Yo,int X1,int Y1);

void DrawRectangle(HWND m_HWnd,int x1,int y1, int x2,int y2) ;

void EnableVechileROI (BOOL bEnable):

void ClearVechileROIO:

void EnableVechileDetai1 (B0OL bEnable);

void ClearVechileDetail( );

void EnableVechileClass (BOOL bEnable);

void ClearVechileClass();

void EnableVechileBrand (BOOL bEnable) ;

void ClearVechileBrand();

void EnableVechileColor(BOOL bEnable) ;

void ClearVechileColor();

其特点在于模块化的设计、编码和实现了调试独立,方便不同模块之间的开发并行;模块能够自由调用;模块与模块之间的通信、联系都是以全局变量为载体的。它的缺点也很明显,模块与模块间的信息传递非常随意,维护和更新困难。

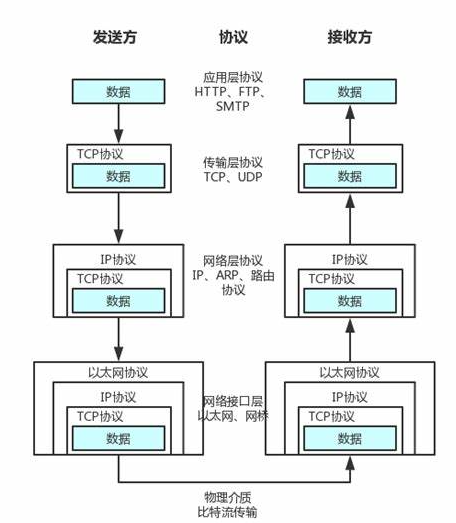

2.层次结构:层次结构的软件例子:TCP/IP协议栈。

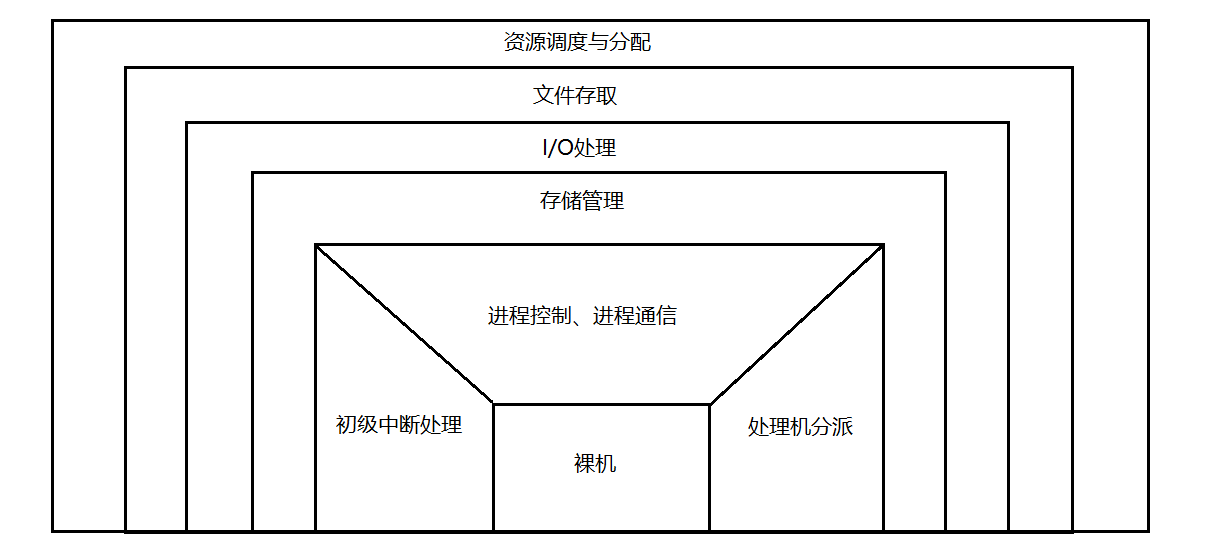

操作系统也是类似这样的结构,所有的功能模块按调用次序排成若干层,层与层之间只有相邻的单向依赖或单向调用,用户只能访问最外层,每一层都是为上一层服务的。这是层次结构的特点,也是缺点。

分层原则:与硬件相关的——最底层;具有外部特征的(能与用户互动的)——最外层;中间层——按照调用的次序或消息传递的顺序排列;共性的服务——较低层;活跃的系统功能——较低层。层次结构的优点在于结构清晰,避免了循环调用;整体问题局部化,模块与模块之间耦合度降低,系统的正确性容易被保证;有利于操作系统的维护、扩充、移植。

3.微内核结构:在微内核结构中,提出了操作系统=微内核+核外服务器的概念:

微内核是什么?微内核足够小,它仅仅提供操作系统最基本的核心功能与服务;它能够实现与硬件紧密相关的处理,实现一些较为基本的功能,还能够负责处理用户与核外服务器的交互。

什么是核外服务器?它能够完成操作系统的绝大部分服务功能(注意与微内核的差别),并且等待应用程序(用户)提出请求。核外服务器由若干服务器或进程组成,也就是说,每个服务器就是一个进程,其中包括进程服务器、线程服务器、虚拟内存服务器、设备管理服务器等等,它们都以进程的形式运行在用户态。它的优点是非常明显的:它方便用户对操作系统扩充,只需要多添加一个进程就好了;它使得操作系统更加灵活,在某些场景下可以舍弃某些服务器;它使得操作系统的可移植性更进一步。

典型的微内核操作系统便是Linux(事实上是一个单内核的操作系统,但是具有微内核特性)和Minix OS。Linux操作系统是一个单体内核操作系统,在桌面、服务器、嵌入式领域得到了广泛的应用;而Minix OS操作系统就是一个纯正的微内核结构操作系统,它主要是用于教学、科研。Linux的作者Torvalds和Minix OS的作者Andrew在1992年的Usenet讨论组上互相评价了两款操作系统(应该就是互黑吧):Torvalds评价Minix设计上存在缺陷,因为它不支持多线程,并且提出了内核本身不需要过度具备可移植性的观点;Aandrew则坦言道Linux是一款过时的操作系统,因其使用单体内核,在整体结构上是有害的,并且Linux对Intel 80386架构的耦合度太高,移植性是不够的。

思考题:

1.操作系统的微内核结构的有点对我们设计大规模的应用程序有什么启示?

操作系统的微内核结构提高了操作系统的可扩展性、增强了操作系统的可靠性以及可移植性,它也使得操作系统变得更加灵活。由此可见,在以后设计大规模的应用程序时,也需要考虑到这几个点,采用什么方式能够提高扩展性、可靠性?如何使代码可维护性、可靠性变得更高?

2.2CPU的态

操作系统必须有最基本的硬件支持,它们分别是CPU、内存、中断、时钟。

其中CPU的态指的是CPU的工作状态,以及对资源和指令的使用权限的描述。也就是说,CPU的态将会限制CPU看到的资源,限制CPU能够处理的指令。

在计算机当中,存在这样一些指令:

1)LGDT/LIDT:装载特殊寄存器

2)CLTS:清除任务开关标志

3)STI/CTI:允许和禁止中断

4)HALT:停止CPU的工作

5)IN/OUT:执行I/O操作

6)从内核态返回到用户态

......

这些指令都与计算机底层有关,所有这些指令不能够被应用程序随意使用,这些指令我们称为特权指令。只有当CPU工作在权限级别较高的态时,才能执行这些指令。

CPU态的分类:

1.内核态(Kernel mode):CPU工作在这样的态下面,能够访问计算机所有的资源和执行所有的指令;操作系统的内核就工作在CPU的内核态下面(内核代码必须在内核态执行),也就是收,CPU工作在内核态下,可以对应用程序作管理。

2.用户态(User mode):也称目态。CPU工作在这样的态下面,只能访问计算机的部分资源以及执行部分指令,用户的应用程序就是在CPU用户态下运行的。

3.管态(Supervisor mode):介于内核态和用户态之间。对于管态,操作系统并没有给出明确的界限和定义,所以我们暂且不谈它。

用户态和内核态之间的转换:

在下面的场景中,能使CPU从用户态转换到内核态:

1.用户或者应用程序请求操作系统提供某些服务

2.CPU接收到中断信号而发生中断时(中断的处理过程在内核态执行)

3.用户进程产生错误,也称内部中断

4.用户企图执行特权指令,会发出一个态的转换请求,如果成功则会切换到内核态

内核态向用户态转换的场景:通常是内核执行中断返回指令IRET。

不同的角度看待态的问题有不同的定义:硬件直接按CPU的态来区分状态;操作系统则是按进程工作在哪种态下来区分的。

Intel CPU的态:

1.Intel CPU的态分为四个,分别为Ring0、Ring1、Ring2、Ring3,其中,Ring0为最核心(CPU权限最高),Ring3为最外层(CPU权限最低)。

2.假设有用户层程序段A和操作系统(内核)层程序段B,当程序段A需要操作系统帮助A完成某个服务时,需要访问程序段B,程序段A就会检查这两个程序段的请求特权级(RPL)和描述符特权级(DPL),如果不相同则说明态不同,态不同则说明发生态的转换。

Windows中Ring0和Ring3之间的通信:

应用程序无法直接访问外部设备,所以Windows提供了一个DeviceIoControl(kernel32.dll)的接口,应用程序可以调用这个接口,这个接口的内部会有从用户态到内核态转换的指令,转换到内核态后,会把外部设备的信息写进用户提供的参数当中,从而完成一次应用程序到外部设备的访问。由此再次强调一点:用户不能够直接越过操作系统访问外部设备,所有的服务必须请求操作系统来完成。

介绍完CPU,就有必要了解以下存储器。存储器是存储程序和数据的部件,它的分类分为:

1.按存储器(半导体存储器)读写工作的方式不同划分成RAM和ROM

2.按存储元的材料可以划分为半导体存储器(通常用作主存),磁存储器(磁带、磁盘),光存储器(光盘)

3.按与CPU的联系可以划分为主存和辅存。主存是直接和CPU发生数据交换的存储器;辅存是不能直接和CPU发生数据交换的存储器

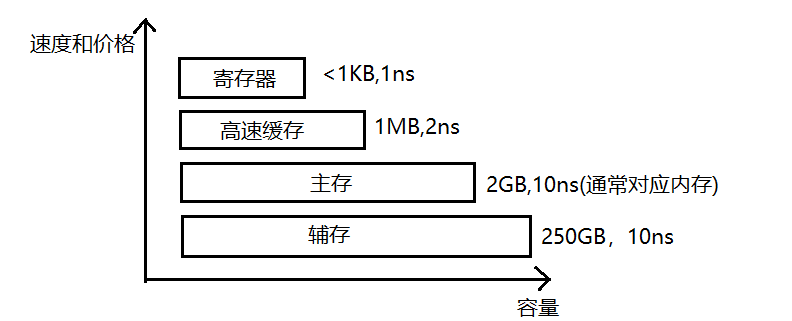

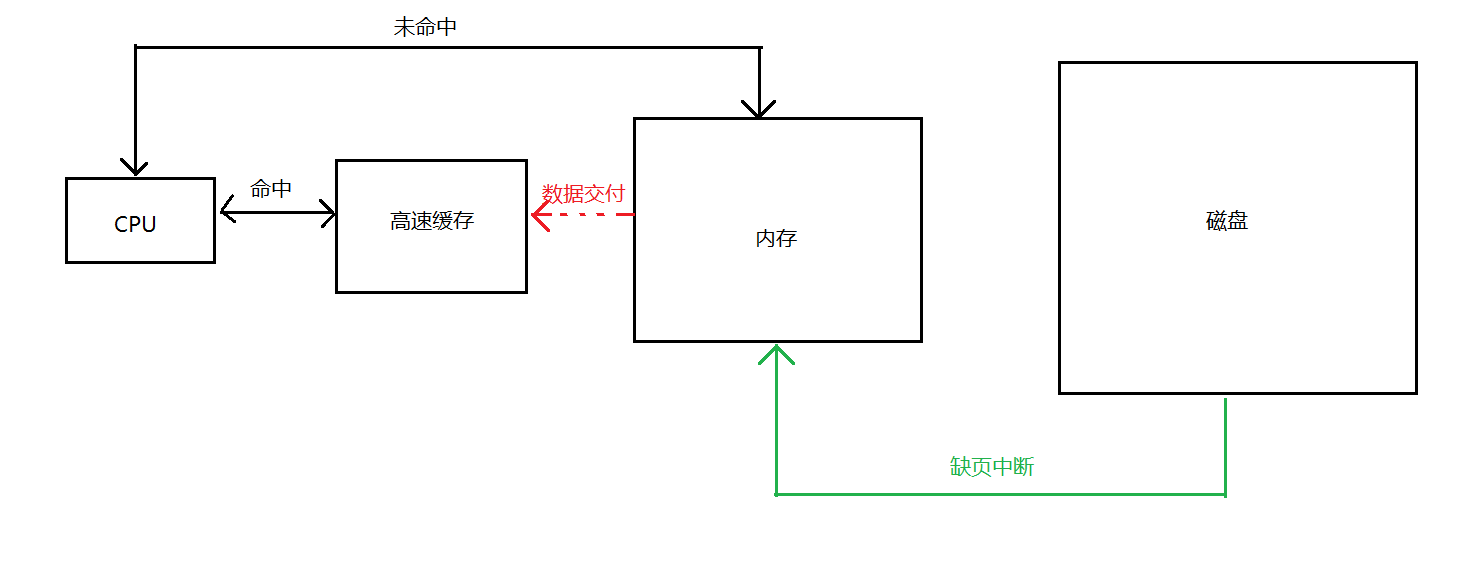

理想的存储体系是速度快、容量大、成本低。但实际上这样的要求很难达到。所以在实际当中,存储器体系往往分为多级,由寄存器、高速缓存(cache),主存、辅存一起构成存储体系。如下图所示,寄存器的容量最小,但速度最快,同时价格、成本最高;辅存(通常对应磁盘)的容量最大,但速度最慢,同时价格、成本最低。

分级存储系统的工作原理:

寄存器、高速缓存直接嵌在CPU上,所以CPU需要的数据直接从寄存器或者高速缓存中拿。但是这仅仅是理论状态,实际上并不能保证CPU每次都能从寄存器或者高速缓存当中得到数据,所以有必要了解分析存储系统的工作原理以及CPU读取指令或数据的访问顺序。

因为寄存器太小,我们这里不考虑寄存器。内存当中的数据并不是直接由CPU读取,而是交付给高速缓存,CPU再从高速缓存中读取数据,如果读取成功,我们称为缓存命中(HIT);如果读取不成功,就需要转向去内存中拿,我们称为不命中(MISS);由于虚拟内存的缘故(后期将会介绍),CPU要访问的数据可能不在内存上而在磁盘上,此时就会产生缺页中断,操作系统需要把磁盘上对应的数据加载到内存中,然后CPU再从内存读取。

思考题:

1.用户态向内核态转换有多种情形,但其本质就是一种中断情形。如何理解这句话?

无论是哪种情况使CPU发生态的转换,都会使CPU放弃当前任务而转向执行其他任务,这个过程很有可能会发生CPU态的转换。CPU的这种执行模式是符合中断的定义的。

2.3中断机制

中断的定义:

中断指的是CPU对突发的外部事件的反应过程或处理动作。

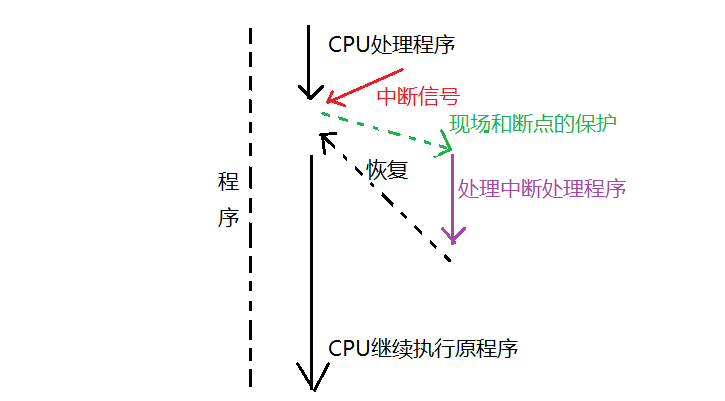

CPU收到外部信号(中断信号)后,会停止当前工作,转去处理该外部事件(中断处理程序),处理完毕后回到原来的中断处(断点)继续原来的工作。

CPU引入中断的目的:

1.实现并发活动:就像多道批处理系统一样,在宏观上看来,所有的任务都是并发执行

2.实现实时处理:对应一些优先、紧急的任务,一旦发出中断信号请求CPU处理自己时,CPU能够及时响应

3.故障自动处理:CPU收到中断信号后,有可能是因为某些模块发生了错误,这时候内核可能具备修复的代码,CPU直接可以切换到内核态执行该代码

中断的一些概念:

1.中断源:引起系统发生中断的事件称为中断源,中断源可以是软件、可以是硬件、也可以是进程本身

2.中断类型:中断类型分为强迫性中断和自愿性中断。强迫性中断指的是程序没有预期,突然收到中断信号,例如在I/O时发生错误,因为访问I/O是通过操作系统完成的,程序并不知道操作系统具体的代码;自愿中断指的是程序有预期的收到中断信号,例如程序本身就写了一个执行访管指令(通常是程序员写的)

3.中断类型还可以分为外中断和内中断:外中断又称中断,由CPU外部的事件引起,例如I/O;内中断指的是由CPU内部事件引起,例如访管中断、程序中断;外中断还分为可屏蔽中断和不可屏蔽中断:可屏蔽中断指的是中断原因并不是很严重的问题,CPU可以不响应;不可屏蔽中断指的是中断原因非常严重,CPU必须响应

4.断点:程序中断的地方,通常用将要执行的下一条指令的地址来表示,它们被放在CS、IP这个两个寄存器中

5.现场:现场指的是程序能够正确运行所依赖的信息集合,也称上下文。这些信息集合指的是和当前程序相关的寄存器和寄存器里面的内容。因为发生中断后,要回到断点处继续执行,所以断点也是程序能够正确运行的信息,所以,现场包括断点。

6.现场的两个处理过程:

1)现场的保护:CPU处理中断处理程序之前,要先把现场放入系统栈

2)现场的恢复:退出中断处理程序后,需要把现场从系统栈拿出来

中断响应过程:

1.识别中断源:搞清楚是内部中断还是外部中断;如果是外部中断,搞清楚是可屏蔽中断还是不可屏蔽中断

2.保护断点和现场:断点和现场是中断处理程序退出时,程序可以正常运行的关键,所以有必要做保护,具体就是将它们压入系统栈

3.装入中断处理程序的入口地址:把中断处理程序的入口地址装入CPU的CS、IP两个寄存器当中

4.处理中断处理程序:需要注意的是,处理的过程大部分都在内核态

5.恢复现场和断点:中断处理程序退出后,需要恢复断点和现场,保证原来程序的正确运行

6.中断返回(IRET):恢复工作做好以后,中断处理程序正式退出,CPU继续执行原来的程序

中断响应的实质(处理中断的实质):

1.交换执行指令的地址:本质就是装入不同程序的指令地址

2.交换CPU的态:处理中断程序很有可能会改变CPU的态

3.现场的保护和恢复

4.信息传递:很有可能中断处理程序是程序有意为之,目的是为了让中断处理程序给自己带一些信息回来