记:STM32F4参考手册-存储器和总线架构

STM32F4参考手册-存储器和总线架构

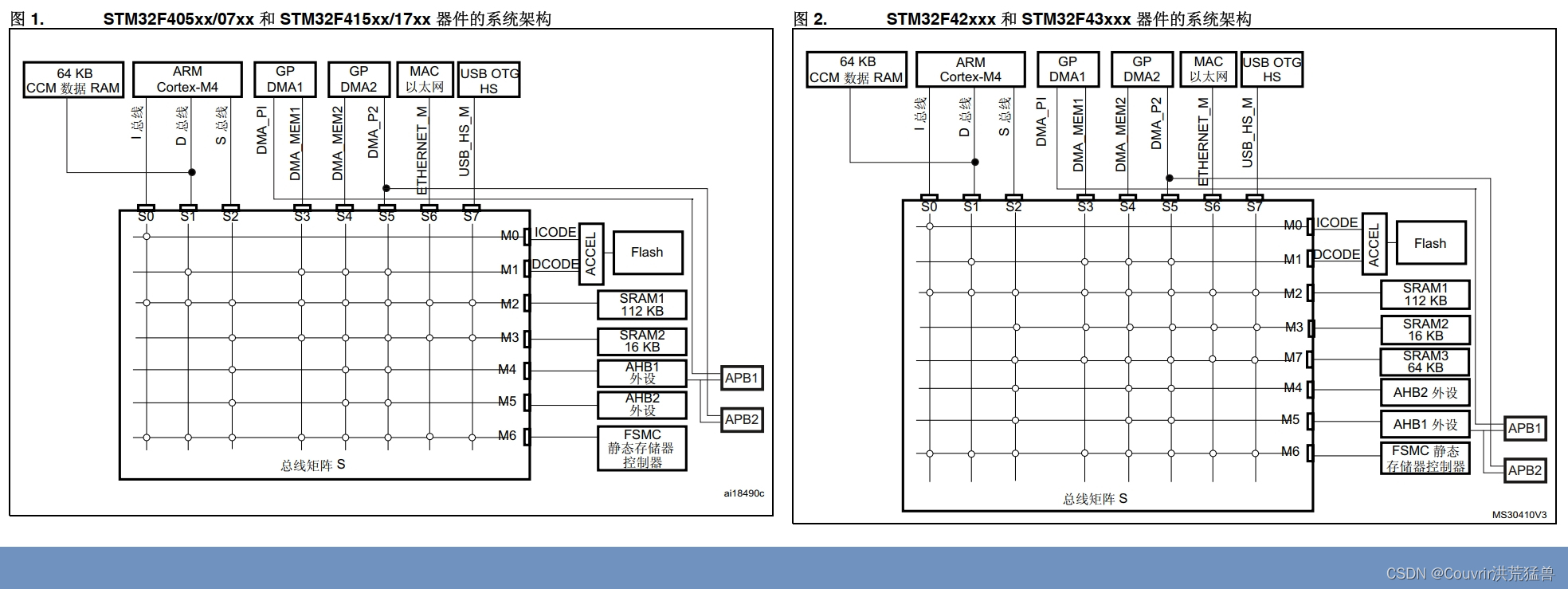

系统架构

主系统由32位多层AHB总线矩阵构成,可实现以下部分部分的互连:

八条主控总线:

Cortex-M4F内核I总线、D总线和S总线

DMA1存储器总线

DMA2存储器总线

DMA2外设总线

以太网DMA总线

USB OTG HS DMA总线

七条被控总线:

内部Flash ICode总线

内部Flash DCode总线

主要部分SRAM1(112KB)

主要部分SRAM2(16KB)

主要部分SRAM2(64KB)(仅适用于STM32F42xxx和STM32F43xxx器件)

AHB1外设(包括AHB-APB总线桥和APB外设)

AHB2外设

FSMC

借助总线矩阵,可以实现主控总线到被控总线的访问,这样即使在多个高速外设同时运行期间,系统也可以实现并发访问和高效运行。

总线矩阵:用于主控总线间的访问总裁管理。仲裁采用循环调度算法。

Tips:图中显示,64KB的CCM数据RAM(内核耦合存储器)不属于总线矩阵,只能通过CPU对其进行访问。

S0--I总线:

用于将Cortex-M4F内核的指令总线连接到总线矩阵。内核通过此总线获取指令。

此总线访问的对象是包含代码的存储器(内部Flash/SRAM或通过FSMC的外部存储器)。

S1--D总线:

用于将Cortex-M4F内核的数据总线连接到总线矩阵。此总线用于访问位于外设或SRAM中的数据,也可通过此总线获取指令(效率低于ICode总线)。

此总线访问的对象是内部SRAM、APB1外设、APB2外设以及通过FSMC的外部存储器。

S2--S总线:

用于将Cortex-M4F内核的系统总线连接到总线矩阵。此总线用于访问位于外设或SRAM中的数据,也可通过此总线获取指令(效率低于ICode总线)。

此总线访问的对象是内部SRAM、APB1外设、APB2外设以及通过FSMC的外部存储器。

S3、S4--DMA存储器总线:

用于将DMA存储器总线主接口连接到总线矩阵。DMA通过此总线来执行存储器数据的传入和传出。

此总线访问的对象是内部SRAM以及通过FSMC的外部存储器。

S5--DMA外设总线:

用于将DMA外设主总线接口连接到总线矩阵。DMA通过此总线访问AHB外设或执行存储器间的数据传输。

此总线访问的对象是内部SRAM、AHB外设、APB1外设、APB2外设以及通过FSMC的外部存储器。

S6--以太网DMA总线:

用于将以太网DMA主总线接口连接到总线矩阵。以太网DMA通过此总线向存储器存取数据。

此总线访问的对象是内部SRAM以及通过FSMC的外部存储器。

S7--USB OTG HS DMA总线:

用于将USB OTG HS DMA主总线接口连接到总线矩阵。USB OTG HS DMA通过此总线向存储器加载/存储数据。

此总线访问的对象是内部SRAM以及通过FSMC的外部存储器。

AHB/APB总线桥(APB):

借助两个AHB/APB总线桥,可在AHB总线与两个APB总线之间实现完全同步的连接,从而灵活选择外设频率。

每次芯片复位后,所有外设时钟都将关闭(SRAM和Flash接口除外)。使用外设前,必须在RCC_AHBxENR或RCC_APPBxENR寄存器中使能其时钟。

Tips:对APB寄存器执行16位或8位访问时,该访问将转换为32位访问(总线桥将16位或8位数据复制后提供给32位向量)。

存储器组织结构

程序存储器、数据存储器、寄存器和I/O端口排列在同一顺序的4GB地址空间内。

各字节按小端格式在存储器中编码。字中编号最低的字节被视为该字的最低有效字节,而编号最高的字节被视为最高有效字节。

可寻址的存储空间分为8个主要块,每个块为512MB。

未分配给片上存储器和外设的所有存储区域均视为保留区。