【微机原理与单片机接口技术】MCS-51单片机的引脚功能介绍

前言

MCS-51是指由美国Intel公司生产的一系列单片机的总称。MCS-51系列单片机型号有很多,按功能分位基本型和增强型两大类,分别称为8051系列单片机和8052系列单片机,两者以芯片型号中的末位数字区分,1为基本型,2为增强型。增强型单片机与基本型单片机相比,其最显著的特点是单片机内部的数据存储器和程序存储器的容量更大,同时增加了一个定时/计数器。

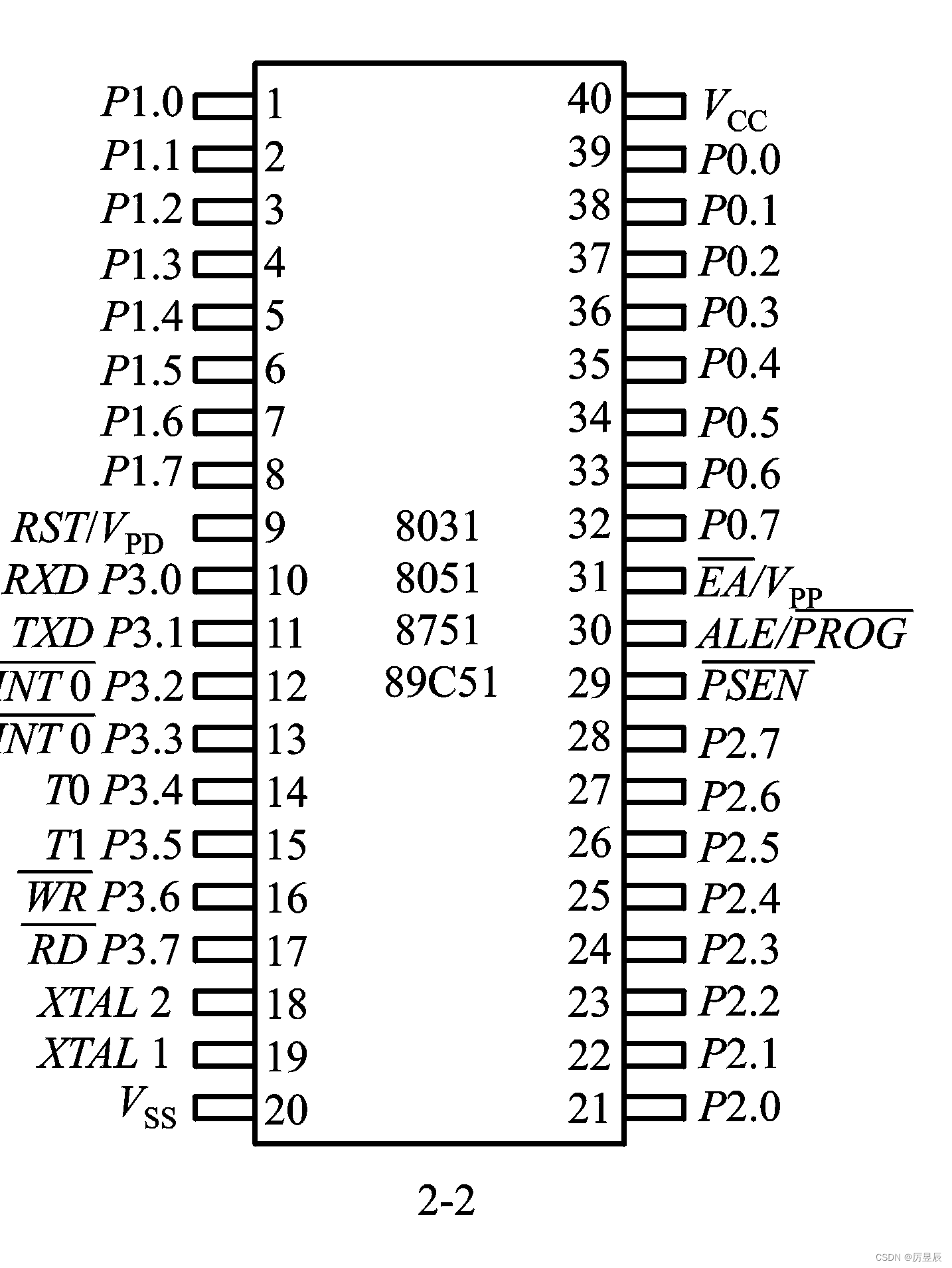

单片机是将CPU、存储器和输入/输出单元(I/O)等集成在一块硅片上,把电路上的引脚用导线接引到封装基座的引脚上,以便与其他器件连接。封装的主要功能是保护芯片和便于焊接安装等。MCS-51系列中各种型号单片机的引脚是相互兼容的。

如图所示的PDIP封装,共有 40 只引脚,根据引脚用途可分为4大类,分别是电源引脚、时钟引脚、控制引脚和 I/O 引脚。下面对引脚定义及其功能进行说明。

1.电源引脚

电源引脚用于外接单片机的工作电源。

(1)Vcc(40脚):单片机工作电源电压输入脚。不同型号单片机接入对应的电压电源。单片机芯片的推荐工作电压及电压范围在芯片用户手册中给出,注意在实际应用中务必严格遵守。

(2)GND(20脚):必须接地。

2.时钟引脚

XTAL1(19脚)为片内振荡电路的输入端,XTAL2(18脚)为片内振荡电路的输出端。

51单片机的 CPU 时钟可由以下两种方式提供。

(1)内部时钟方式:在XTAL1和XTAL2引脚外接一个石英品体或陶瓷晶振和振荡电容,如图所示。

振荡电容通常取10~30pF,石英晶体的频率为0.5~24MHZ,典型值为6MHz、I2MHZ和11.0592MHZ。在石英晶体起振后,XTAL2引脚输出一个2.24V左右的正弦波,XTAL1对地电压约为2.09V。51单片机片内的时钟和石英晶体的自激振荡频率相同,为保证振荡电路的稳定性及快速要求在设计电路板时,晶振和电容应尽量靠近单片机芯片,以减小分布电容对振荡电路的影响。

(2)外部时钟方式:使用外部振荡器脉冲信号,外部CMOS时钟源直接接到XTAL1引脚,XIAL2悬空,如图所示。

3、控制引脚

(1)复位引脚RST(9脚)

RST 为单片机复位输入端,高电平有效。当单片机运行时,若RST引脚输入大于两个机器周期(24个振荡周期)以上的高电平,则触发单片机复位操作,初始化单片机,使单片机重新运行程序,即从序存储器的 0000H 地址单元开始执行指令。

(2)(29脚)

引脚为外部程序存储器读选通信号,低电平有效。当单片机读取外部程序存储器上的数据或指令时,该引脚输出一个负脉冲用于选通外部程序存储器,否则一直输出高电平。外扩ROM 时,

引脚连接到外部ROM的

引脚。

(3)(30脚)

为双功能引脚。ALE为地址锁存允许输出端。当单片机访问外部存储器时,ALE引脚输出一个由正向负的负跳沿作为地址锁存信号,用于控制片外的地址锁存器锁存低8位的访问地址。访网地址为16位,低8位由P0口输出,高8位由P2口输出,由于P0口分时复用为低8位地址线8 位数据输入/输出,因此必须将地址低8位锁存起来。

为第二功能引脚。在对片内EPROM型单片机(如8751)烧写程序时,该引脚作为编程负脉冲输入端。

除上述两种情况外,该引脚自动输出固定频率的脉冲信号,频率为单片机时钟振荡频率的1/6,可用做外部时钟源或定时计数脉冲。

(4)(31脚)

为双功能引脚。

引脚为内部程序存储器和外部程序存储器的选择控制端。当

端接高电平(Vcc)时,单片机访间内部程序存储器,即运行内部程序存储器(地址范围为0000H~0FFFH)中的程序,但在程序计数器PC的值超过0FFFH(访问地址超过4KB)时,则自动转到外部程序存储器执行程序。当

端接低电平(GND)时,则只访问外部程序存储器,不管此时是否存在内部程序存储器。对于内部无ROM的8031单片机,程序存储器需外接,则

引脚必须接地(低电平)。

Vpp为第二功能引脚,为片内EPROM或Flash存储器的编程电压输入端,对内部有EPROM的8751单片机,编程电压的21V;对片内为Flash存储器的51单片机,编程电压为12V。

4.I/O引脚

MCS-51单片机一共有32条输入/输出I/O引脚,由4个8位的并行接口P0、P1、P2和P3组成,每组并口有8位输入/输出接口,命名为Px.0~Px.7(x=0~3)。每个 I/O引脚都可以独立设置为输入或输出引脚。单片机内部设有对应的特殊功能寄存器P0~P3用于控制或读取并口状态,这些寄存器为直接字节寻址,且都支持按位寻址,即支持独立控制或读取某个I/O端口的状态。

(1)P0.0~P0.7(32~39 脚)

本组的8个引脚组成P0口,其中P0.0为最低位,P0.7为最高位。P0口为8位的双向三态口,由两个MOS串接,采用漏极开路输出。P0口可作为通用输入/输出端口,当单片机访问外部存储器或扩

展I/O时,分时复用为16位地址总线的低8位和8位数据总线。

注意,P0口作为地址总线和数据总线时,引脚外部无须外接上拉电阻,但作为通用输入/输出端口时,由于P0口每个I/O引脚内部电路为漏极开路的,无高电平输出能力,因此在引脚外必须接上拉电阻,P0口的引脚带负载能力为8个TTL负载。

(2)P1.0~P1.7(1~8脚)

本组的8个引脚组成P1口,其中P1.0为最低位,P1.7为最高位。P1口为8位准双向I/O口,内置上拉电阻。P1口用做普通输入/输出端口,每个P1口的引脚能驱动4个TTL负载。

(3)P2口(21~28 脚)

本组的8个引脚组成P2口,其中P2.0为最低位,P2.7为最高位。P2口为8位准双向I/O口,内置上拉电阻。P2 可用做通用输入/输出端口,每个P2口的引脚能驱动4个 TTL 负载。当单片机访问外部存储器时,作为16位地址总线的高8位。如果外接的数据存储器(RAM)小于256B,则可以使用字节寻址(Ri间接寻址),此时只使用低8位地址线(P0),P2可作为普通输入输出端口。如果外接的数据存储器大于256B或外接程序存储器,则必须采用字寻址方式,P2作为高8位地址线,P0作为低8位地址线。

(4)P3口(10~17脚)

本组的8个引脚组成P3口,其中P3.0为最低位,P3.7为最高位。P3口为8位准双向I/O口,内置上拉电阻,每个P3口的引脚能驱动4个TTL负载。P3 口除可用做普通输入/输出端口外,还具有第二功能,如表所示。

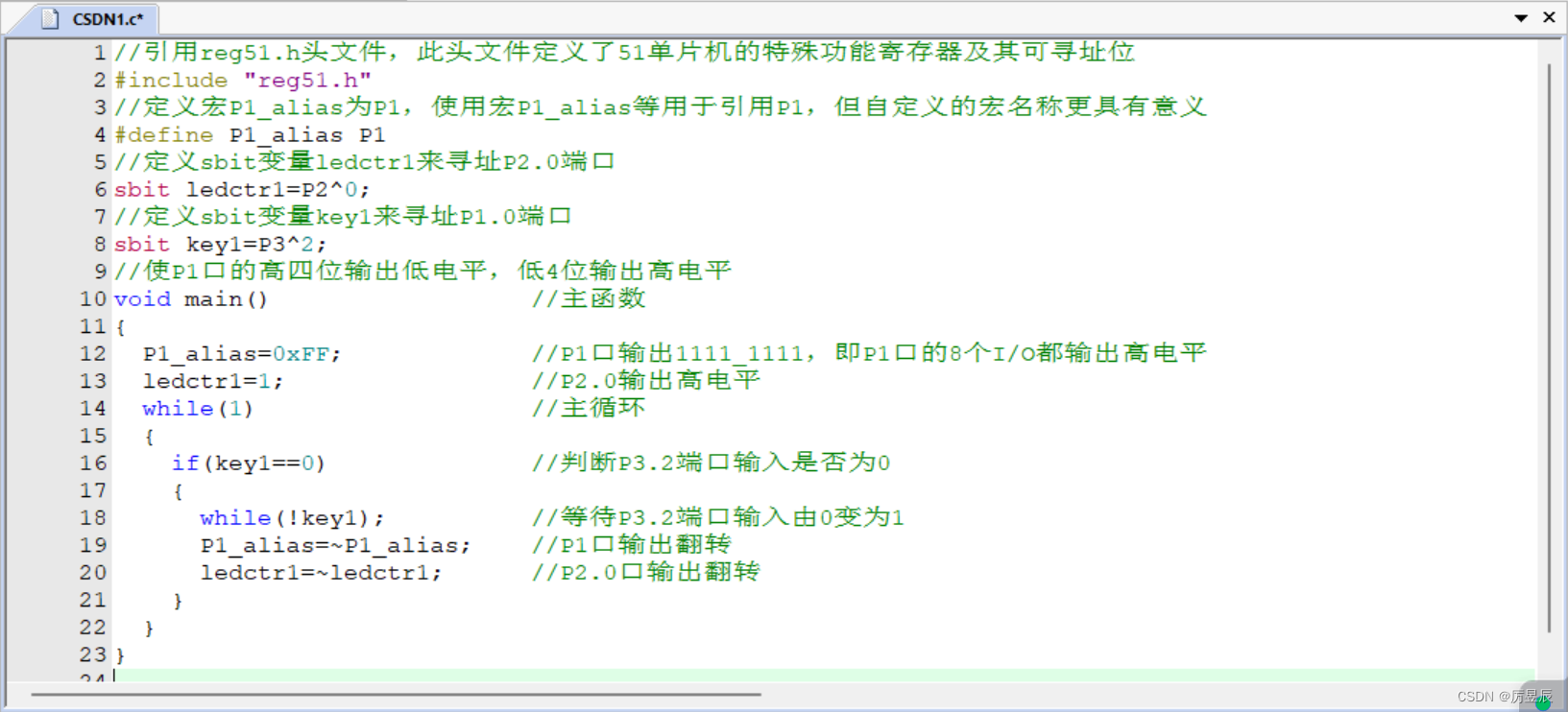

【例1】 I/O端口操作示例(汇编语言)。

- P1口输出0000_1111,即P1.7~P1.4输出低电平,P1.3~P1.0输出高电平。

MOV P1, #0F H- 置P2.0为1,即P2.0输出高电平。

SETB P2.0- 清P2.1为0。

CLR P2.1- 翻转P3.0输出,即高电平变为低电平,低电平变为高电平。

CPL P3.0- 判断P1.0输入,如果为高电平('1'),则等待(跳转到本指令),否则继续执行后续指令。

JB P1.0, $- 判断P1.1输入,如果为低电平('0'),则等待(跳转到本指令),否则继续执行后续指令。

JNB P1.1, $【例2】I/O端口操作示例(C51)。