基于dsp+fpga+AD+ENDAC的半导体运动台高速数据采集电路仿真设计(四)

整个调试验证与仿真分析分三个步骤:第一步是进行

PCB

检查及电气特性测试,主

要用来验证硬件设计是否正常工作;第二步进行各子模块功能测试,包括高速光纤串行

通信的稳定性与可靠性测试,

A/D

及

D/A

转换特性测试,

EnDat

串行通信相关时序测试

与验证等,主要用来验证

FPGA

软件内核是否正常工作以及符合预期设计要求;第三步

进行系统联合测试验证,主要包括

DSP

系统对远程伺服控制分系统控制命令数据的发,

以及对

EnDat

远程位置数据、增量式位置数据、各数字或模拟传感器的远程数据请求及

验证。

5.1

调试与验证仿真平台

为了对整个系统进行验证测试,需搭建相应的调试与仿真验证平台。调试与仿真验

证平台主要包括硬件平台、软件开发环境、仿真调试工具三大部分:

1.

硬件平台:

DSP

主系统控制板卡、传感数据采集板卡、伺服控制及位置数据控制

卡、

PC

机。

2.

软件开发环境:

CCS3.3

、

Quartus II 11.1

及其

SignalTap II

在线逻辑分析仪、

Modelsim

SE

、

Matlab

等。

3.

测试工具:安捷伦

MSO7032A

示波器(带宽

350Mhz

、采样率

2Gps

)、

DSP

仿真

器(

XDS510

)、

FPGA

下载仿真器

(USB-Blaster)

、安捷伦

34401A

万用表(六位半)、信

号发生器、直流电源、

3

米

62.5/125um

的

SC-SC

接口多模光纤线缆等。

5.2

系统子模块功能仿真

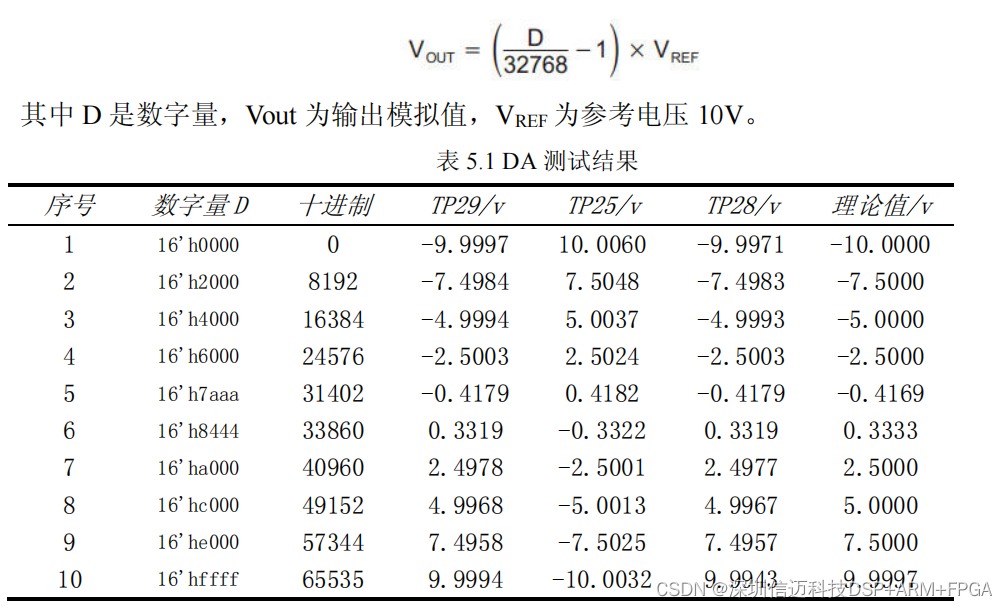

5.2.1 模数 D/A 数模 A/D 子模块验证

验证方法:采用由

FPGA

主动产生一系列递增的数字量,然后送给

DA

模块进行转

换,得到对应的模拟电压信号。测试点选择第三章中图

3.15

中的

TP28

点及其后端差分

后的

TP29

、

TP25

测试点进行。输入值为

16'H0000---16'HFFFF

之间的一些值,输出值

为对应测试点的电压值,数字与模拟值之间的对应关系为:

表格

5.1

为按照上述验证方法,采用安捷伦

34401A

万用表测得的实验数据,然后

再计算测量值与真实值之间的误差,结果如表

5.2

所示:

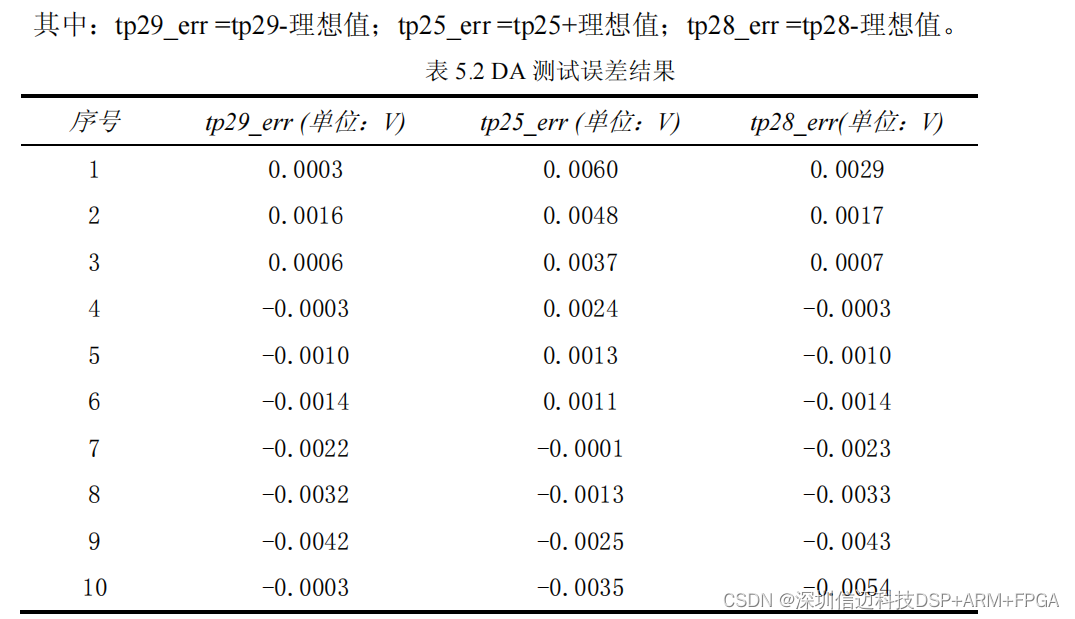

根据表格

5.2

测得的误差数据进行散点作图,得到图

5.1

所示的误差散点示意图。

据图显示,

DA

最大误差值在

0.006

左右,达到设计要求的

13

位精度,满足了设计预期。

数模

A/D

子模块的验证方法与之类似,在此不再详细介绍。

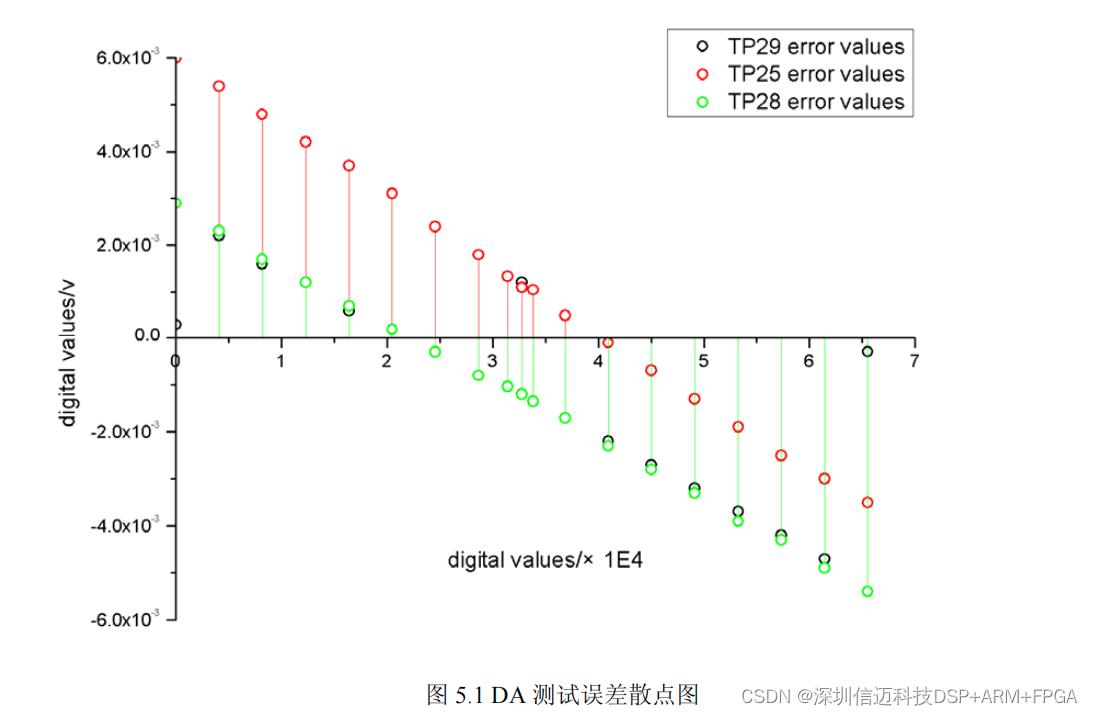

5.2.2 EnDat 子模块的验证

验证方法:采用

SignalTap II

在线逻辑分析仪对不同模式指令下的传输时序进行探

测,然后与

EnDat

规范相比较,从而确定本文中第四章中

EnDat

双向串行通信协议内核

的设计是否能够正常工作。本次使用

EnDat2.2

版本的多圈旋转编码器进行验证,其中

编码器主要参数是单圈

13

位,多圈

12

位。

图

5.2

为

EnDat

双向串行通信协议内核向编码器发送模式指令:编码器传送位置值,

对应的模式指令码为

000111

。编码器计算位置值后向

EnDat 内核发送位置值,其时序与

第四章中介绍的

EnDat

传输位置值时序规范完全符合,其中单圈数值为

6735

,多圈数

值为

1580

。

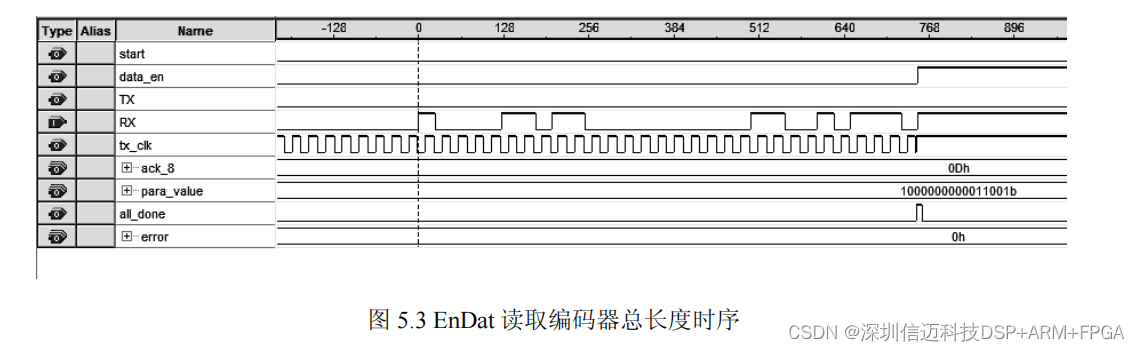

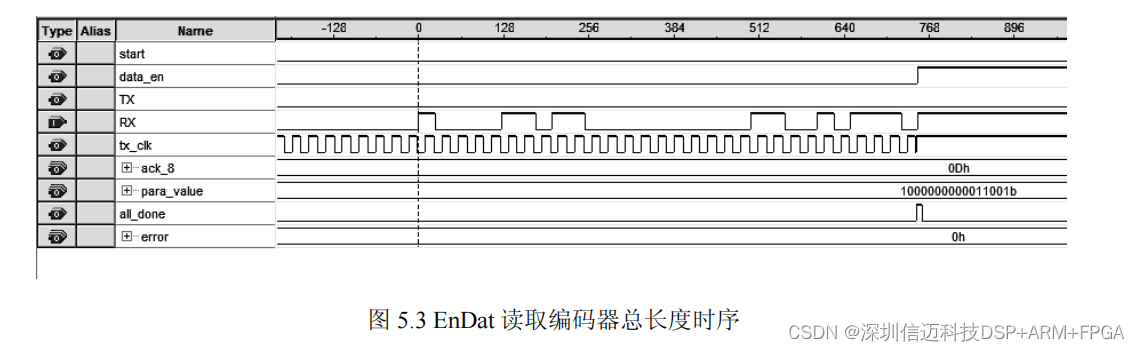

5.3

为

EnDat

内核向编码器发送读取参数模式指令,模式指令码为

100011

。

EnDat

内核接收到的串行数据为

1000000000011001

。根据

EnDat

规范,最高位保留读始终为高

电平,低

6

位用于指示编码器的总长度,因此

11001

表示该编码器为

25

位。

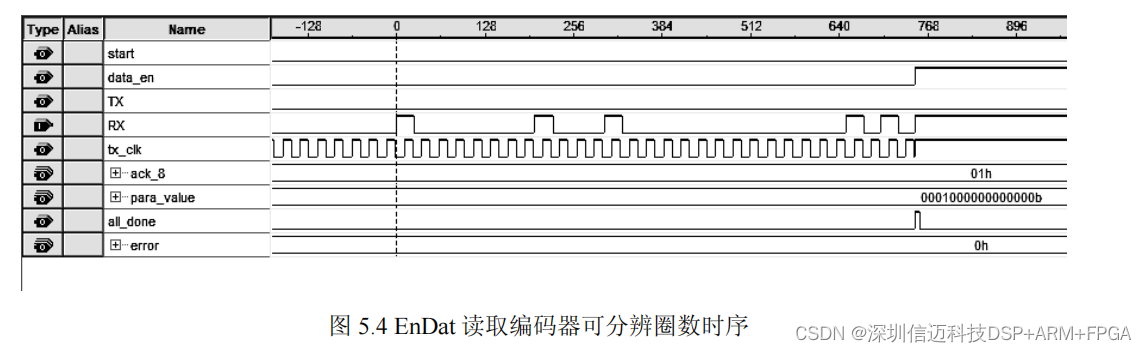

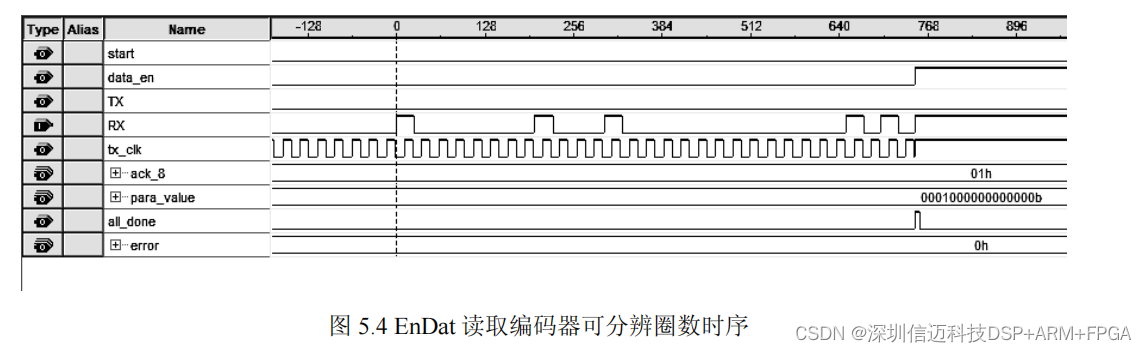

图

5.4

为

EnDat

内核向编码器发送读取参数模式指令,模式指令码为

100011

。

EnDat

内核接收到的串行数据为

0001000000000000

。根据

EnDat

规范,

16

位的数据代表编码

器可以区分的圈数,即多圈数目,因此(

1000

)

h

表示该编码器为

4096

即

12

位。

从测试的结果可以看出与之前已知的编码器参数完全吻合。

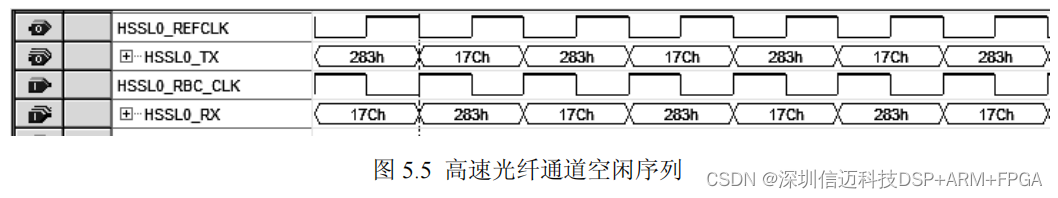

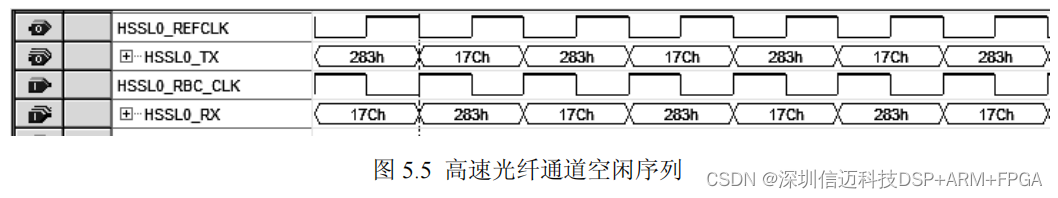

5.2.3 高速串行通信子模块的验证

验证方法:采用

SignalTap II

在线逻辑分析仪对高速串行通信内核的传输时序进行

探测,从而确定本文第四章中所设计的高速串行光纤通信内核的设计是否正常工作。在

图

4.16

和图

4.17

所示的发送控制器及接受控制器的空闲状态时,为了提供足够的信道

跳变密度,同时保证接收端的时钟相位的同步,协议内核中采用了

8B/10B

高速编码方

案中的特殊字符

K28.5

,用来调整字对齐,保证接收时钟的相位同步,同时提供

50%

的

跳变密度。根据上文中

8B/10B

编码方案及表格

4.1

,

K28.5

对应的十位的传输字符二进

制表示分别是

0101111100

和

1010000011

,即十六进制的

17C

和

283

,其中

j

为最高位,

a

为最低位,测试结果如图

5.5

所示。

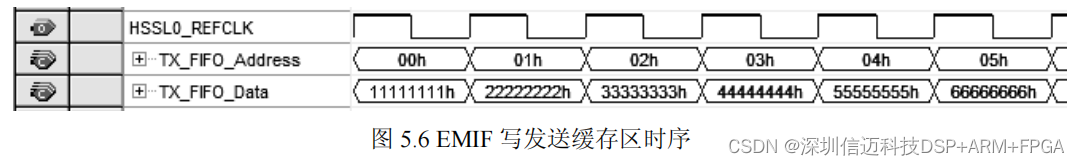

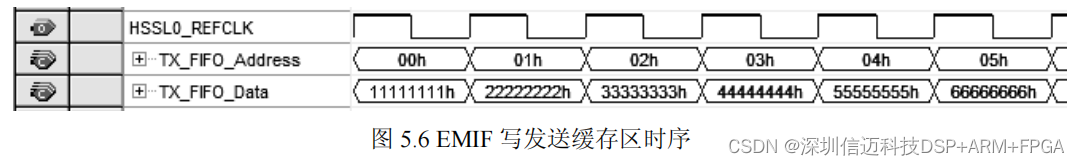

为了进行数据传输,首先要写发送缓存区,即双口

RAM

。为了测试方便简单,本

次只写十六进制的

11111111, 22222222, 33333333, 44444444, 55555555, 66666666

这六个

32

位的数据,测试结果如图

5.6

所示。

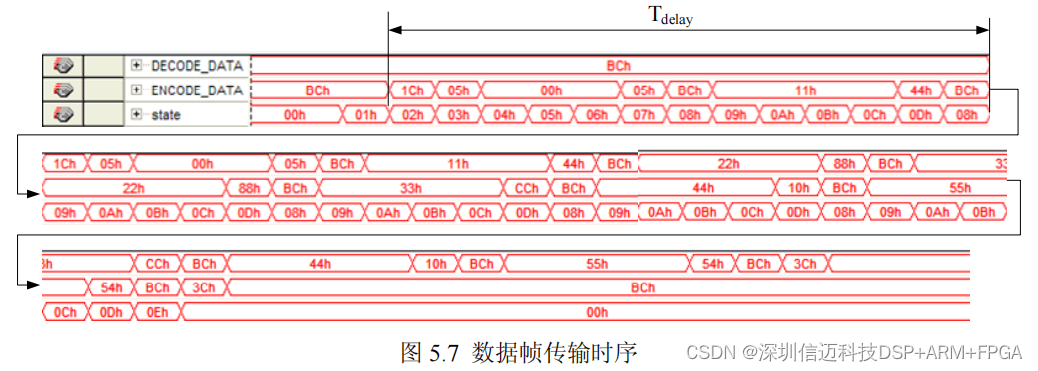

存储在如图

4.15

发送缓存区的数据

,

按照如图

4.14

所示的数据帧的格式传输到接收

端。其中数据长度配置为

5

,基地址配置为

0x00

。因此十六进制的

11111111, 22222222,

33333333, 44444444, 55555555

按顺序被传输到接收端,而

66666666

则被忽略,因为数

据长度为

5

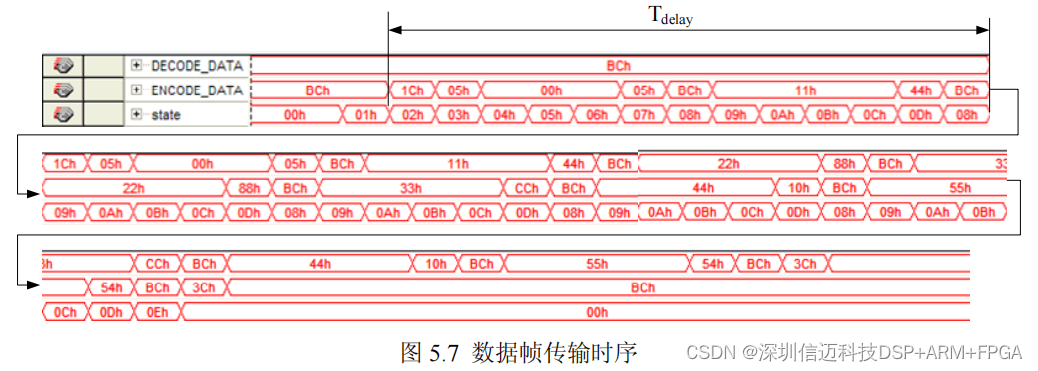

。在图

5.7

中,

ENCODE_DATA

为某发送端编码前的

8

位数据,而

DECODE_DATA

是另外通信模块的接收端译码之后的

8

位数据。测试中采用的是同一

块板卡上面的两个不同的高速串行通信模块,即模块

A

的发送端与模块

B

的接收端进

行通信连接。

T

delay

定义为在数据帧的传输过程中发送端与接收端的信道延迟时间。该参数只跟高

速串行通信模型有关,并不受应用层的控制,因此可以保证精确的控制。

测试结果如图

5.7

所示,从中可以明确地看到数据在状态机的控制下按照图

4.14

的

数据帧格式进行传输,测试结果表明,数据传输正确,且长时间测试无误码产生,传输

稳定可靠。

5.3

系统测试与验证

系统级的测试与验证,采用应用层

DSP

主系统对系统的各个子模块进行功能验证

与分析,以判断应用层能否对各功能模块进行长时间无错误的信息采集及数据下发任

务,确保整个系统的可靠运行。值得庆幸的是

CCS

提供了一个信号分析工具

Graph

图

形窗口,使用户能够精确的监测信号数据,是数据采集分析强有力的工具。

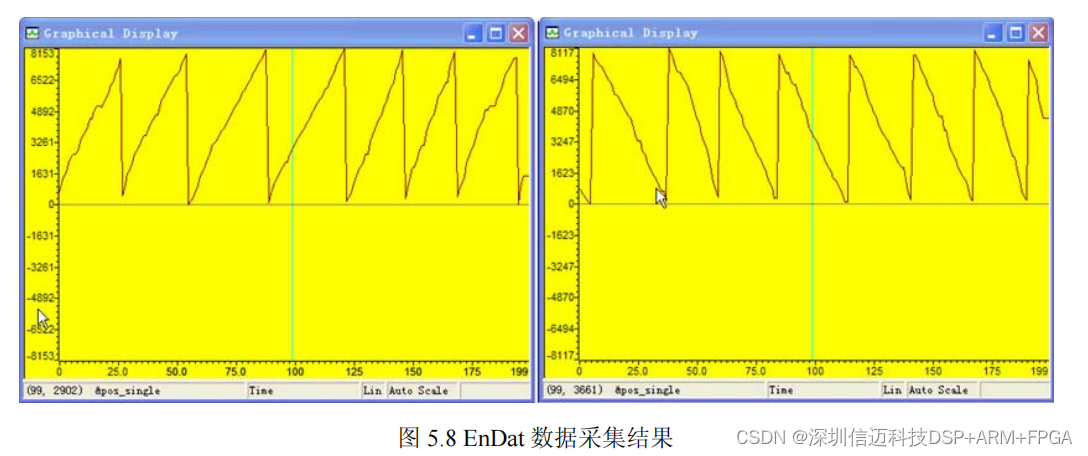

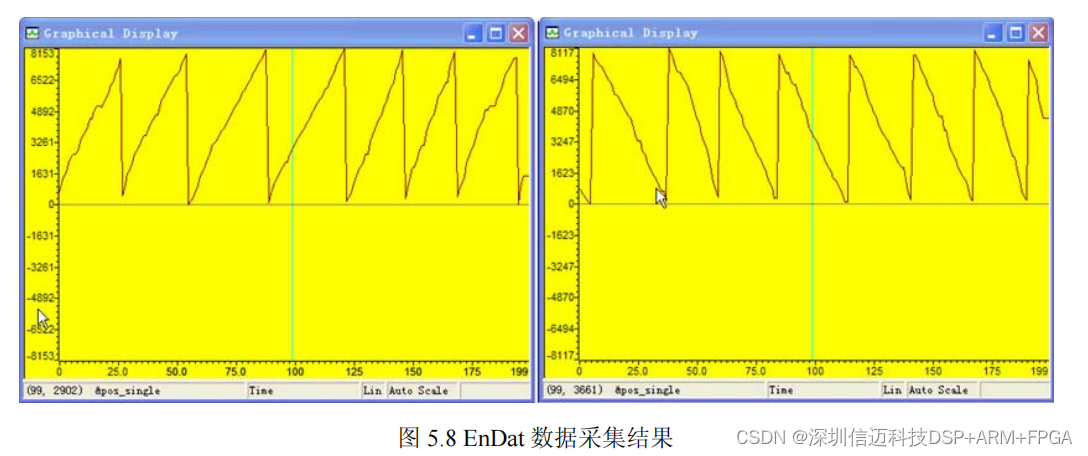

5.3.1 系统对 EnDat 数据采集的验证

验证方法:采用

CCS

信号分析工具

Graph

图形窗口,将

EnDat

数据值实时显示作

图,其中使用

EnDat2.2

版本的多圈旋转编码器,其单圈

13

位,多圈

12

位,采用手动

选择的方式。图

5.8

中左侧为顺时针旋转时的数据波形,右侧为逆时针旋转时的数据波

形,从中可以看出单圈位置值有规律的从

0

逐渐增大到最大值

2

13

即

8192

,然后又回到

0

,如此重复;由于采用手动旋转的方式,多圈位置值没有进行截图。单圈位置数据的

测试结果如图

5.8

所示。

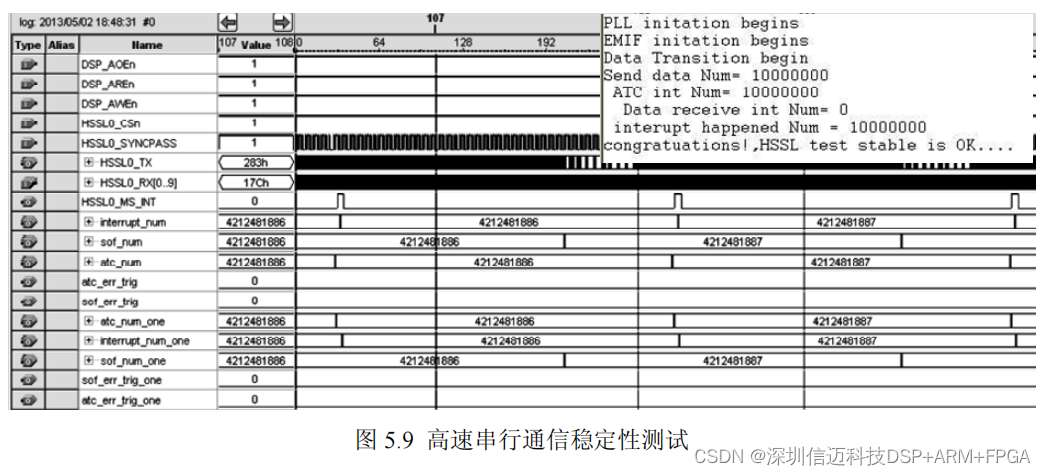

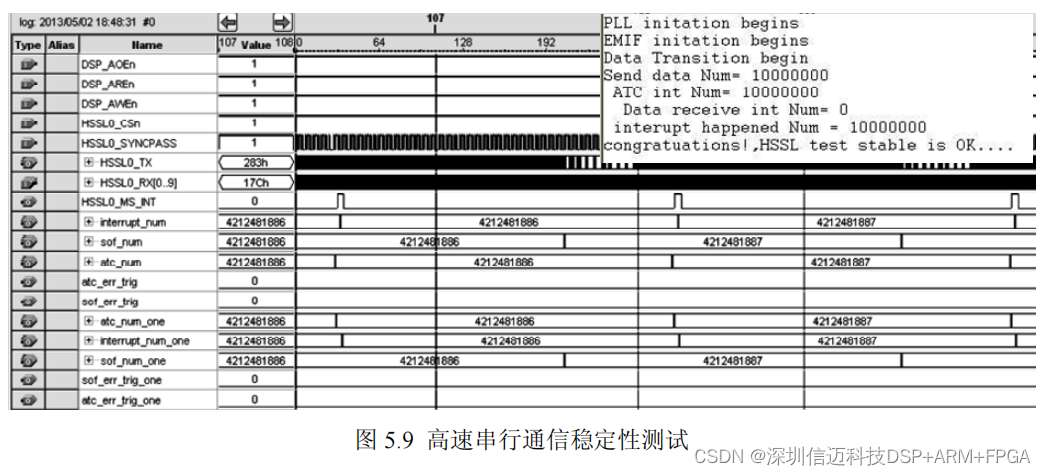

5.3.2 系统高速串行光纤通信可靠性验证

验证方法:采用

SignalTap II

在线逻辑分析仪和

CCS 集成开发环境对高速串行光纤

通信进行长时间的测试,以判断通信的可靠性。

根据高速串行光纤通信协议,

DSP

主系统发送一帧数据,目标板会应答一次,如果

中断使能则应答中断产生一次。因此,发送数目、

atc

应答数目、中断数目,三个数值

应当相等即

Send Data Num

、

ATC int Num

、

interput happened Num

三个变量数值相等,

且等于测试帧数目,同时数据接收中断

Data received int Num

数目为零;说明光纤通信

正常,否则异常。测试结果如图

5.9

所示,

CCS

的打印窗口表明,一千万次的可靠性测

试中

Send Data Num

、

ATC int Num

、

interput happened Num

三个变量数值均为一千万次,

Data received int Num

为

0

,无错误产生,系统高速串行光纤通信可靠性很高,完全满足

本课题需求。

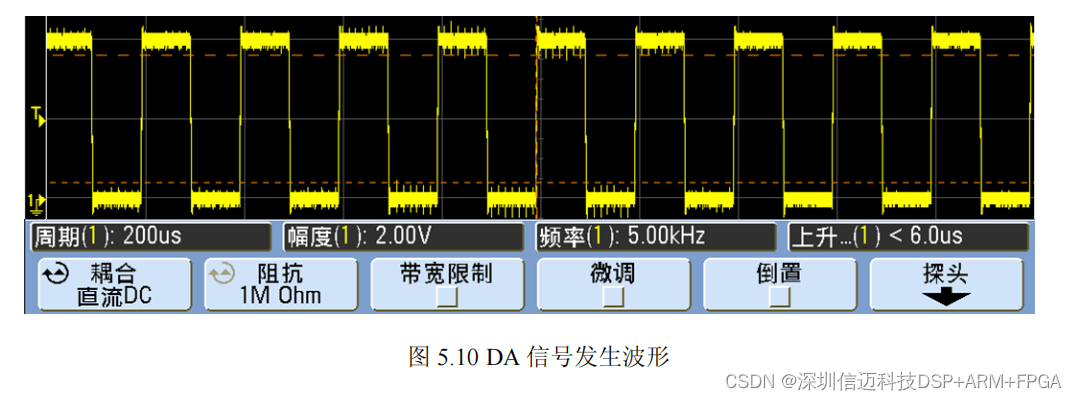

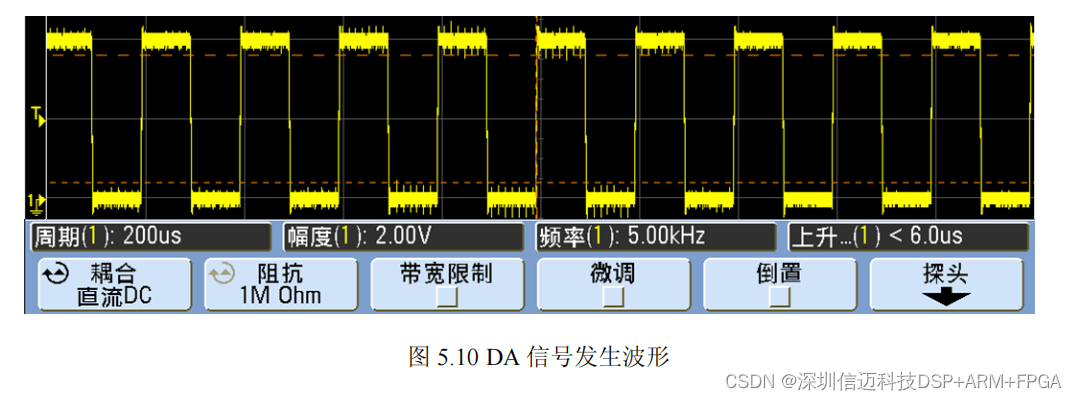

5.3.3 系统对 DA 控制输出的验证

验证方法:采用示波器对

DSP

主系统下发的

DA

控制数据进行显示,以判断应用层

对

DA

控制的正确性。

测试采用

DSP

的定时器中断产生

200us

的中断周期,模拟

200us

的伺服周期内分别

对

DA

部分下发数据

0x0000

、

0x9999

两个数字量。根据前面的硬件设计,

DA

输出的模

拟电压信号应为

0V

、

1.99999V

两个电压值,周期为

200us

的方波。图

5.10

所示为示波

器测试结果

,

从中可以看出实际输出与理论输出完全一致,由于测试中采用的是开关电

源,存在开关噪声,因此测得的模拟电压信号毛刺较大。

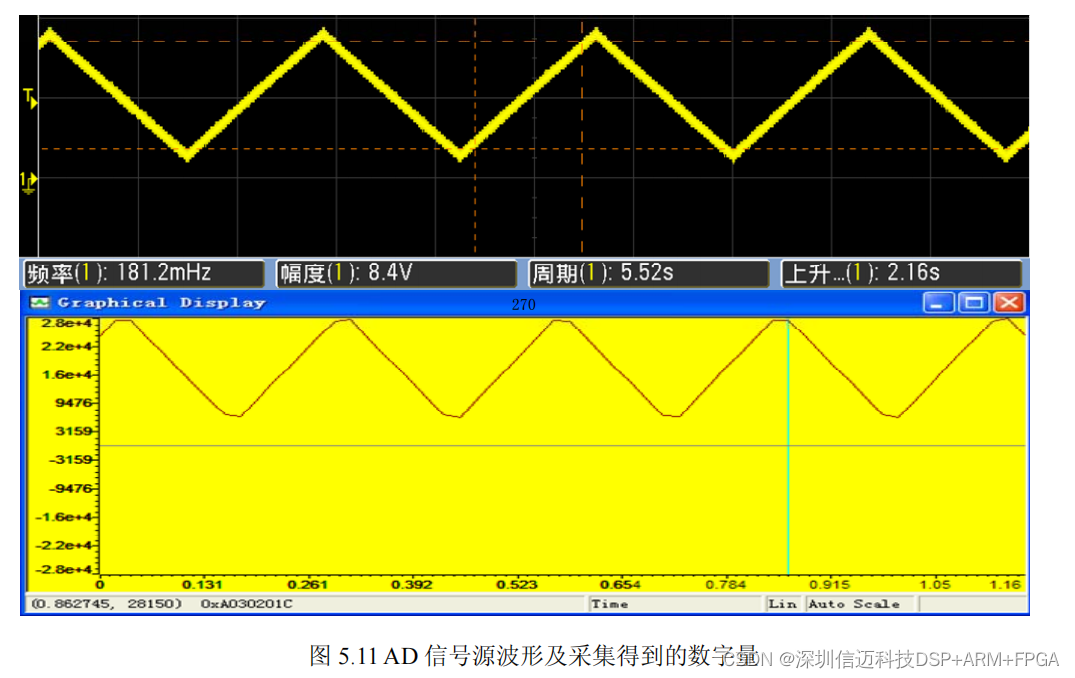

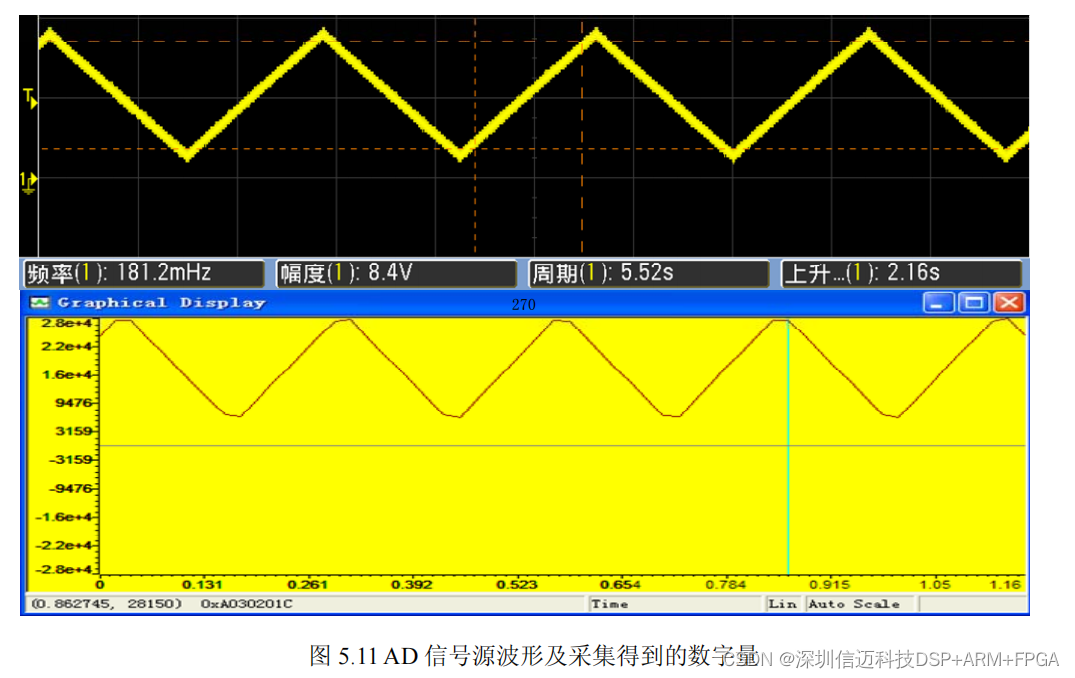

5.3.4 系统对 AD 信号采集的验证

验证方法:采用信号发生器为

AD

输入端提供模拟传感器信号,采用

CCS

信号分

析工具

Graph

图形窗口对采集的

AD

数字量实时作图显示,以判断应用层对

AD

信号采

集的正确性。

图

5.11

是测试结果,上面为信号发生器提供的模拟电压信号

,

下图为

Graph

图形窗

口对

AD

数字量的作图显示。从中可以看出,模拟电压信号与转化的数字量完全与理论

值相符合。

5.3.5 系统对 EMIF 的可靠性验证

验证方法:采用

CCS

集成开发环境,变量观察窗口及存储区查看窗口,对通过

EMIF

异步访问的发送及接收缓存区即双口

RAM

读写操作长时间测试,以判断

EMIF

读写通

信接口的可靠性。

EMIF

异步接口中,读、写都需要配置建立、选通、保持三个参数,为了缩短读写

话费的时间,尽可能设置的小,但过小的设置参数可能会影响读写操作的可靠性,因此

对

EMIF 读写通信接口的可靠性验证是必须的。

图

5.12

所示,通过

EMIF

异步接口对高速串行光纤通信内核的发送缓存区写一系列

递增的数据,然后再读取发送缓存区,将读到的数据与之前写入的数据进行一一比较,

就可以判断本次读写操作是否正确。测试结果显示,对缓存区即双口

RAM

的

255

个长

字即

1KB

的存储区进行了十万次的读写重复性测试,错误指示变量

ERROR

的值为零,

存储区查看窗口

memory window

显示了最后一次读写操作之后缓存区中存储的数据,

结果表明测试无误。

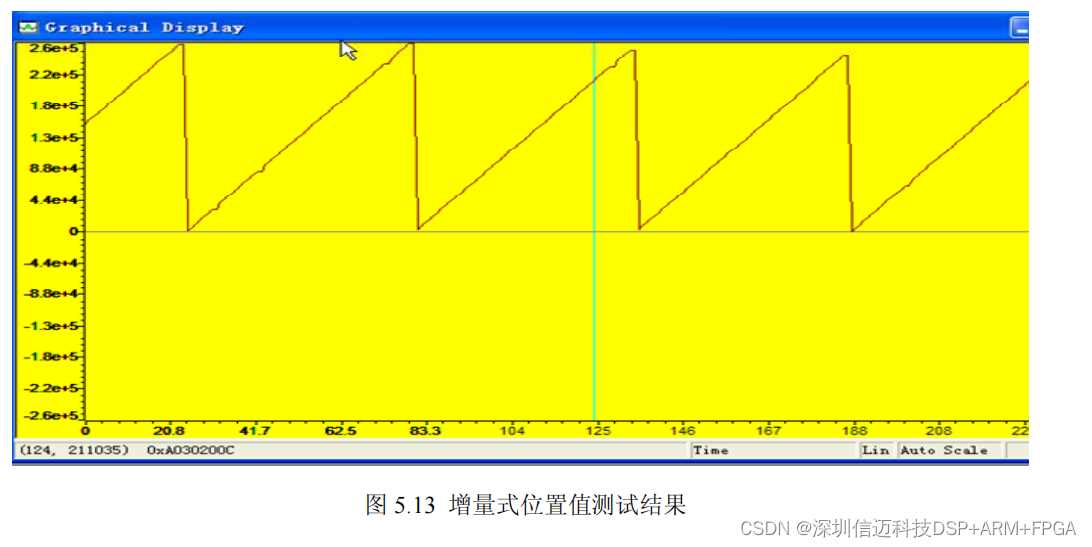

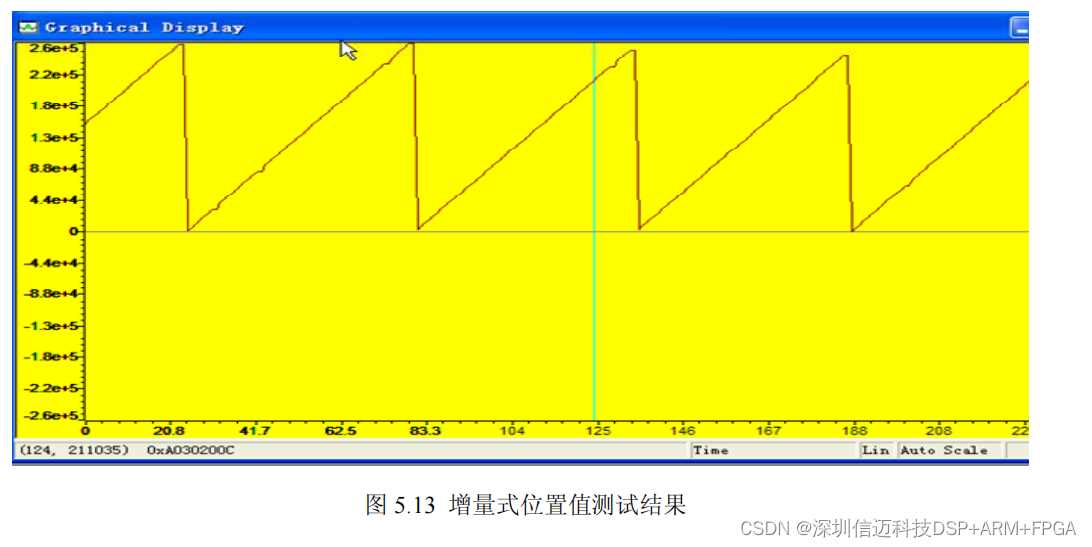

5.3.6 系统对增量式位置值采集的验证

验证方法:采用旋转电机自带的增量式接口提供增量式位置数据,利用

CCS

信号

分析工具

Graph

图形窗口对采集的增量式位置值实时作图显示,以判断增量式位置数据

采集的正确性。测试中电机开环,匀速旋转,定时手动复位位置数据为零,图

5.13

即为

测试结果,从图中可以看出,位置值数据从零均匀增加,手动复位时跳变为零,之后又

匀速增加,与理论预期完全吻合。

信迈提供DSP+FPGA电路仿真方案。