FPGA基于RIFFA实现PCIE采集HDMI传输,提供工程源码和QT上位机

目录

- 1、前言

- 2、RIFFA理论基础

- 3、设计思路和架构

- 4、vivado工程详解

- 5、上板调试验证并演示

- 6、福利:工程代码的获取

1、前言

PCIE是目前速率很高的外部板卡与CPU通信的方案之一,广泛应用于电脑主板与外部板卡的通讯,PCIE协议极其复杂,想要掌握不容易,所以Xilinx和Altera等FPGA厂商直接推出了相关IP供用户使用,比如Xilinx的XDMA,这种IP直接集成了PCIE通信的所有内核资源,并已封装为AXIS接口,用户在使用时只需要按照AXIS流数据格式收发即可,相当于傻瓜式使用PCIE,但是,如果你想装个杯,想要自己研究甚至手写一个PCIE收发器呢?那本文就适合你的胃口了。。。

本文详细描述了RIFFA的实现设计方案,使用Xilinx的PCIE IP作为桥接工具,实现PCIE和电脑主机的图像采集传输,将结合HDMI输入视频,将摄像头数据采集到 DDR3 内存中,然后通过上位机实验 PCIE 接口将摄像头图像采集到QT上位机中,做到实时显示图像,工程代码编译通过后上板调试验证,文章末尾有演示效果,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

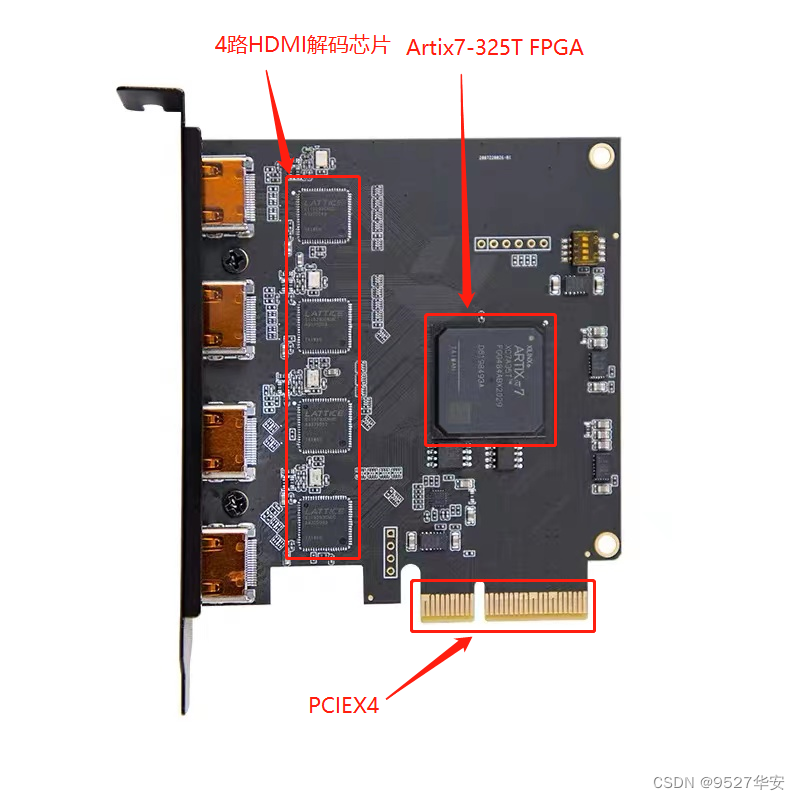

本设计实际项目意义十分重要,他可以直接做成产品,比如某宝的这种产品

这种市面上常见的,一千多块钱的HDMI视频采集卡用本工程就可以实现,我们来解析一下这块板子:

输入是4路HDMI视频接口,经过4颗解码芯片解为RGB888视频,再用Artix7 FPGA做PCIE驱动即可完成,输出PCIEX4,这样一个板卡就做好了,看起来很高端,实则很简单,用这个工程就可以做。。。

2、RIFFA理论基础

前面已经写过两篇关于RIFFA理论的文章,请兄弟们线参考一下:

1、RIFFA与PCIE IP的FPGA架构,参考链接RIFFA

2、RIFFA与PCIE的测速实验,参考链接测速实验

3、RIFFA与PCIE的ov5640摄像头视频采集,参考链接PCIE ov5640

前面的2篇文章只是理论基础和在FPGA上实现了部署,属于学习和验证性质,从本文开始,我们正式进入项目实战阶段,使用RIFFA与PCIE架构采集视频,并在QT上位机上显示,后面还将出采集HDMI视频的工程,敬请期待。

3、设计思路和架构

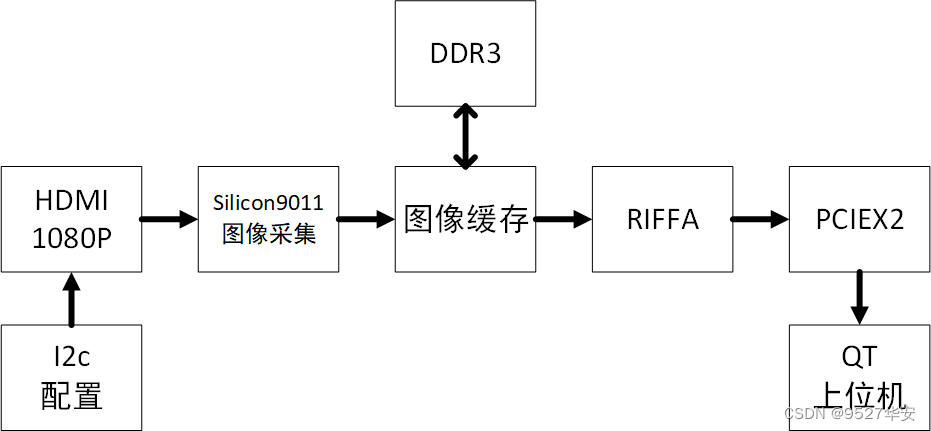

设计思路和架构如下:

输入为HDMI视频,i2c配置为默认1920x1080的分辨率,输入分辨率是自动识别的;

图像采集:

HDMI采集使用silicon9011芯片完成,silicon9011需要i2c配置才能使用,关于silicon9011的配置和使用,请参考我之前的文章silicon9011

图像缓存:

经常看我文章的兄弟应该都熟悉,我的图像缓存架构一般喜欢用FDMA方案,关于FDMA方案可以参考我之前的文章FDMA方案

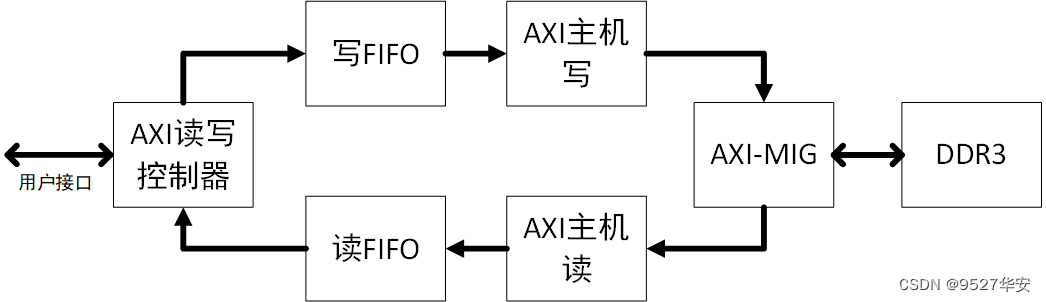

图像缓存:

图像缓存架构如下:

但本实验没有使用该方案,而是使用另一种基于AXI4-FULL的图像缓存方案,考虑到PCIE图传的延时性,只做到了2帧的图像缓存,高于2帧延迟就大了,项目不允许,所以采用乒乓架构实现图像2帧缓存,具体可看代码,后面我也会专门出一期讲解该方案的文章和验证工程;

RIFFA-PCIEX2架构

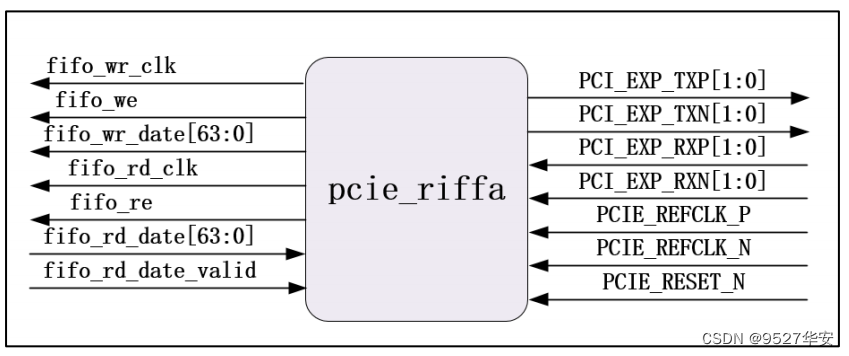

RIFFA-PCIEX2架构如下:

请参考我前面的2期文章,这里对原始工程的该架构部分做了修改,以适应图像传输的接口要求。

PCIE 的顶层模块与测速模块几乎一致,只是将用户端数据引出来,修改了部分接口。

右边接口为 PCIE 接口,未对其进行修改,左边接口为新增 fifo 接口,包括读 fifo 与写 fifo接口,用于将 pcie 的读写数据转接成 fifo 接口,以供其他模块使用。

RIFFA-PCIEX2模块顶层接口如下,标出了新增的端口:

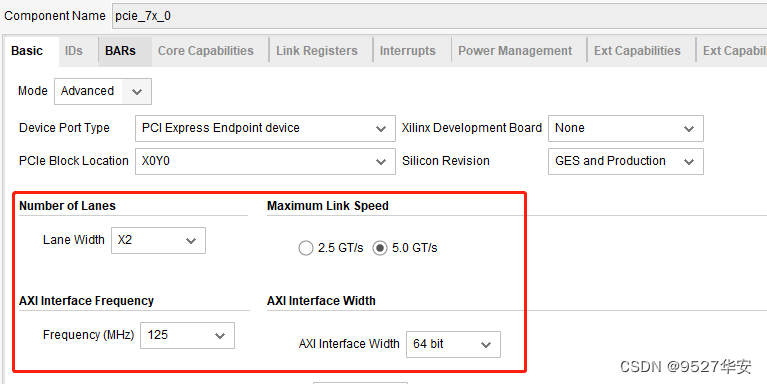

module pcie_riffa #(

parameter C_NUM_CHNL = 1, // Number of RIFFA Channels

parameter C_NUM_LANES = 2, // Number of PCIe Lanes

parameter C_PCI_DATA_WIDTH = 64, // Settings from Vivado IP Generator

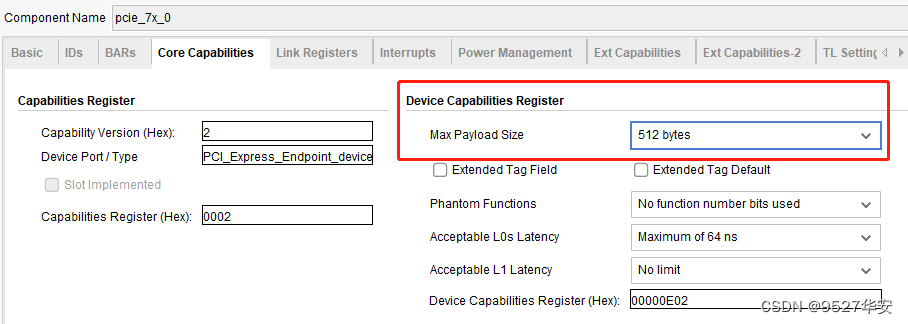

parameter C_MAX_PAYLOAD_BYTES = 512,

parameter C_LOG_NUM_TAGS = 5,

parameter PCIE_TX_LEN = 32'd307200

)(

//增加端口开始

//写端口

output fifo_wr_clk, //pcie写数据到外部的时钟信号

output fifo_we, //pcie写数据的使能信号

output [C_PCI_DATA_WIDTH-1:0]fifo_wr_date, //pcie写数据到外部

//读端口

output fifo_rd_clk, //pcie从外部读取数据时钟

output fifo_re, //pcie从外部读取数据使能

input [C_PCI_DATA_WIDTH-1:0]fifo_rd_date, //pcie读数据

input fifo_rd_date_valid, //外部数据可读有效

//增加端口结束

output [(C_NUM_LANES - 1) : 0] PCI_EXP_TXP,

output [(C_NUM_LANES - 1) : 0] PCI_EXP_TXN,

input [(C_NUM_LANES - 1) : 0] PCI_EXP_RXP,

input [(C_NUM_LANES - 1) : 0] PCI_EXP_RXN,

//output [3:0] LED,

input PCIE_REFCLK_P,

input PCIE_REFCLK_N,

input PCIE_RESET_N

);

新增信号接口主要用于将 pcie 发送数据与接收数据以 fifo 接口引出,用户只需将其连接到 fifo 模块或者类似 fifo 模块即可,本工程将其读取数据连接到 ddr3 顶层模块,即可完成从 ddr3 中读取数据,将其通过 pcie 发送到上位机。

PCIE发送数据模块:

PCIE 数据模块为本工程的重点,PCIE 数据的提取将由此模块将 PCIE 数据装换为FIFO 数据接口,以完成数据的提取。chnl_tester.v 模块中的信号接口有接收数据端口与发送数据端口组成,里面有 1 个状态机组成,有 4 种状态,等待读状态,读数据,等待写状态,写数据这 4 个过程。此状态机当接收到上位机发送到 PCIE 的数据时进入读数据状态,随后将进入写数据过程,将数据完完整整的写会到上位机,因此测速模块发送和接收的数据都是从 1 到发送长度最大值的序列。

具体请看代码。。。

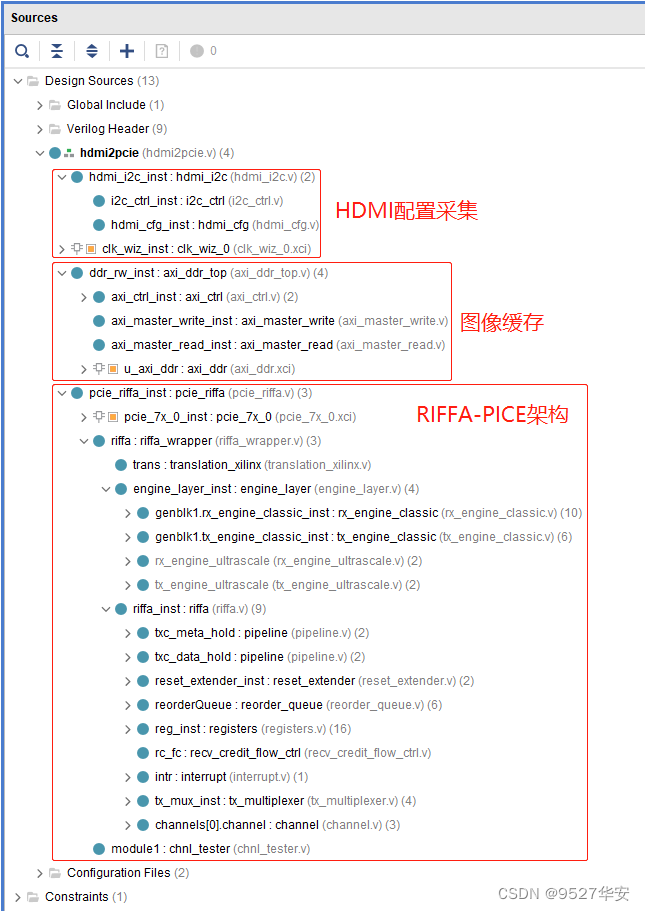

4、vivado工程详解

开发板:Xilinx xc7a100tfgg484-2

开发环境:Vivado2019.1;

输入:HDMI,分辨率1920x1080;

输出:PCIEX2;QT上位机显示收发速率;

工程代码架构如下:

PCIE IP配置如下:

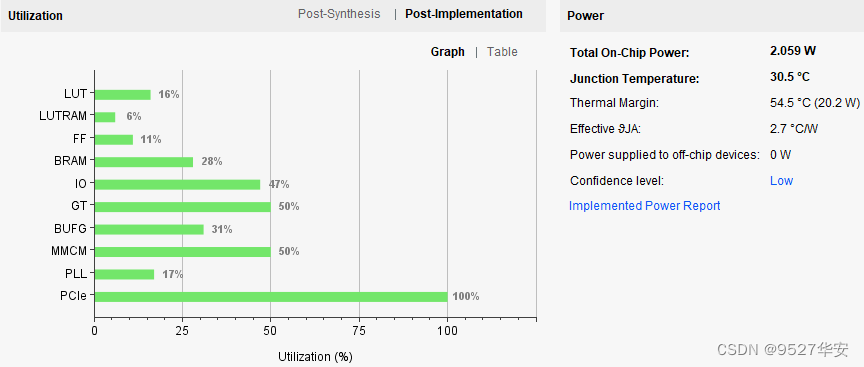

FPGA资源消耗和功耗预估如下:

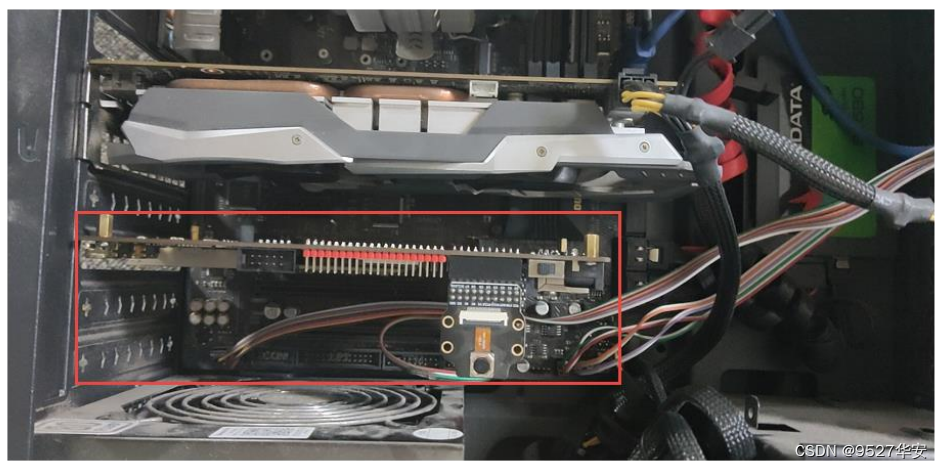

5、上板调试验证并演示

6、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

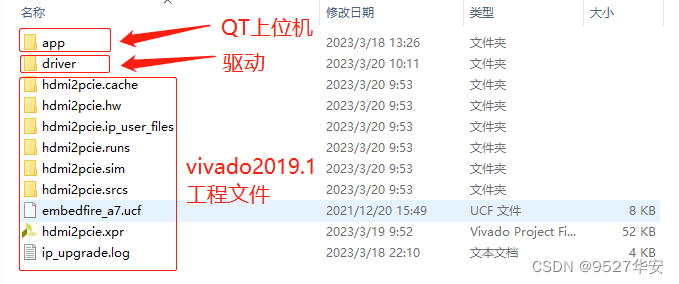

网盘资料如下:

网盘资料内容如下:已压缩,方便大家下载。。。