FPGA——DDR3的IP核

FPGA——DDR3的ip核

- IP核配置

- 基于MIG核代码

- 基于AXI接口的DDR3

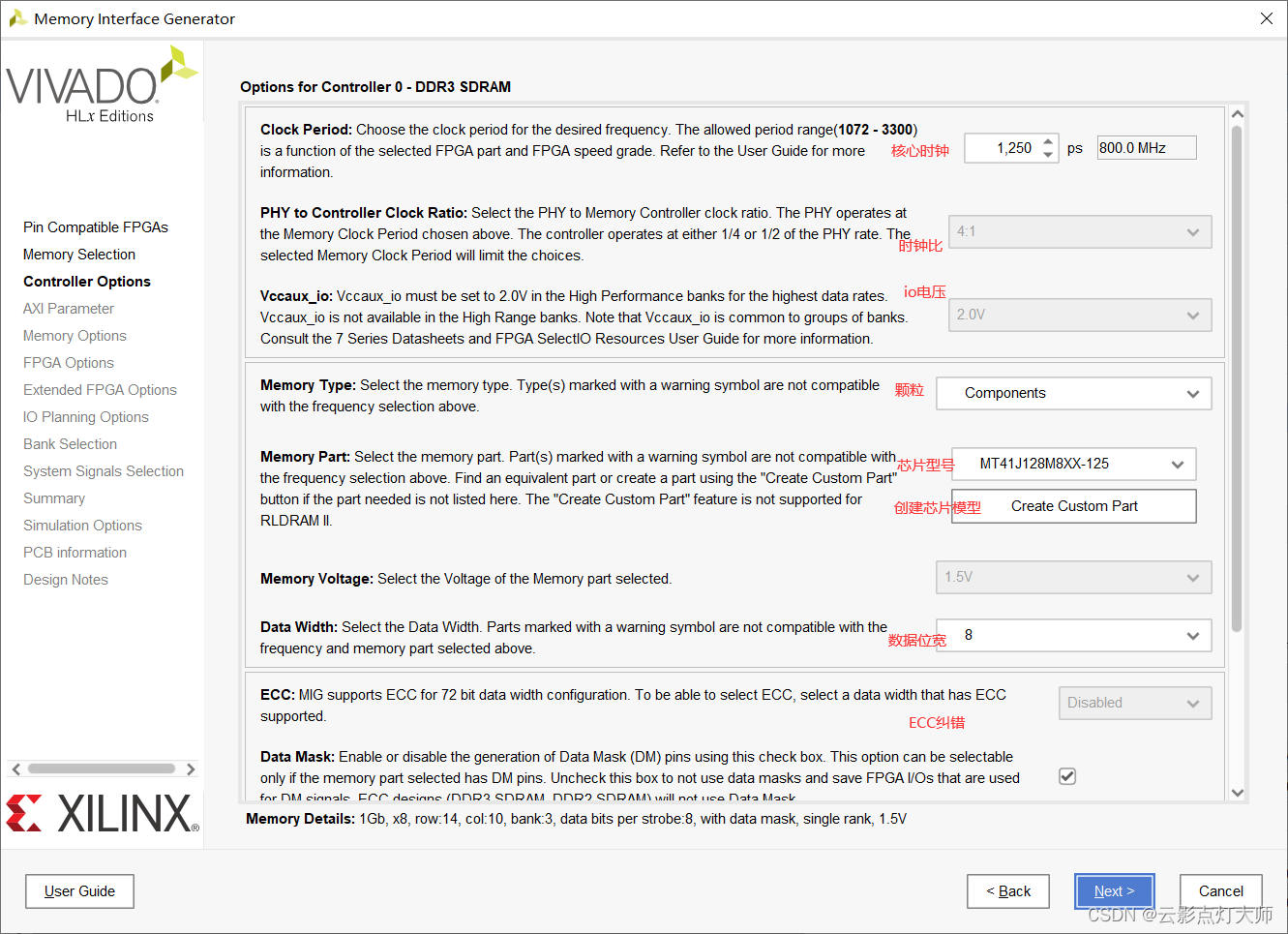

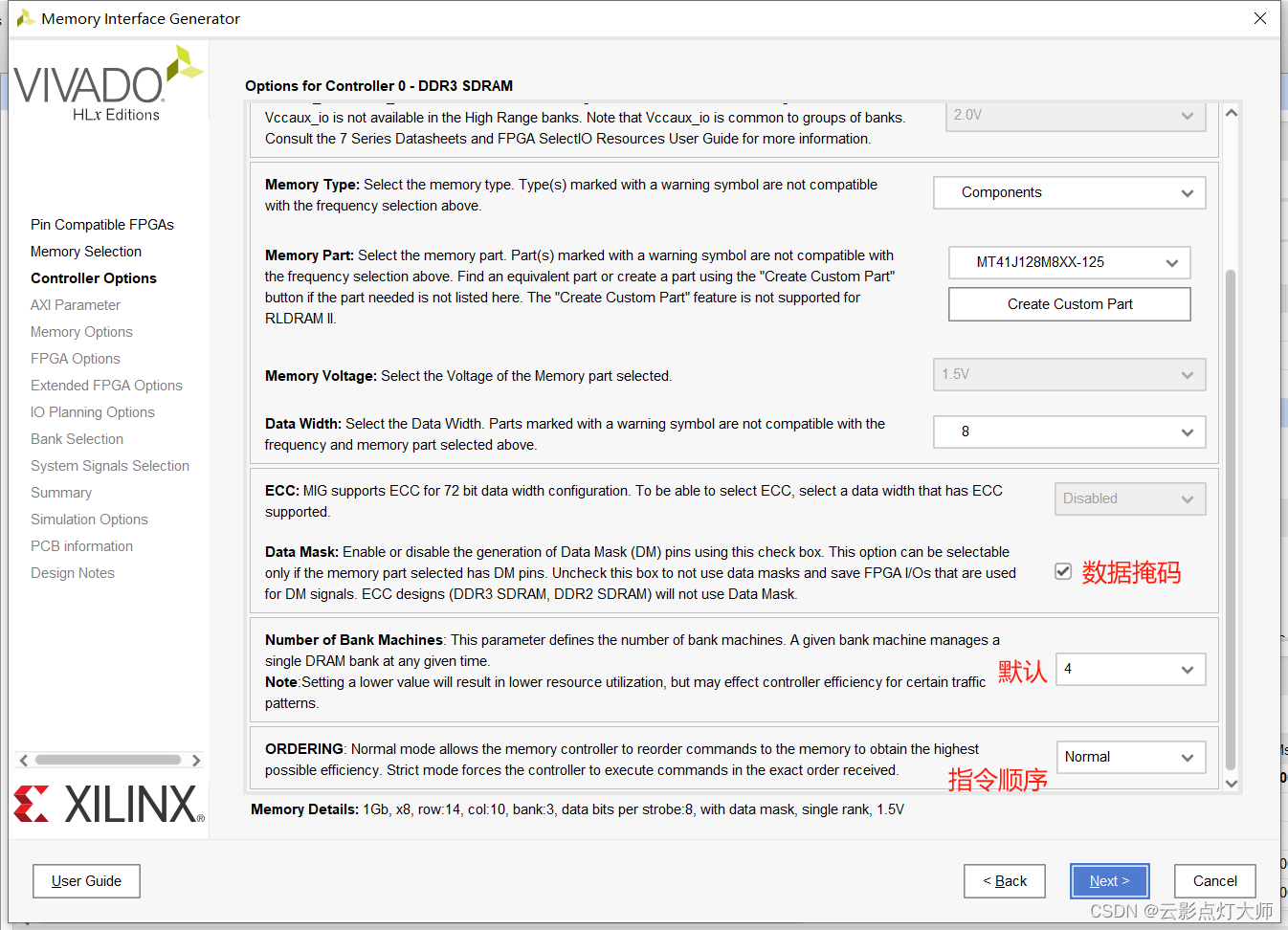

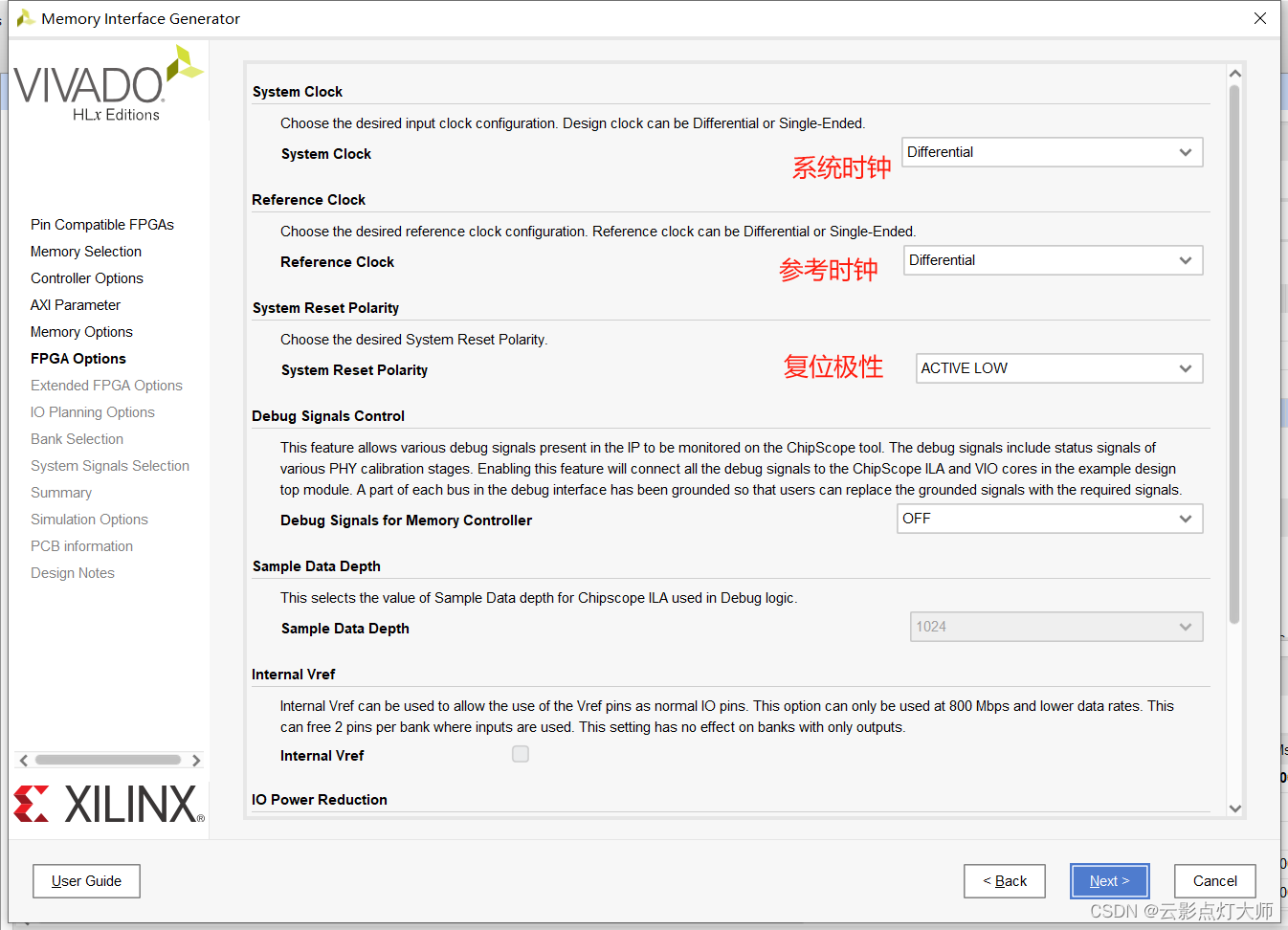

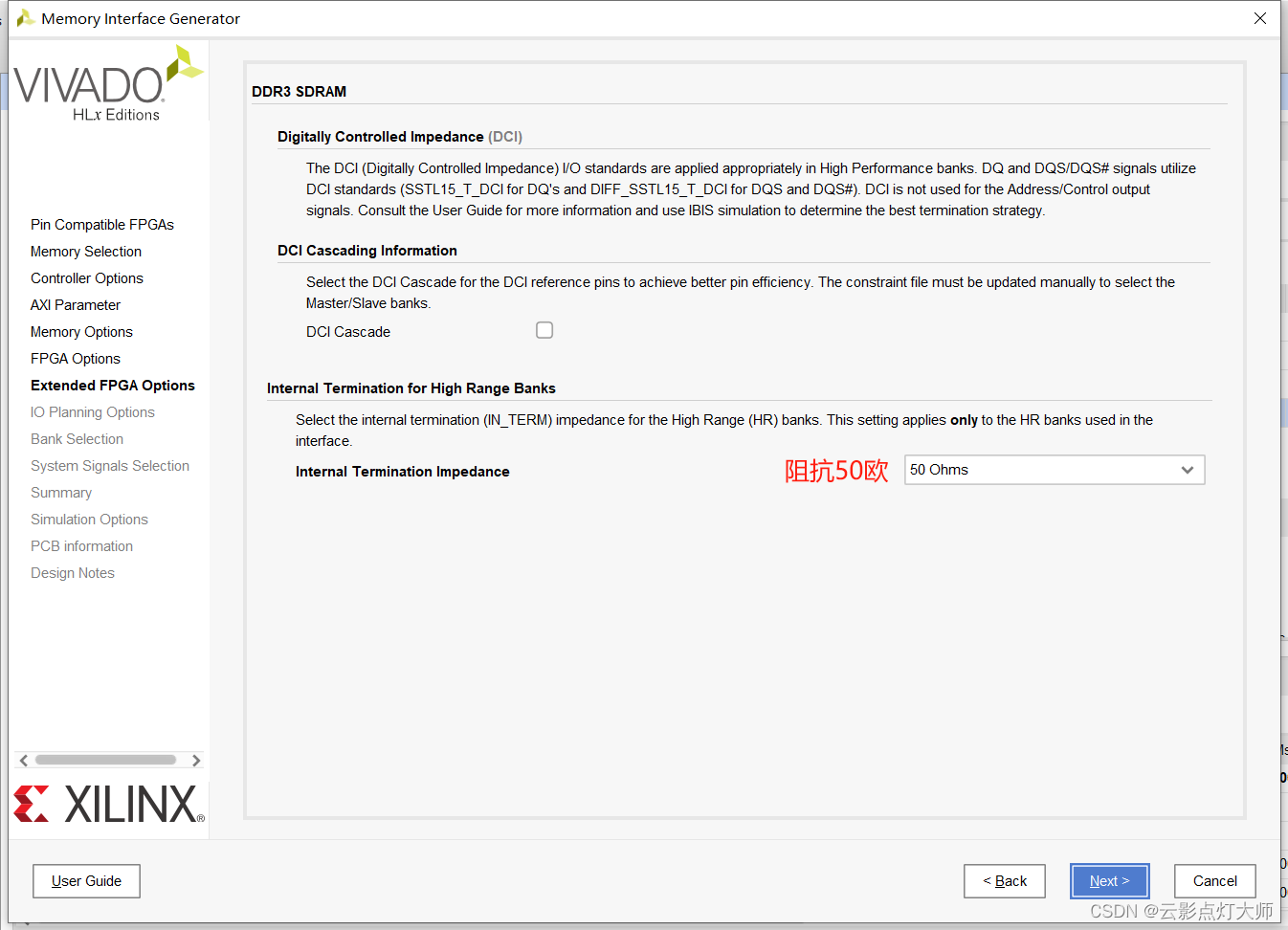

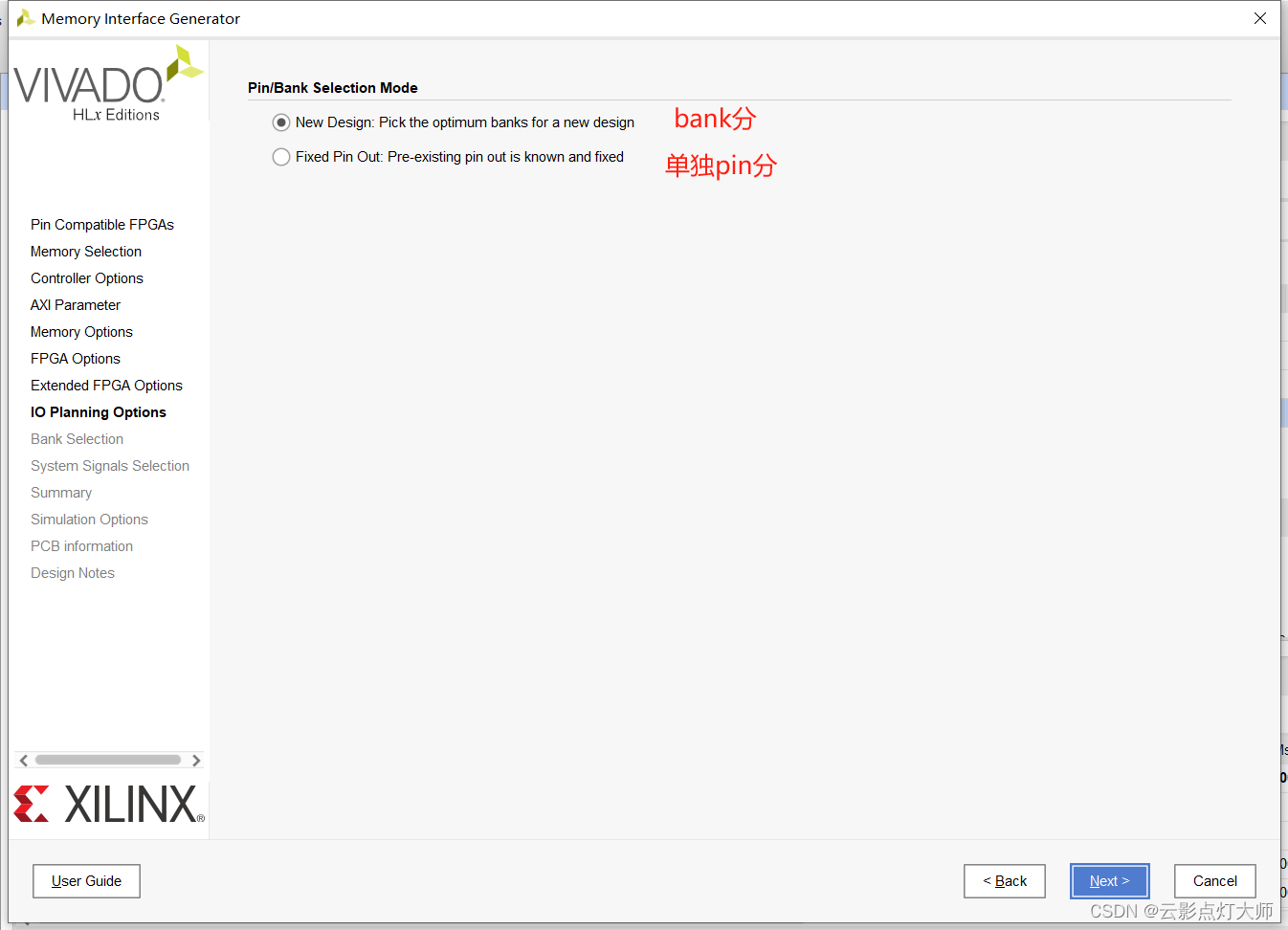

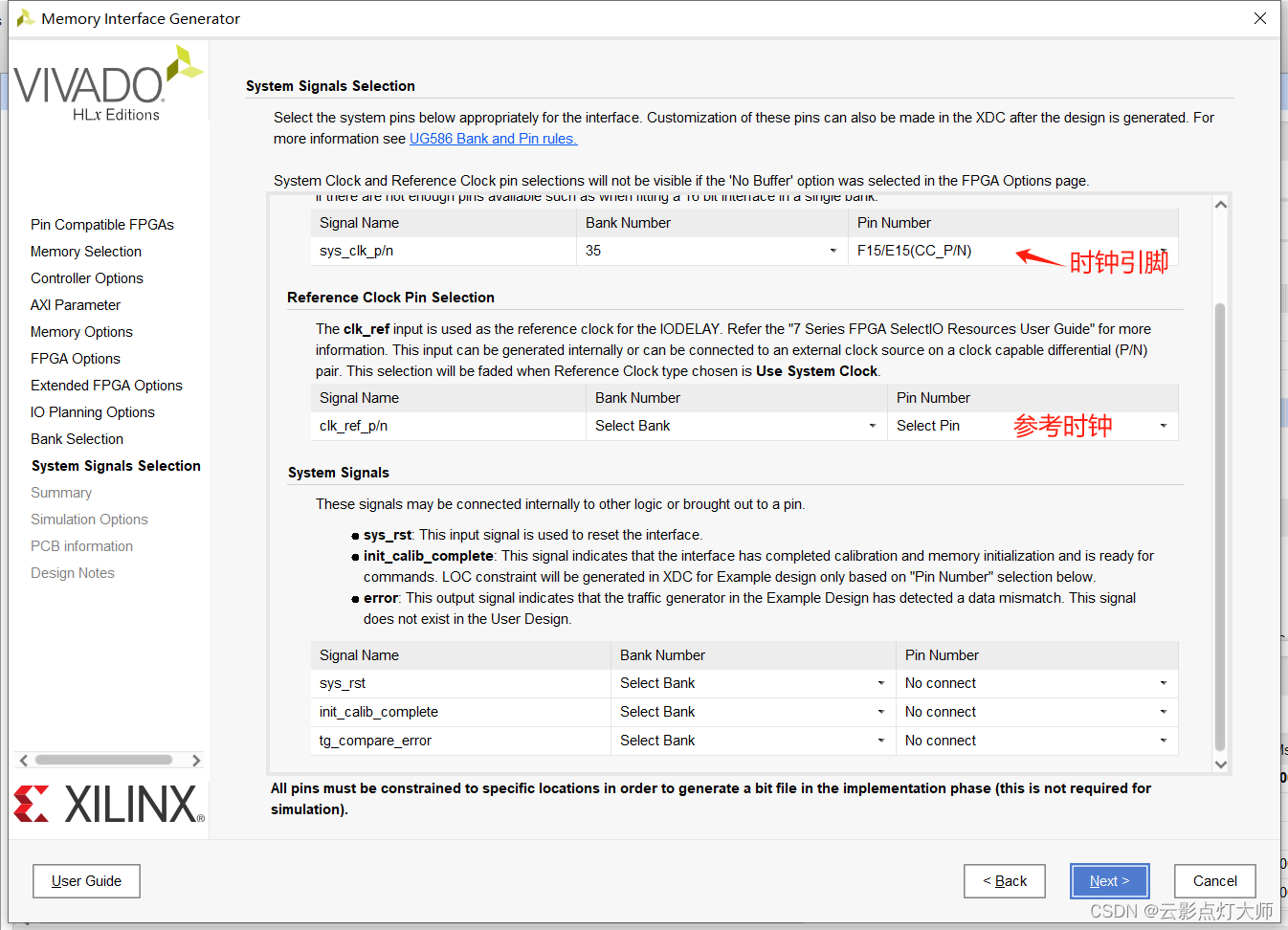

IP核配置

1

2

3

4

5

6

基于MIG核代码

控制MIG核的信号进行读写

module MIG_APP_Drive(

input i_ui_clk ,

input i_ui_rst ,

input init_calib_complete ,

output [28:0] app_addr ,

output [2 :0] app_cmd ,

output app_en ,

output [255:0] app_wdf_data ,

output app_wdf_end ,

output app_wdf_wren ,

input [255:0] app_rd_data ,

input app_rd_data_end ,

input app_rd_data_valid ,

input app_rdy ,

input app_wdf_rdy ,

output [31:0] app_wdf_mask ,

input [1 :0] i_operation_cmd ,

input [15:0] i_operation_len ,

input [28:0] i_operation_addr ,

input i_operation_valid ,

output o_operation_ready ,

input [255:0] i_write_data ,

input i_write_last ,

input i_write_valid ,

output [255:0] o_read_data ,

output o_read_valid

);

/***************function**************/

/***************parameter*************/

localparam P_ST_INIT = 0 ,

P_ST_IDLE = 1 ,

P_ST_WAIT = 2 ,

P_ST_WRITE = 3 ,

P_ST_READ = 4 ,

P_ST_READ_WAIT = 5 ;

/***************port******************/

/***************mechine***************/

(* mark_debug = "true" *)reg [7 :0] r_st_current ;

reg [7 :0] r_st_next ;

reg [15:0] r_st_cnt ;

/***************reg*******************/

reg [28:0] ro_app_addr ;

reg [2 :0] ro_app_cmd ;

reg ro_app_en ;

reg ro_app_wdf_wren ;

reg [31:0] ro_app_wdf_mask ;

reg ro_operation_ready ;

reg [255:0] ro_read_data ;

reg ro_read_valid ;

reg [1 :0] ri_operation_cmd ;

reg [15:0] ri_operation_len ;

reg [28:0] ri_operation_addr ;

reg r_op_act ;

reg [15:0] r_write_cnt ;

reg [15:0] r_read_cnt ;

(* mark_debug = "true" *)reg [15:0] r_read_data_cnt ;

reg [7 :0] r_init ;

/***************wire******************/

wire w_op_act ;

wire [255:0] w_write_fifo_dout ;

wire w_write_fifo_empty ;

wire w_write_fifo_full ;

wire w_mig_wvalid ;

wire w_mig_rvalid ;

wire w_write_fifo_rd_en ;

/***************component*************/

FIFO_256X512 FIFO_256X512_U0 (

.clk (i_ui_clk ), // input wire clk

.din (i_write_data ), // input wire [63 : 0] din

.wr_en (i_write_valid ), // input wire wr_en

.rd_en (w_write_fifo_rd_en ), // input wire rd_en

.dout (w_write_fifo_dout ), // output wire [63 : 0] dout

.full (w_write_fifo_full ), // output wire full

.empty (w_write_fifo_empty ) // output wire empty

);

/***************assign****************/

assign app_addr = ro_app_addr ;

assign app_cmd = ro_app_cmd ;

assign app_en = ro_app_en & app_rdy ;

assign app_wdf_data = w_write_fifo_dout ;

assign app_wdf_end = app_wdf_wren ;

assign app_wdf_wren = ro_app_wdf_wren & app_rdy & app_wdf_rdy;

assign app_wdf_mask = ro_app_wdf_mask ;

assign o_operation_ready = ro_operation_ready ;

assign o_read_data = ro_read_data ;

assign o_read_valid = ro_read_valid ;

assign w_op_act = i_operation_valid & o_operation_ready;

assign w_mig_wvalid = app_rdy & app_wdf_rdy & app_en & ro_app_wdf_wren & app_cmd == 0;

assign w_write_fifo_rd_en = w_mig_wvalid ;

assign w_mig_rvalid = app_rdy & app_en & app_cmd == 1;

/***************always****************/

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

r_st_current <= P_ST_INIT;

else

r_st_current <= r_st_next;

end

always@(*)

begin

case(r_st_current)

P_ST_INIT : r_st_next = &r_init ? P_ST_IDLE : P_ST_INIT;

P_ST_IDLE : r_st_next = r_op_act ?

ri_operation_cmd == 0 ? P_ST_WAIT : P_ST_READ

: P_ST_IDLE ;

P_ST_WAIT : r_st_next = r_st_cnt == 4 ? P_ST_WRITE : P_ST_WAIT ;

P_ST_WRITE : r_st_next = r_write_cnt == ri_operation_len - 1 & w_mig_wvalid ? P_ST_IDLE : P_ST_WRITE ;

P_ST_READ : r_st_next = r_read_cnt == ri_operation_len - 2 & w_mig_rvalid ? P_ST_READ_WAIT: P_ST_READ ;

P_ST_READ_WAIT : r_st_next = r_read_data_cnt >= ri_operation_len - 2 & app_rd_data_valid ? P_ST_IDLE : P_ST_READ_WAIT ;

default : r_st_next = P_ST_INIT;

endcase

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

r_init <= 'd0;

else

r_init <= {r_init[6 :0],init_calib_complete};

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

r_st_cnt <= 'd0;

else if(r_st_current != r_st_next)

r_st_cnt <= 'd0;

else

r_st_cnt <= r_st_cnt + 1;

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst) begin

ri_operation_cmd <= 'd0;

ri_operation_len <= 'd0;

ri_operation_addr <= 'd0;

end else if(w_op_act) begin

ri_operation_cmd <= i_operation_cmd ;

ri_operation_len <= i_operation_len ;

ri_operation_addr <= i_operation_addr;

end else begin

ri_operation_cmd <= ri_operation_cmd ;

ri_operation_len <= ri_operation_len ;

ri_operation_addr <= ri_operation_addr;

end

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

r_op_act <= 'd0;

else

r_op_act <= w_op_act;

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst) begin

ro_app_cmd <= 'd0;

ro_app_en <= 'd0;

end else if(r_st_current == P_ST_WRITE) begin

ro_app_cmd <= 'd0;

ro_app_en <= 'd1;

end else if(r_st_current == P_ST_READ) begin

ro_app_cmd <= 'd1;

ro_app_en <= 'd1;

end else begin

ro_app_cmd <= 'd0;

ro_app_en <= 'd0;

end

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

ro_app_addr <= 'd0;

else if(w_op_act)

ro_app_addr <= i_operation_addr;

else if(w_mig_wvalid)

ro_app_addr <= ro_app_addr + 8 ;

else if(w_mig_rvalid)

ro_app_addr <= ro_app_addr + 8 ;

else

ro_app_addr <= ro_app_addr;

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

ro_app_wdf_mask <= 'd0;

else

ro_app_wdf_mask <= 'd0;

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

ro_app_wdf_wren <= 'd0;

else if(r_st_current == P_ST_WRITE)

ro_app_wdf_wren <= 'd1;

else

ro_app_wdf_wren <= 'd0;

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst) begin

ro_read_data <= 'd0;

ro_read_valid <= 'd0;

end else begin

ro_read_data <= app_rd_data;

ro_read_valid <= app_rd_data_valid;

end

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

ro_operation_ready <= 'd0;

else if(w_op_act)

ro_operation_ready <= 'd0;

else if(r_st_next == P_ST_IDLE)

ro_operation_ready <= 'd1;

else

ro_operation_ready <= ro_operation_ready;

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

r_write_cnt <= 'd0;

else if(r_st_current == P_ST_IDLE)

r_write_cnt <= 'd0;

else if(w_mig_wvalid)

r_write_cnt <= r_write_cnt + 1;

else

r_write_cnt <= r_write_cnt;

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

r_read_cnt <= 'd0;

else if(r_st_current == P_ST_IDLE)

r_read_cnt <= 'd0;

else if(w_mig_rvalid)

r_read_cnt <= r_read_cnt + 1;

else

r_read_cnt <= r_read_cnt;

end

always@(posedge i_ui_clk,posedge i_ui_rst)

begin

if(i_ui_rst)

r_read_data_cnt <= 'd0;

else if(r_st_current == P_ST_IDLE)

r_read_data_cnt <= 'd0;

else if(app_rd_data_valid)

r_read_data_cnt <= r_read_data_cnt + 1;

else

r_read_data_cnt <= r_read_data_cnt;

end

endmodule

示列

DDR3_MIG u_DDR3_MIG (

// Memory interface ports

.ddr3_addr (ddr3_addr ),

.ddr3_ba (ddr3_ba ),

.ddr3_cas_n (ddr3_cas_n ),

.ddr3_ck_n (ddr3_ck_n ),

.ddr3_ck_p (ddr3_ck_p ),

.ddr3_cke (ddr3_cke ),

.ddr3_ras_n (ddr3_ras_n ),

.ddr3_reset_n (ddr3_reset_n ),

.ddr3_we_n (ddr3_we_n ),

.ddr3_dq (ddr3_dq ),

.ddr3_dqs_n (ddr3_dqs_n ),

.ddr3_dqs_p (ddr3_dqs_p ),

.ddr3_cs_n (ddr3_cs_n ),

.ddr3_dm (ddr3_dm ),

.ddr3_odt (ddr3_odt ),

// Application interface ports

.init_calib_complete (w_init_calib_complete ),

.app_addr (w_app_addr ),

.app_cmd (w_app_cmd ),

.app_en (w_app_en ),

.app_wdf_data (w_app_wdf_data ),

.app_wdf_end (w_app_wdf_end ),

.app_wdf_wren (w_app_wdf_wren ),

.app_rd_data (w_app_rd_data ),

.app_rd_data_end (w_app_rd_data_end ),

.app_rd_data_valid (w_app_rd_data_valid ),

.app_rdy (w_app_rdy ),

.app_wdf_rdy (w_app_wdf_rdy ),

.app_wdf_mask (w_app_wdf_mask ),

.app_sr_req (0 ),

.app_ref_req (0 ),

.app_zq_req (0 ),

.app_sr_active ( ),

.app_ref_ack ( ),

.app_zq_ack ( ),

.ui_clk (ui_clk ),

.ui_clk_sync_rst (ui_clk_sync_rst ),

// System Clock Ports

.sys_clk_p (i_clk_200m_p ),

.sys_clk_n (i_clk_200m_n ),

.sys_rst (0 )

);

MIG_APP_Drive MIG_APP_Drive_u0(

.i_ui_clk (ui_clk ),

.i_ui_rst (ui_clk_sync_rst ),

.init_calib_complete (w_init_calib_complete ),

.app_addr (w_app_addr ),

.app_cmd (w_app_cmd ),

.app_en (w_app_en ),

.app_wdf_data (w_app_wdf_data ),

.app_wdf_end (w_app_wdf_end ),

.app_wdf_wren (w_app_wdf_wren ),

.app_rd_data (w_app_rd_data ),

.app_rd_data_end (w_app_rd_data_end ),

.app_rd_data_valid (w_app_rd_data_valid ),

.app_rdy (w_app_rdy ),

.app_wdf_rdy (w_app_wdf_rdy ),

.app_wdf_mask (w_app_wdf_mask ),

.i_operation_cmd (w_app_operation_cmd ),

.i_operation_len (w_app_operation_len ),

.i_operation_addr (w_app_operation_addr ),

.i_operation_valid (w_app_operation_valid ),

.o_operation_ready (w_app_operation_ready ),

.i_write_data (w_app_write_data ),

.i_write_last (w_app_write_last ),

.i_write_valid (w_app_write_valid ),

.o_read_data (w_app_read_data ),

.o_read_valid (w_app_read_valid )

);

基于AXI接口的DDR3

module AXI_Master_Drive(

input i_clk ,

input i_rst ,

(* mark_debug = "true" *) input i_init_calib_complete ,

output [3 :0] m_axi_awid ,

output [29:0] m_axi_awaddr ,

output [7 :0] m_axi_awlen ,

output [2 :0] m_axi_awsize ,

output [1 :0] m_axi_awburst ,

output [0 :0] m_axi_awlock ,

output [3 :0] m_axi_awcache ,

output [2 :0] m_axi_awprot ,

output [3 :0] m_axi_awqos ,

output m_axi_awvalid ,

(* mark_debug = "true" *) input m_axi_awready ,

output [255:0] m_axi_wdata ,

output [31:0] m_axi_wstrb ,

output m_axi_wlast ,

output m_axi_wvalid ,

(* mark_debug = "true" *) input m_axi_wready ,

input [3 :0] m_axi_bid ,

input [1 :0] m_axi_bresp ,

(* mark_debug = "true" *) input m_axi_bvalid ,

output m_axi_bready ,

output [3 :0] m_axi_arid ,

output [29:0] m_axi_araddr ,

output [7 :0] m_axi_arlen ,

output [2 :0] m_axi_arsize ,

output [1 :0] m_axi_arburst ,

output [0 :0] m_axi_arlock ,

output [3 :0] m_axi_arcache ,

output [2 :0] m_axi_arprot ,

output [3 :0] m_axi_arqos ,

output m_axi_arvalid ,

(* mark_debug = "true" *) input m_axi_arready ,

input [3 :0] m_axi_rid ,

input [255:0] m_axi_rdata ,

input [1 :0] m_axi_rresp ,

input m_axi_rlast ,

input m_axi_rvalid ,

output m_axi_rready

);

/***************function**************/

/***************parameter*************/

localparam P_ST_INIT = 0 ,

P_ST_IDLE = 1 ,

P_ST_WRITE = 2 ,

P_ST_READ = 3 ;

localparam P_LEN = 16 ;

/***************port******************/

/***************mechine***************/

(* mark_debug = "true" *)reg [7 :0] r_st_current ;

reg [7 :0] r_st_next ;

reg [15:0] r_st_cnt ;

/***************reg*******************/

reg [3 :0] ro_m_axi_awid ;

(* mark_debug = "true" *)reg [29:0] ro_m_axi_awaddr ;

(* mark_debug = "true" *)reg [7 :0] ro_m_axi_awlen ;

reg [2 :0] ro_m_axi_awsize ;

reg [1 :0] ro_m_axi_awburst ;

reg [0 :0] ro_m_axi_awlock ;

reg [3 :0] ro_m_axi_awcache ;

reg [2 :0] ro_m_axi_awprot ;

reg [3 :0] ro_m_axi_awqos ;

(* mark_debug = "true" *)reg ro_m_axi_awvalid ;

(* mark_debug = "true" *)reg [255:0] ro_m_axi_wdata ;

reg [31:0] ro_m_axi_wstrb ;

(* mark_debug = "true" *)reg ro_m_axi_wlast ;

(* mark_debug = "true" *)reg ro_m_axi_wvalid ;

(* mark_debug = "true" *)reg ro_m_axi_bready ;

reg [3 :0] ro_m_axi_arid ;

(* mark_debug = "true" *)reg [29:0] ro_m_axi_araddr ;

(* mark_debug = "true" *)reg [7 :0] ro_m_axi_arlen ;

reg [2 :0] ro_m_axi_arsize ;

reg [1 :0] ro_m_axi_arburst ;

reg [0 :0] ro_m_axi_arlock ;

reg [3 :0] ro_m_axi_arcache ;

reg [2 :0] ro_m_axi_arprot ;

reg [3 :0] ro_m_axi_arqos ;

(* mark_debug = "true" *)reg ro_m_axi_arvalid ;

(* mark_debug = "true" *)reg ro_m_axi_rready ;

reg [3 :0] ri_m_axi_rid ;

(* mark_debug = "true" *)reg [255:0] ri_m_axi_rdata ;

reg [1 :0] ri_m_axi_rresp ;

(* mark_debug = "true" *)reg ri_m_axi_rlast ;

(* mark_debug = "true" *)reg ri_m_axi_rvalid ;

reg [15:0] r_read_cnt;

/***************wire******************/

wire w_aw_act ;

wire w_w_act ;

wire w_br_act ;

wire w_ar_act ;

wire w_r_act ;

/***************component*************/

/***************assign****************/

assign m_axi_awid = ro_m_axi_awid ;

assign m_axi_awaddr = ro_m_axi_awaddr ;

assign m_axi_awlen = ro_m_axi_awlen ;

assign m_axi_awsize = ro_m_axi_awsize ;

assign m_axi_awburst = ro_m_axi_awburst ;

assign m_axi_awlock = ro_m_axi_awlock ;

assign m_axi_awcache = ro_m_axi_awcache ;

assign m_axi_awprot = ro_m_axi_awprot ;

assign m_axi_awqos = ro_m_axi_awqos ;

assign m_axi_awvalid = ro_m_axi_awvalid ;

assign m_axi_wdata = ro_m_axi_wdata ;

assign m_axi_wstrb = ro_m_axi_wstrb ;

assign m_axi_wlast = ro_m_axi_wlast ;

assign m_axi_wvalid = ro_m_axi_wvalid ;

assign m_axi_bready = ro_m_axi_bready ;

assign m_axi_arid = ro_m_axi_arid ;

assign m_axi_araddr = ro_m_axi_araddr ;

assign m_axi_arlen = ro_m_axi_arlen ;

assign m_axi_arsize = ro_m_axi_arsize ;

assign m_axi_arburst = ro_m_axi_arburst ;

assign m_axi_arlock = ro_m_axi_arlock ;

assign m_axi_arcache = ro_m_axi_arcache ;

assign m_axi_arprot = ro_m_axi_arprot ;

assign m_axi_arqos = ro_m_axi_arqos ;

assign m_axi_arvalid = ro_m_axi_arvalid ;

assign m_axi_rready = ro_m_axi_rready ;

assign w_aw_act = m_axi_awvalid & m_axi_awready ;//写地址激活信号

assign w_w_act = m_axi_wvalid & m_axi_wready ;//写数据激活信号

assign w_br_act = m_axi_bvalid & m_axi_bready ;//响应激活信号

assign w_ar_act = m_axi_arvalid & m_axi_arready ;//读地址激活信号

assign w_r_act = m_axi_rvalid & m_axi_rready ;//读数据信号

/***************always****************/

//第一段状态机

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

r_st_current <= P_ST_IDLE;

else

r_st_current <= r_st_next;

end

//第二段

always@(*)

begin

case(r_st_current)

P_ST_INIT : r_st_next <= i_init_calib_complete ? P_ST_IDLE : P_ST_INIT;

P_ST_IDLE : r_st_next <= P_ST_WRITE;

P_ST_WRITE : r_st_next <= w_br_act ? P_ST_READ : P_ST_WRITE;

P_ST_READ : r_st_next <= r_read_cnt == P_LEN - 1 && w_r_act ? P_ST_IDLE : P_ST_READ;

default : r_st_next <= P_ST_IDLE;

endcase

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

r_st_cnt <= 'd0;

else if(r_st_current != r_st_next)

r_st_cnt <= 'd0;

else

r_st_cnt <= r_st_cnt + 1;

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst) begin

ro_m_axi_awid <= 'd0;

ro_m_axi_awaddr <= 'd0;

ro_m_axi_awlen <= 'd0;

ro_m_axi_awsize <= 'd0;

ro_m_axi_awburst <= 'd0;

ro_m_axi_awlock <= 'd0;

ro_m_axi_awcache <= 'd0;

ro_m_axi_awprot <= 'd0;

ro_m_axi_awqos <= 'd0;

ro_m_axi_awvalid <= 'd0;

end else if(w_aw_act) begin

ro_m_axi_awid <= 'd0;

ro_m_axi_awaddr <= 'd0;

ro_m_axi_awlen <= 'd0;

ro_m_axi_awsize <= 'd0;

ro_m_axi_awburst <= 'd0;

ro_m_axi_awlock <= 'd0;

ro_m_axi_awcache <= 'd0;

ro_m_axi_awprot <= 'd0;

ro_m_axi_awqos <= 'd0;

ro_m_axi_awvalid <= 'd0;

end else if(r_st_current == P_ST_WRITE && r_st_cnt == 0) begin

ro_m_axi_awid <= 'd0;

ro_m_axi_awaddr <= 'd0;

ro_m_axi_awlen <= P_LEN - 1;

ro_m_axi_awsize <= 3'b101;//32byte

ro_m_axi_awburst <= 'd1;//突发模式

ro_m_axi_awlock <= 'd0;

ro_m_axi_awcache <= 4'b0010;//无缓存

ro_m_axi_awprot <= 'd0;

ro_m_axi_awqos <= 'd0;

ro_m_axi_awvalid <= 'd1;//有效拉高

end else begin

ro_m_axi_awid <= ro_m_axi_awid ;

ro_m_axi_awaddr <= ro_m_axi_awaddr ;

ro_m_axi_awlen <= ro_m_axi_awlen ;

ro_m_axi_awsize <= ro_m_axi_awsize ;

ro_m_axi_awburst <= ro_m_axi_awburst;

ro_m_axi_awlock <= ro_m_axi_awlock ;

ro_m_axi_awcache <= ro_m_axi_awcache;

ro_m_axi_awprot <= ro_m_axi_awprot ;

ro_m_axi_awqos <= ro_m_axi_awqos ;

ro_m_axi_awvalid <= ro_m_axi_awvalid;

end

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

ro_m_axi_wdata <= 'd0;

else if(ro_m_axi_wdata == P_LEN - 1 && w_w_act)

ro_m_axi_wdata <= 'd0;

else if(w_w_act)

ro_m_axi_wdata <= ro_m_axi_wdata + 1;

else

ro_m_axi_wdata <= ro_m_axi_wdata;

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

ro_m_axi_wvalid <= 'd0;

else if(ro_m_axi_wdata == P_LEN - 1 && w_w_act)

ro_m_axi_wvalid <= 'd0;

else if(w_aw_act)

ro_m_axi_wvalid <= 'd1;

else

ro_m_axi_wvalid <= ro_m_axi_wvalid;

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

ro_m_axi_wlast <= 'd0;

else if(ro_m_axi_wdata == P_LEN - 1 && w_w_act)

ro_m_axi_wlast <= 'd0;

else if(ro_m_axi_wdata == P_LEN - 2)

ro_m_axi_wlast <= 'd1;

else

ro_m_axi_wlast <= ro_m_axi_wlast;

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

ro_m_axi_wstrb <= 32'hffffffff;

else

ro_m_axi_wstrb <= 32'hffffffff;

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

ro_m_axi_bready <= 'd0;

else if(w_br_act)

ro_m_axi_bready <= 'd0;

else if(ro_m_axi_wlast)

ro_m_axi_bready <= 'd1;

else

ro_m_axi_bready <= ro_m_axi_bready;

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst) begin

ro_m_axi_arid <= 'd0;

ro_m_axi_araddr <= 'd0;

ro_m_axi_arlen <= 'd0;

ro_m_axi_arsize <= 'd0;

ro_m_axi_arburst <= 'd0;

ro_m_axi_arlock <= 'd0;

ro_m_axi_arcache <= 'd0;

ro_m_axi_arprot <= 'd0;

ro_m_axi_arqos <= 'd0;

ro_m_axi_arvalid <= 'd0;

end else if(w_ar_act) begin

ro_m_axi_arid <= 'd0;

ro_m_axi_araddr <= 'd0;

ro_m_axi_arlen <= 'd0;

ro_m_axi_arsize <= 'd0;

ro_m_axi_arburst <= 'd0;

ro_m_axi_arlock <= 'd0;

ro_m_axi_arcache <= 'd0;

ro_m_axi_arprot <= 'd0;

ro_m_axi_arqos <= 'd0;

ro_m_axi_arvalid <= 'd0;

end else if(r_st_current == P_ST_READ && r_st_cnt == 0) begin

ro_m_axi_arid <= 'd0;

ro_m_axi_araddr <= 'd0;

ro_m_axi_arlen <= P_LEN - 1;

ro_m_axi_arsize <= 3'b101;

ro_m_axi_arburst <= 'd1;

ro_m_axi_arlock <= 'd0;

ro_m_axi_arcache <= 4'b0010;

ro_m_axi_arprot <= 'd0;

ro_m_axi_arqos <= 'd0;

ro_m_axi_arvalid <= 'd1;

end else begin

ro_m_axi_arid <= ro_m_axi_arid ;

ro_m_axi_araddr <= ro_m_axi_araddr ;

ro_m_axi_arlen <= ro_m_axi_arlen ;

ro_m_axi_arsize <= ro_m_axi_arsize ;

ro_m_axi_arburst <= ro_m_axi_arburst;

ro_m_axi_arlock <= ro_m_axi_arlock ;

ro_m_axi_arcache <= ro_m_axi_arcache;

ro_m_axi_arprot <= ro_m_axi_arprot ;

ro_m_axi_arqos <= ro_m_axi_arqos ;

ro_m_axi_arvalid <= ro_m_axi_arvalid;

end

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

ro_m_axi_rready <= 'd0;

else if(r_read_cnt == P_LEN - 1 && w_r_act)

ro_m_axi_rready <= 'd0;

else if(w_ar_act)

ro_m_axi_rready <= 'd1;

else

ro_m_axi_rready <= ro_m_axi_rready;

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst) begin

ri_m_axi_rid <= 'd0;

ri_m_axi_rdata <= 'd0;

ri_m_axi_rresp <= 'd0;

ri_m_axi_rlast <= 'd0;

ri_m_axi_rvalid <= 'd0;

end else begin

ri_m_axi_rid <= m_axi_rid ;

ri_m_axi_rdata <= m_axi_rdata ;

ri_m_axi_rresp <= m_axi_rresp ;

ri_m_axi_rlast <= m_axi_rlast ;

ri_m_axi_rvalid <= m_axi_rvalid;

end

end

always@(posedge i_clk,posedge i_rst)

begin

if(i_rst)

r_read_cnt <= 'd0;

else if(r_read_cnt == P_LEN - 1 && w_r_act)

r_read_cnt <= 'd0;

else if(w_r_act)

r_read_cnt <= r_read_cnt + 1;

else

r_read_cnt <= r_read_cnt;

end

endmodule